#### A 2.8V Multibit Complex Bandpass Delta-Sigma AD Modulator in 0.18µm CMOS

<u>H. San,</u> Y. Jingu, H. Wada, H. Hagiwara, A. Hayakawa, H. Kobayashi, M. Hotta<sup>2</sup>

Gunma University

Musashi Institute of Technology

#### **Motivation**

# Low power ADC in low-IF receiver targeted for wireless system.

#### Complex bandpass Delta-Sigma AD modulator

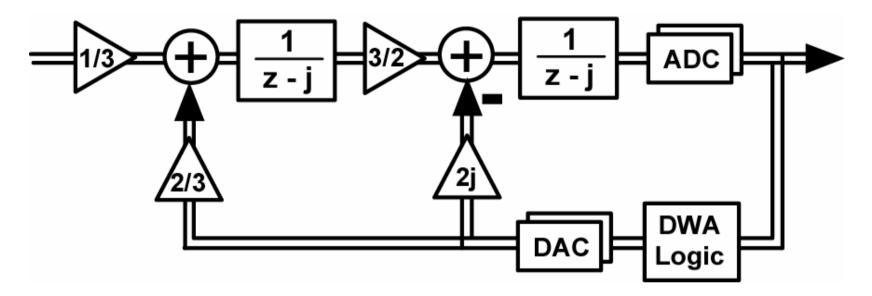

#### **Proposed Architecture**

- 2<sup>nd</sup>-order modulator

- New complex bandpass filter

- Multi-bit ADCs/DACs

- Complex DWA algorithm

## **Complex BPDSM with Low-power**

- 2<sup>nd</sup> order modulator

- -Less hardware, low power

- 9-level ADCs/DACs

- -Stability improvement

- -Low quantization error

- -Power reduction of amplifiers

- Problems

- -I,Q mismatch >I,Q Dynamic Matching

- -Nonlinearities of multibit DAC ->>> DWA

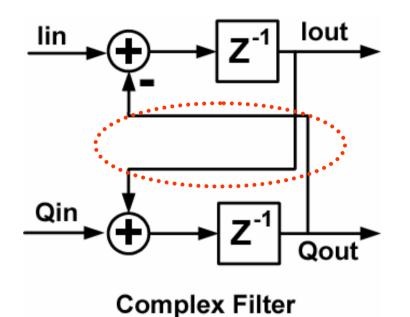

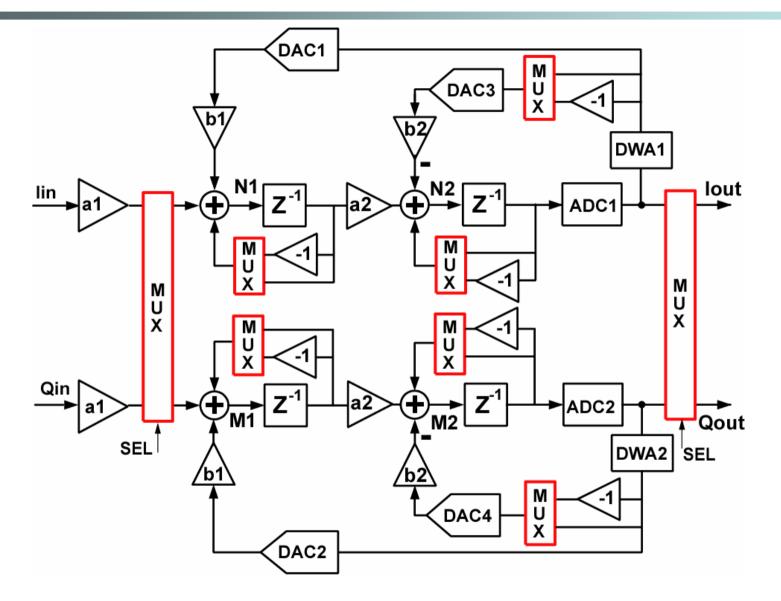

#### I,Q Dynamic Matching of Complex Filter

Conventional complex filter I &Q crossing paths

$$H_1(z) = \frac{1}{z - j}$$

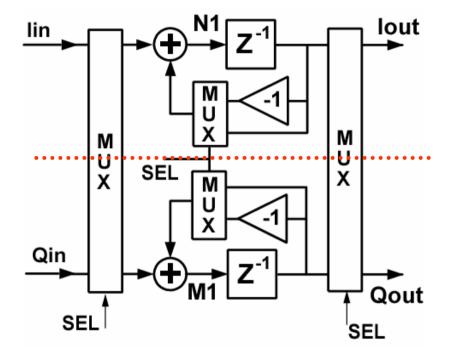

Proposed complex filter Upper, lower separated paths

- I,Q mismatch reduction.

- Layout simplification.

**ASP-DAC 2007**

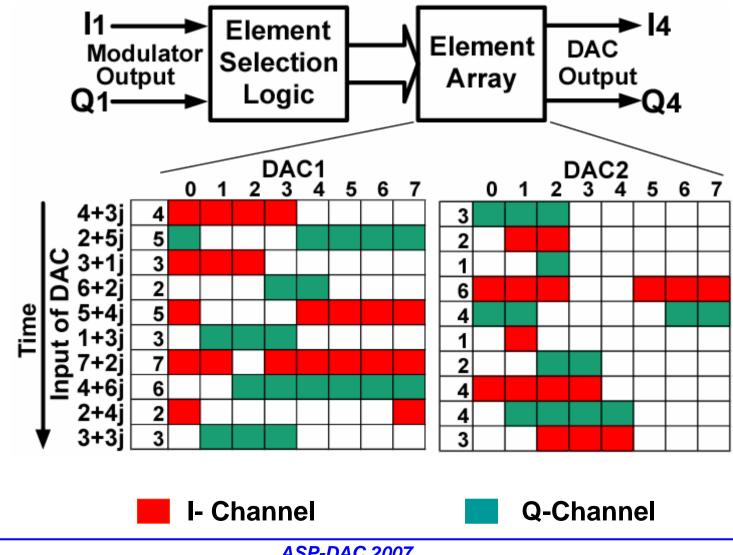

## **Selected segment in Complex DWA**

#### **Proposed Structure**

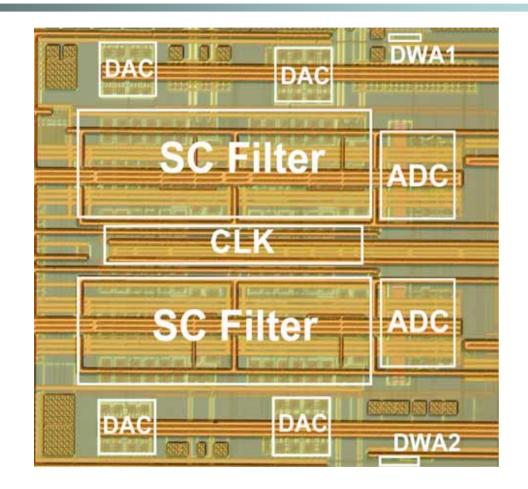

## **Chip Implementation**

- 1P6M 0.18µm CMOS Process

- Core size 1.4 \*1.3mm<sup>2</sup>.

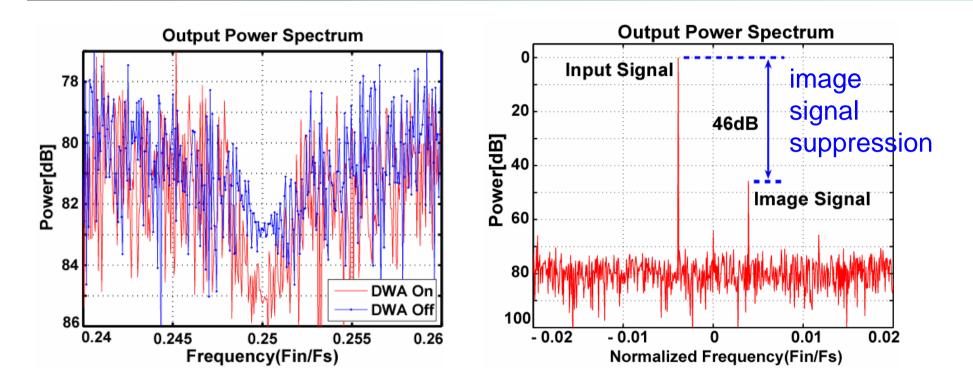

## **Measured Results**

| Supply voltage     | 2.8V              |

|--------------------|-------------------|

| Sampling Frequency | 20MHz             |

| SNDR               | 64.5dB @ BW=78kHz |

| Power consumption  | 28.4mw            |

## Conclusion

• A 2<sup>nd</sup>-order multi-bit complex bandpass delta-sigma modulator

- I,Q mismatch reduction

- Layout simplification

- Complex DWA

- Suppression of multibit DACs nonlinearities

- Chip measurements demonstrated these