ASPDAC'07 Keynote Address II 9am – 10am Jan.25, 2007

#### Meeting with the forthcoming IC design – The era of power, variability and NRE explosion and a bit of the future –

# - Solving issues of IC's by 3D-stacking –

Prof. Takayasu Sakurai

Center for Collaborative Research, and Institute of Industrial Science, University of Tokyo E-mail:tsakurai@iis.u-tokyo.ac.jp

#### Moore's law continues as a backbone but...

#### **Favorable effects**

| Size           | x1/2      |

|----------------|-----------|

| Voltage        | x1/2      |

| Electric Field | <b>x1</b> |

| Speed          | <b>x3</b> |

| Cost           | x1/4      |

# Unfavorable effectsPower densityx1.6RC delay/Tr. delayx3.2Current densityx1.6Voltage noisex3.2Design complexityx4

#### **Three explosions threat Moore's law**

- Explosion of power

- Explosion of integrity attackers

- Explosion of complexity

- ➔ Explosion of NRE\*

\*) Non-Recurring Engineering Cost

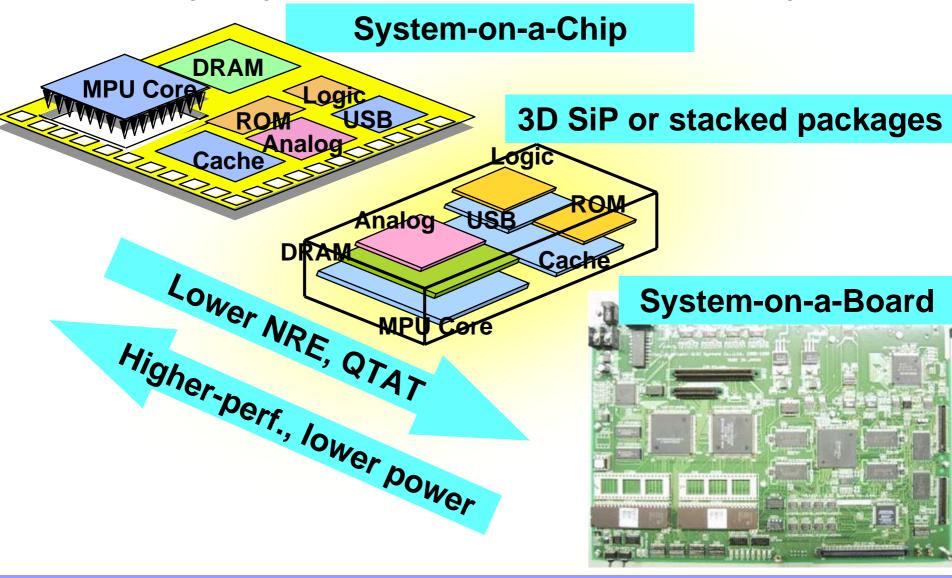

#### **3D Stacking for solving issues**

#### Silicon chips stacking

#### for lower power & lower NRE

# Organic sheets stacking for newer applications

#### With design tool implications

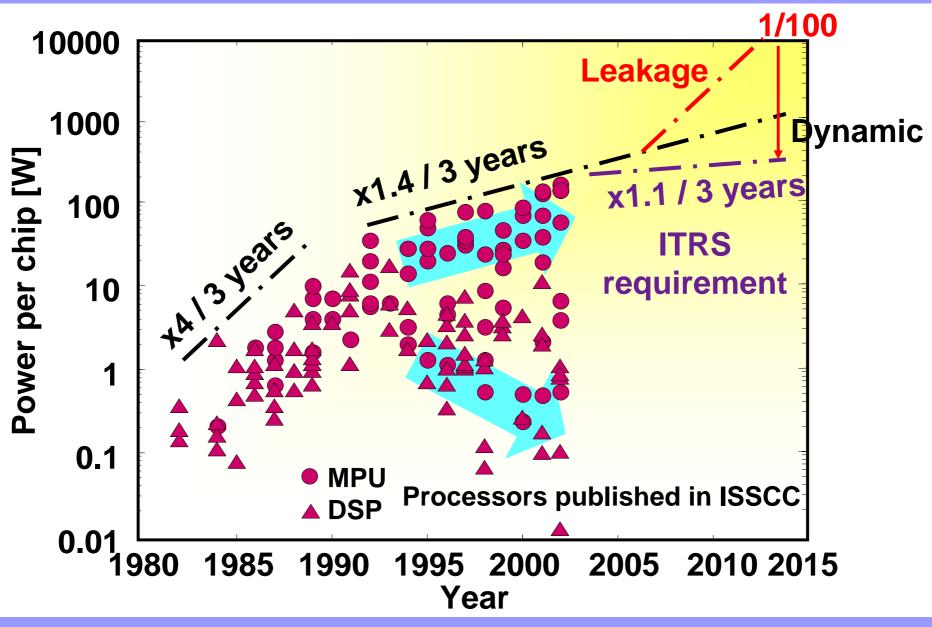

#### Power is a stumbling block to Moore's law

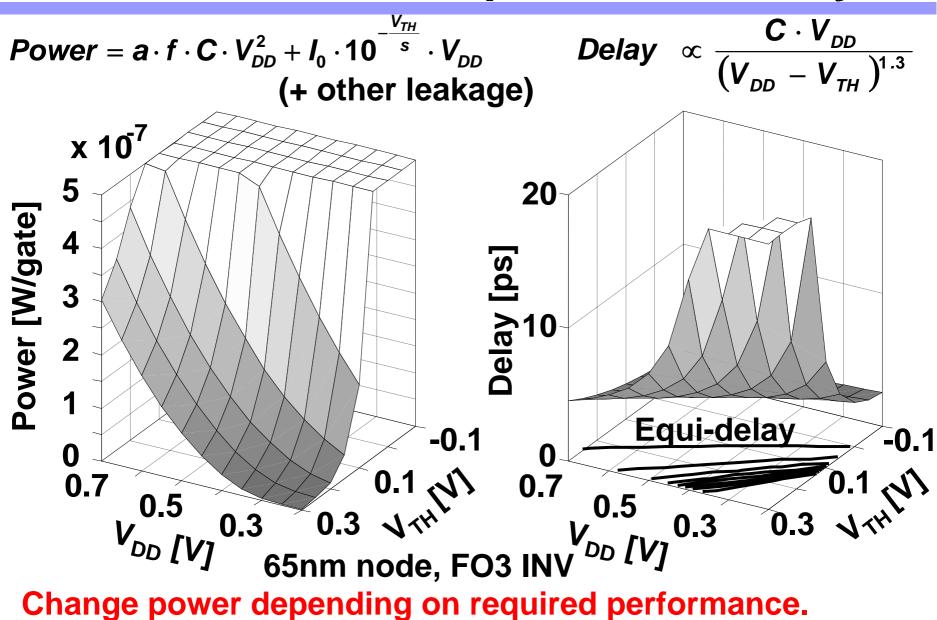

#### **Trade-off between power and delay**

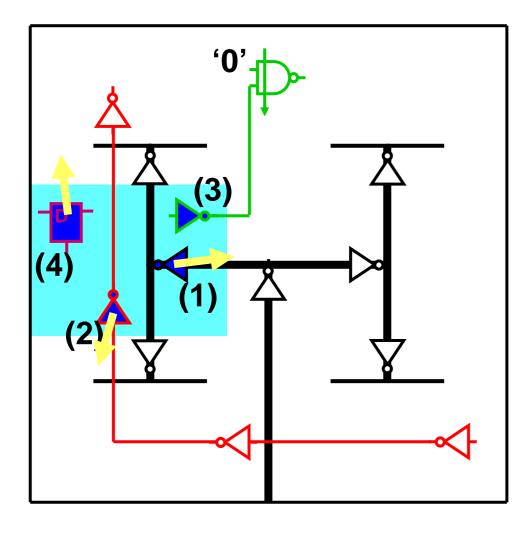

# **Example of power-aware design**

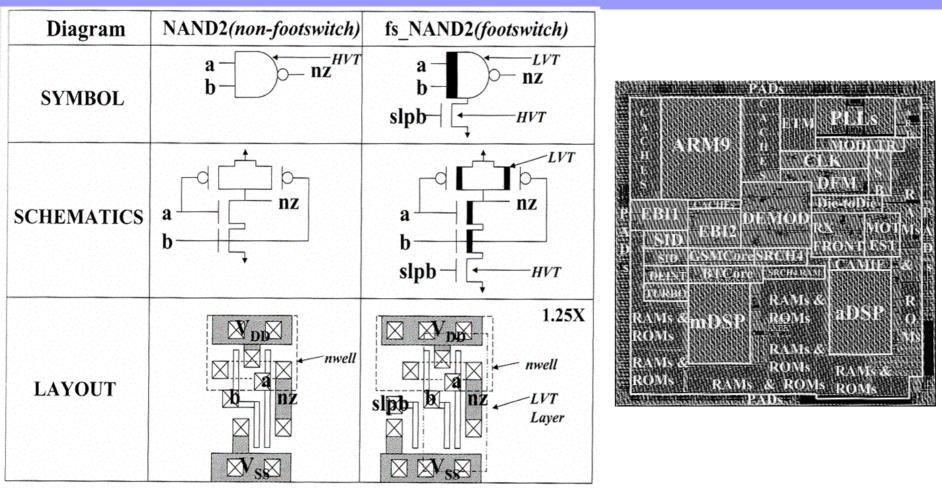

Multi-V<sub>DD</sub>: Seven V<sub>DD</sub>'s Dual-V<sub>TH</sub>: Two V<sub>TH</sub>'s for PMOS and NMOS each Power gating: Selective MTCMOS reduced standby to 1/3~1/4. G. Uvieghara, et al., "A Highly-Integrated 3G CDMA2000 1X Cellular-Baseband Chip with GSM/AMPS/GPS/Bluetooth/Multimedia Capabilities and ZIF RF Support," ISSCC paper#23.3, Feb. 2004

GSM/AMPS/GPS/Bluetooth/Multimedia Capabilities and ZIF RF Support, "ISSCC paper#23.3, Feb. 2004. T.Sakurai

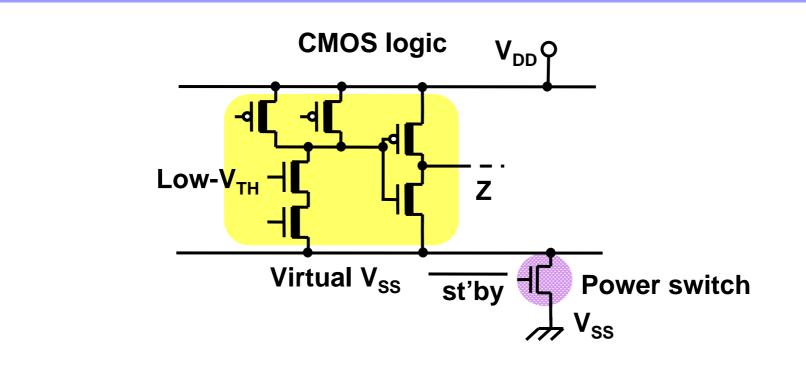

## Power-gating to cut-off V<sub>DD</sub> of inactive blocks is getting a major leakageaware design style and seems easy but...

#### **Pitfalls in power-gating**

- 1) Clock buffers

- 2) Repeaters

- 3) Gates receiving power-gated signals

- 4) Registers will lose stored info

- 5) Other common blocks like analog and sleep signal generator

**Power-gated block**

Big and rather slow (µs-order) noise on power supply line when switched off and on.

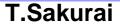

#### **Tool implications of power-gating**

- 1) High-level description of power-gating

- 2) Power estimation tool

- 3) Sizing of power switch

- 4) Delay estimation under the effect of the power switch

- 5) Automatic generation of sleep signal

- 6) Layout level considerations

- 7) Power line integrity at sleep and wake-up

#### New tools for each new design approach

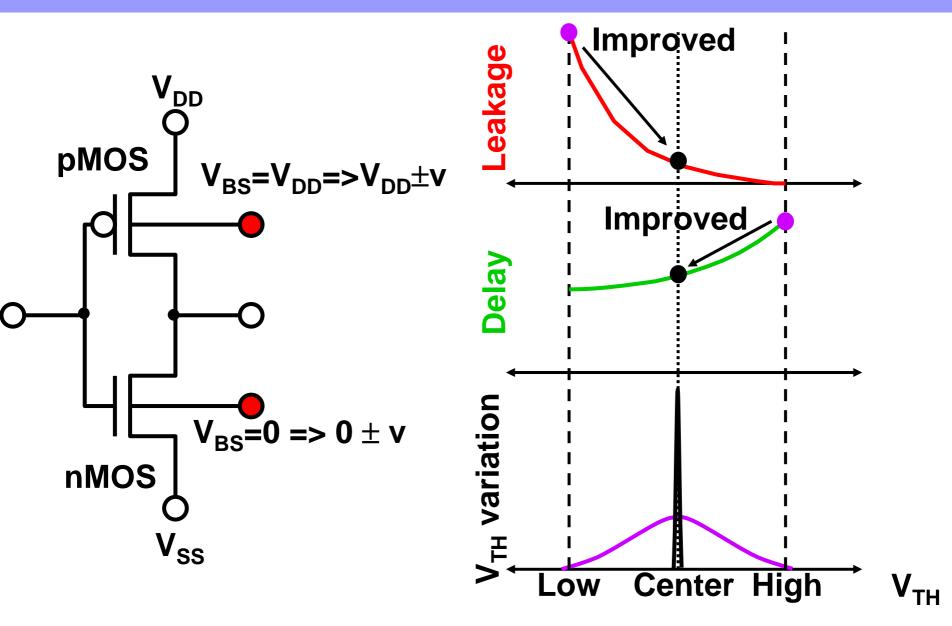

# Adaptive $V_{DD} \& V_{TH}$ control for lower power with variability

#### Adaptive voltage for variation control

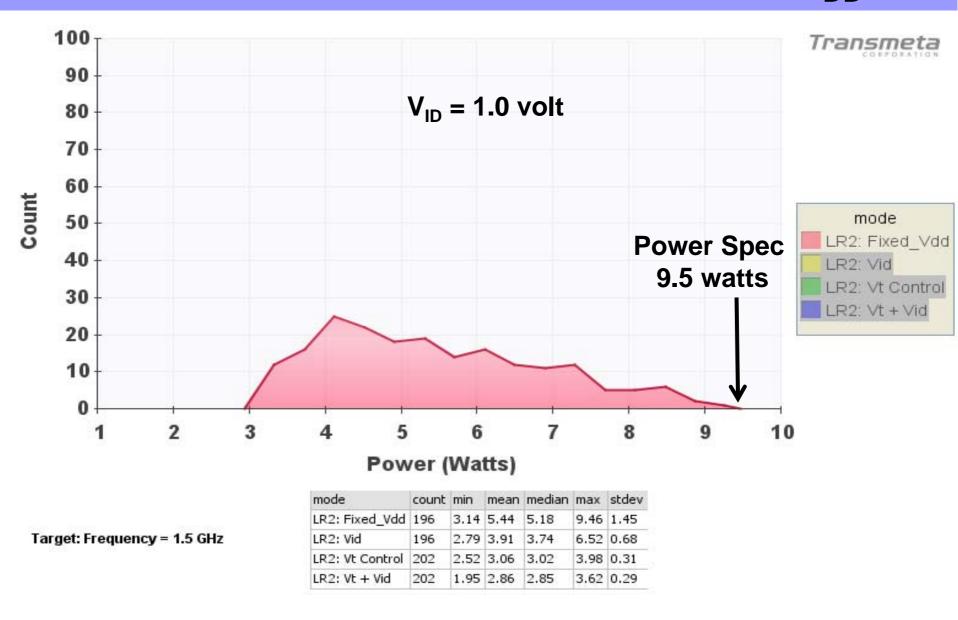

#### **Transmeta Efficeon 1.5 GHz Fixed V**<sub>DD</sub>

Courtesy: Transmeta Corp.

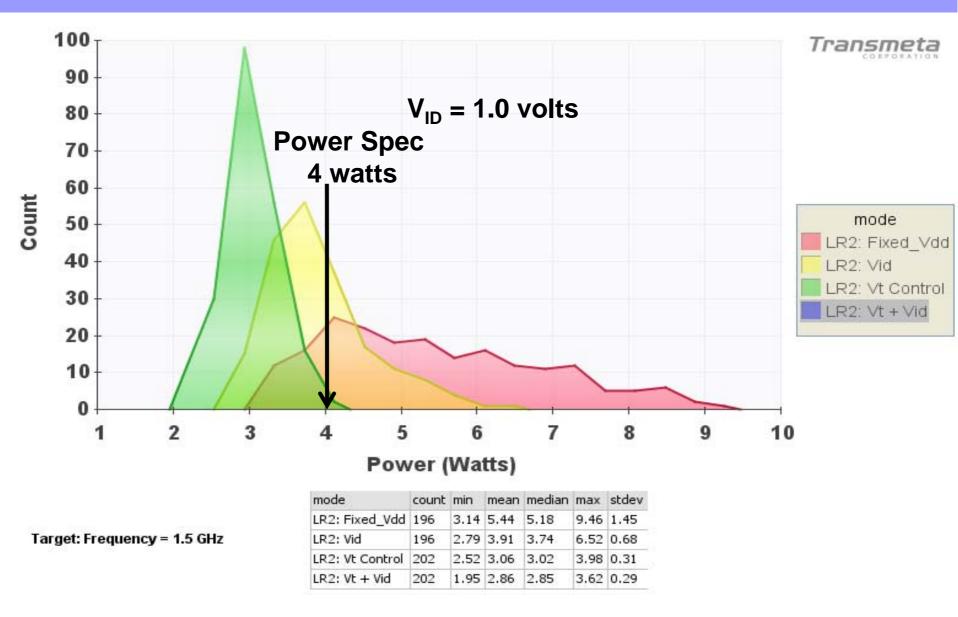

#### **Transmeta Efficeon 1.5 GHz with Voltage ID**

**T.Sakurai**

Courtesy: Transmeta Corp.

#### 1.5 GHz with $V_{TH}$ Control and Fixed $V_{DD}$

Courtesy: Transmeta Corp.

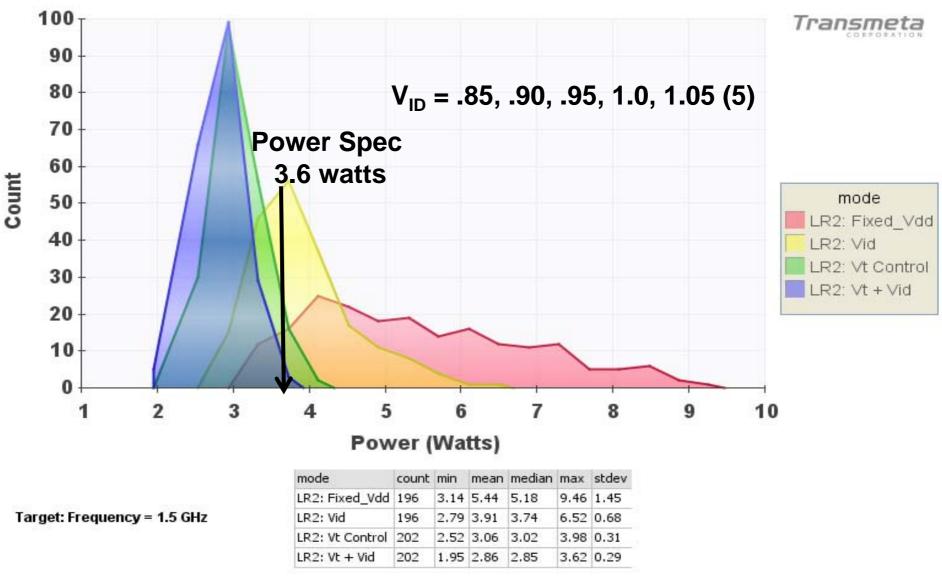

#### 1.5 GHz with $V_{TH}$ and $V_{DD}$ Control

#### Statistical simulation tools with $V_{DD}$ and $V_{TH}$ adjustment

Courtesy: Transmeta Corp.

**History and perspective of low-power VLSI**

Once upon a time on a peaceful chip of VLSI before the notorious power war ...

We were using single  $V_{\text{DD}}$  and single  $V_{\text{TH}}$  for an entire chip.

Then, the power war began and we started using multiple  $V_{TH}$  and  $V_{DD}$  depending on the location on a chip.

Still, the power war gets severer and we started to vary  $V_{TH}$  and  $V_{DD}$  in time adaptively.

In finer granularity in time and space ... with a help from circuit and software.

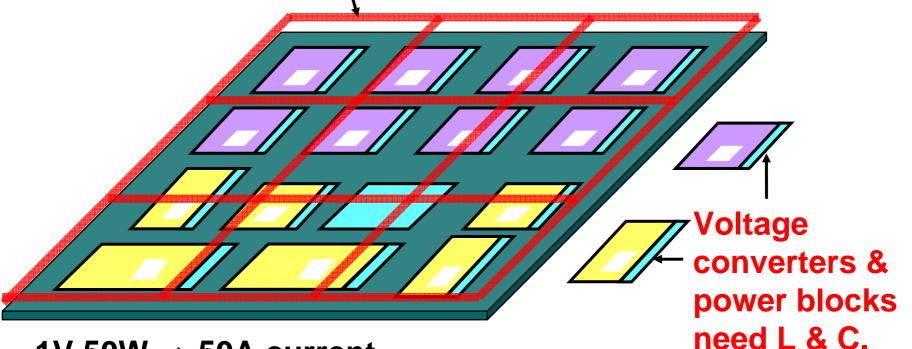

#### **Future power-aware VLSI**

- High-voltage V<sub>DD</sub> distribution to lower noise issues

- Distributed voltage conv. for fine-grain adaptive V<sub>DD</sub> & V<sub>TH</sub>

**Power-grid**

1V 50W  $\rightarrow$  50A current 5% noise  $\rightarrow$  0.05V noise  $\rightarrow$  1m $\Omega$  sheet R  $\rightarrow$  15µm thick Cu Thick interconnects on interposer, package or something else

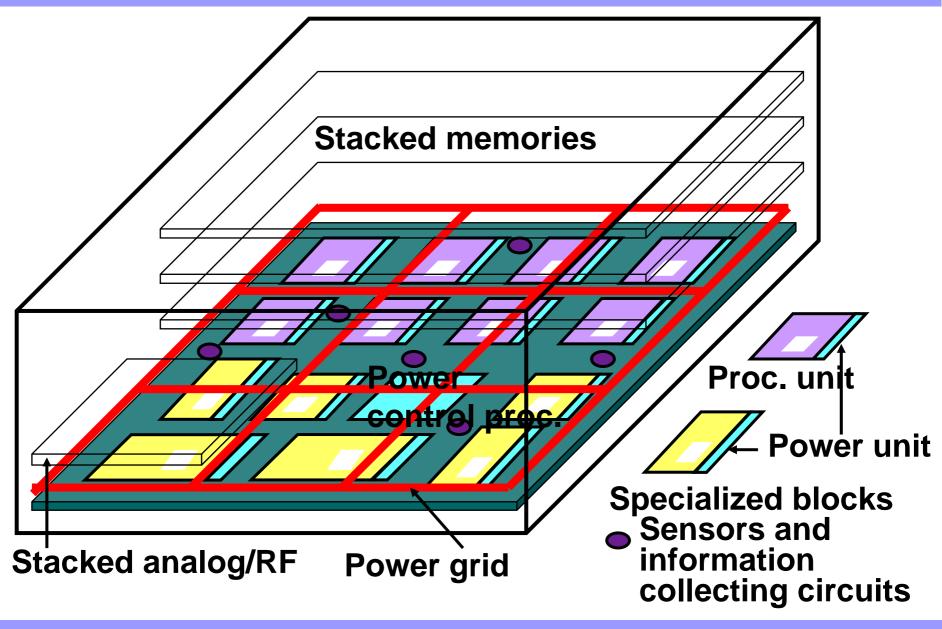

#### Further power-awareness by 3D stacking

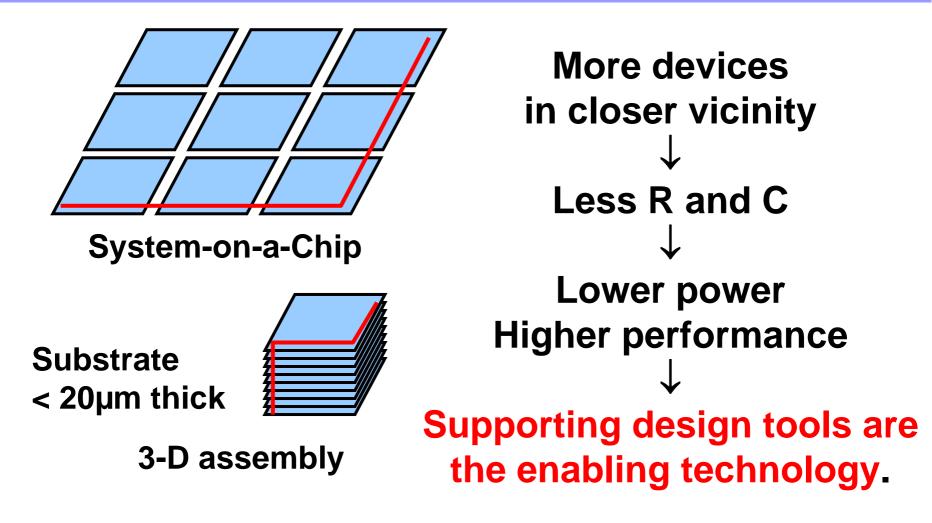

#### 3-D is good for low-power and high-perf.

System simulation & synthesis with 3D, simulation with electro-magnetic interaction

#### **Three explosions threat Moore's law**

- Explosion of power

- Explosion of integrity attackers

- Explosion of complexity

# ➔ Explosion of NRE\*

#### \*) Non-Recurring Engineering Cost

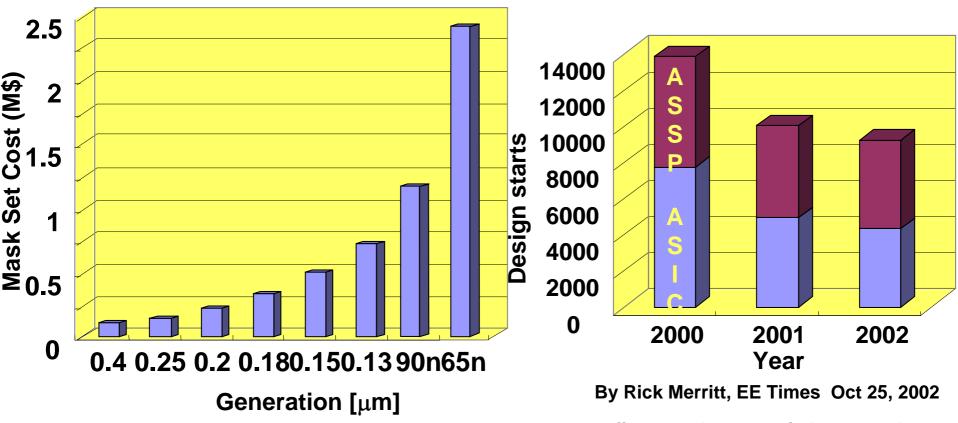

#### **Exploding NRE (Non-Recurring Eng. Cost)**

Source: Rahul Goyal, Intel –Nov 2001 SEMI Mtg

http://www.eetimes.com/printableArticle ?doc\_id=OEG20021025S0052

- NRE for a SoC is getting \$5M~10M and without over \$20M sales it is difficult to make a SoC. by Bryan Lewis, Gartner Dataquest

- Number of design starts is declining from 1997.

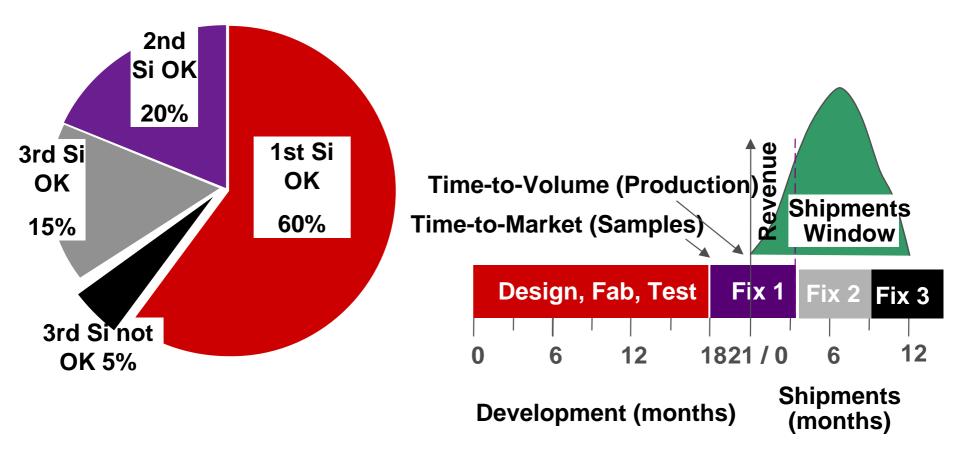

# **Development is also risky**

Dr. Kurt Keutzer, Ahmed Jerraya

Special Session: "How do you design a 10M gate ASIC?" 2002 Design Automation Conference Dr. Fumiyasu Hirose, Cadence Japan

# **CANDE meeting 2005**

The final 5-year predictions (to be reviewed in 2010) were:

- 1) IC-Package CAD will be a part of standard design flow

- 2) India and China will have more EDA startups than U.S.

- 3) Analog Designers will still resist high-level models and languages

- 4) A complete Open Source RTL-GDS tool flow will exist

- 5) Nearly all EDA tools will take advantage of multiprocessors

- 6) Fewer than 200 commercial chips released in 45 nm technology

- 7) No practical nanotech computing products

- 8) SPICE-type simulators will still be the workhorse of analog designs

- 9) Moore's law will be dead

- 10) System in Package will boom

http://www.ics.uci.edu/~rgupta/cande/

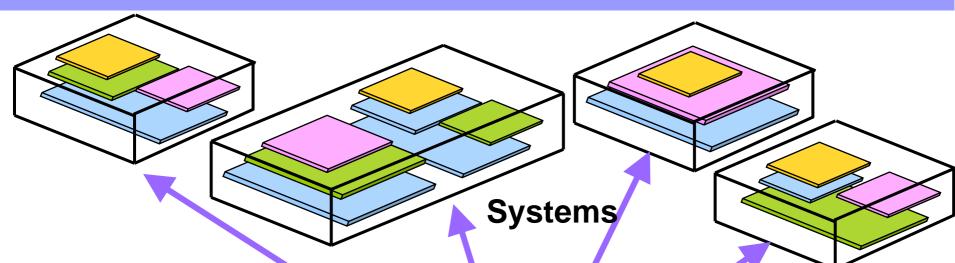

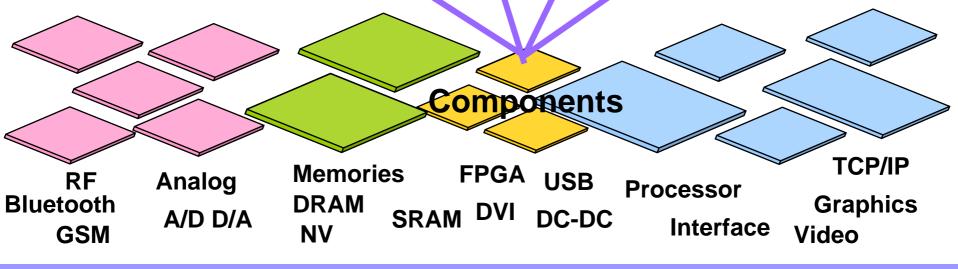

# 3D stacking of chips/packages will be an assembly style suitable for low-NRE systems

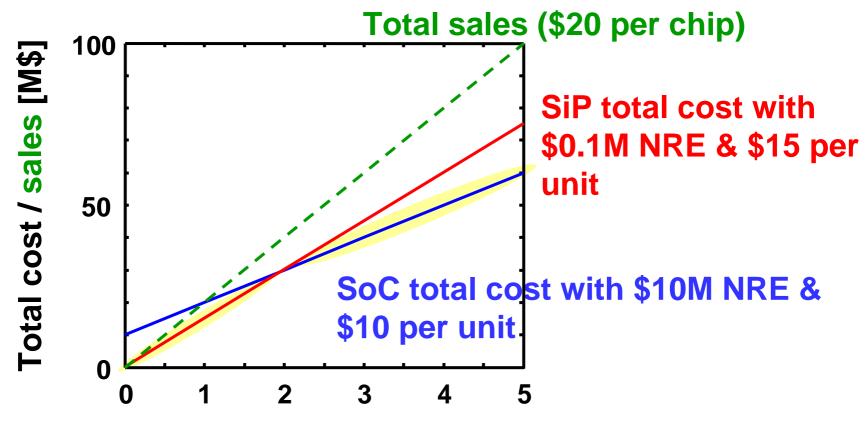

## **Amortizing NRE by volume production**

#### "Mix & Match" increases number of chips per development.

#### **Mixed business model**

Number of chips sold [million units]

Design tools from high level to physical level are needed.

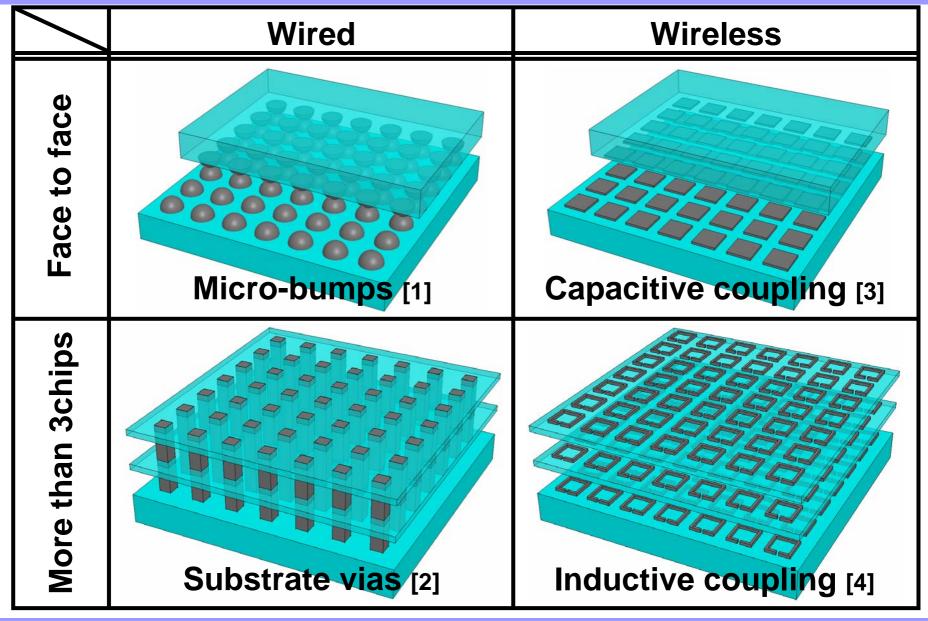

#### Interconnections for new 3D SiP's

[1] T.Ezaki [2] J.Burns [3] K.Kanda [4] D.Mizoguchi, (ISSCC'04, '01, '03, '04)

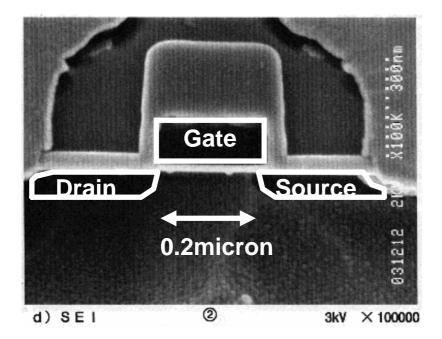

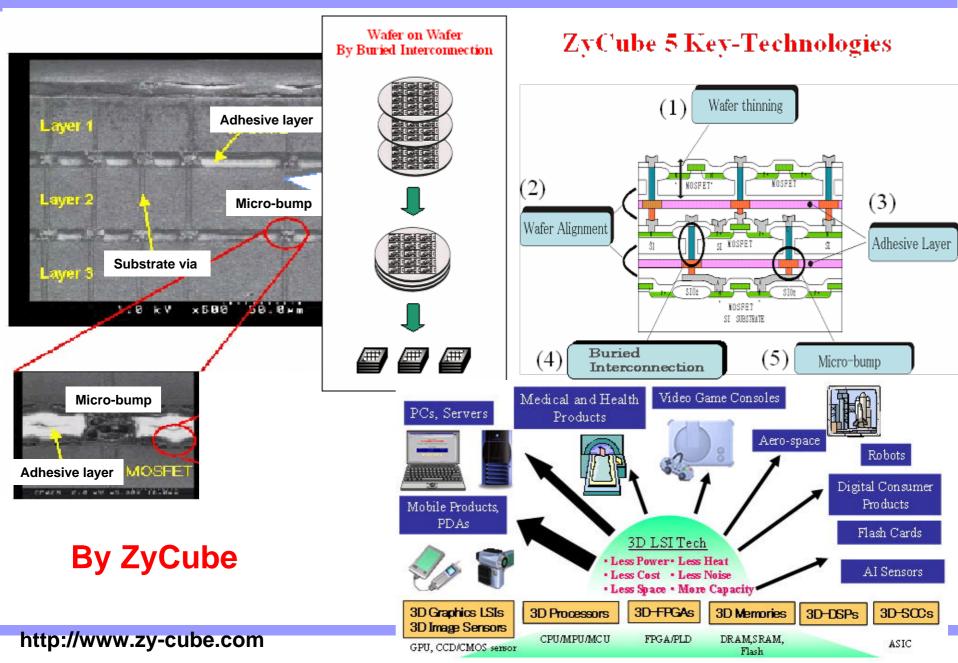

#### Through substrate via (TSV)

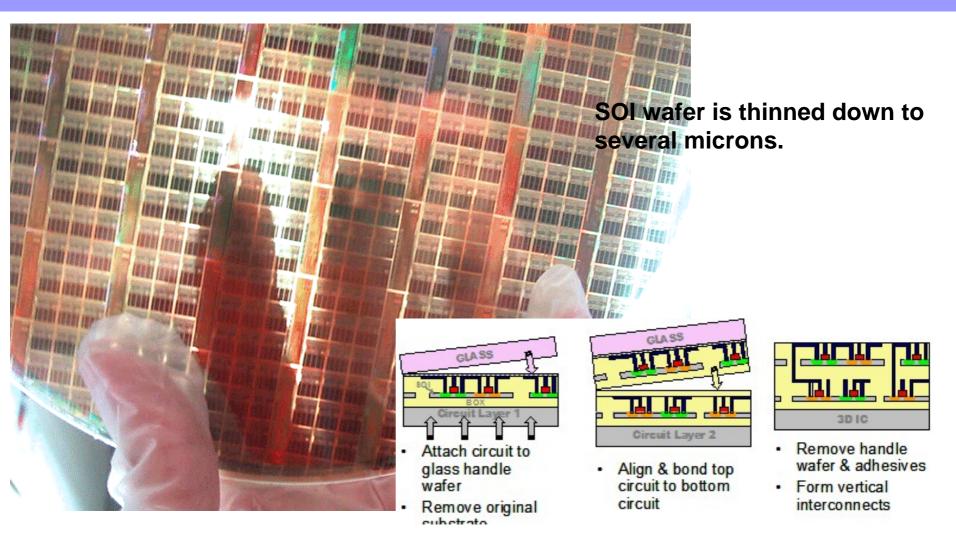

## 3D wafer stacking for high performance

Via size is 0.2 microns diameter at the top, and 0.14 microns at the bottom.

Courtesy of Kerry Bernstein, IBM T.J. Watson Research Center

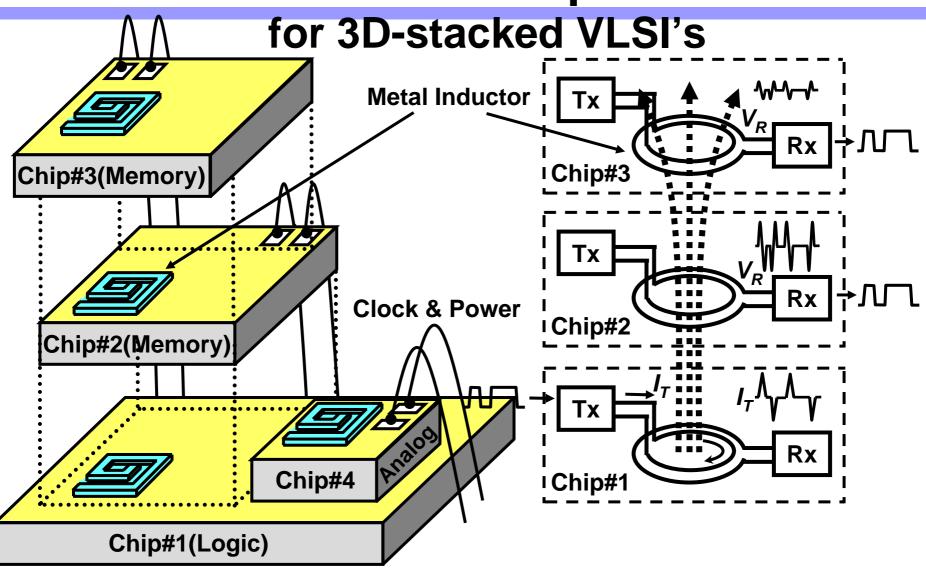

#### Inductive wireless superconnect

D. Mizoguchi, Y. Yusof, N. Miura, T. Sakurai, T. Kuroda, "A 1.2Gb/s/pin Wireless Superconnectbased on Inductive Interchip Signaling (IIS), "ISSCC'04, pp. 142-143, Feb. 2004. N. Miura, D. Mizoguchi, Y. B. Yusof, T. Sakurai, and T. Kuroda, "Analysis and Design of Transceiver Circuit and Inductor Layout for Inductive Inter-chip Wireless Superconnect," *Symp. on VLSI Circuits*, pp. 246-249 June 2004.

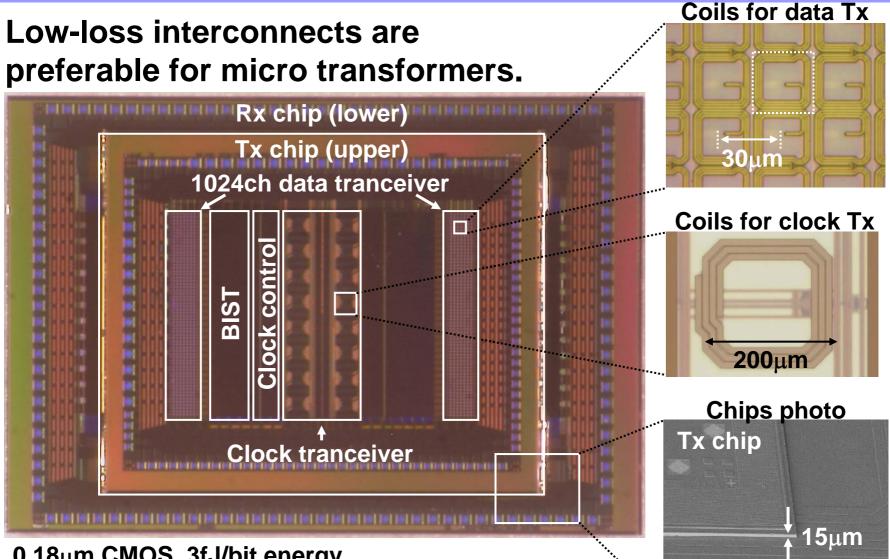

# 1Tbps inter-chip wireless by 30µm coils

#### 0.18µm CMOS, 3fJ/bit energy

N.Miura, D.Mizoguchi, M.Inoue, K.Niitsu, Y.Nakagawa, M.Tago, M.Fukaishi, T. Sakurai, T. Kuroda, "A 1Tb/s 3W Inductive-Coupling Transceiver for Inter-Chip Clock and Data Link," ISSCC'06, Paper#23.4, Feb. 2006.

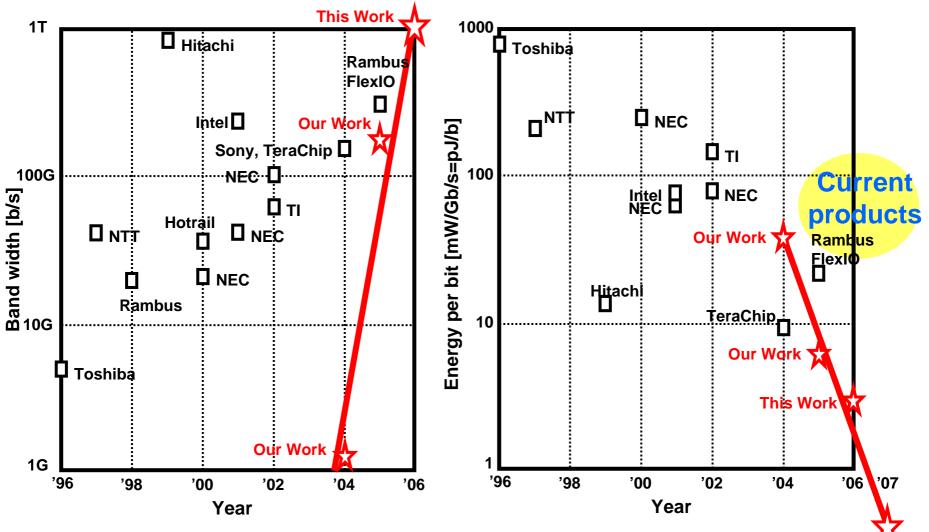

#### Inductively-coupled inter-chip communication

#### **Circuits and electro-magnetism hybrid simulation.**

N.Miura, H.Ishikuro, T.Sakurai, T.Kuroda, "A 0.14pJ/b Inductive-Coupling Inter-Chip Data Transceiver with Digitally-Controlled Precise Pulse Shaping," Paper#20.2, ISSCC, Feb.2007.

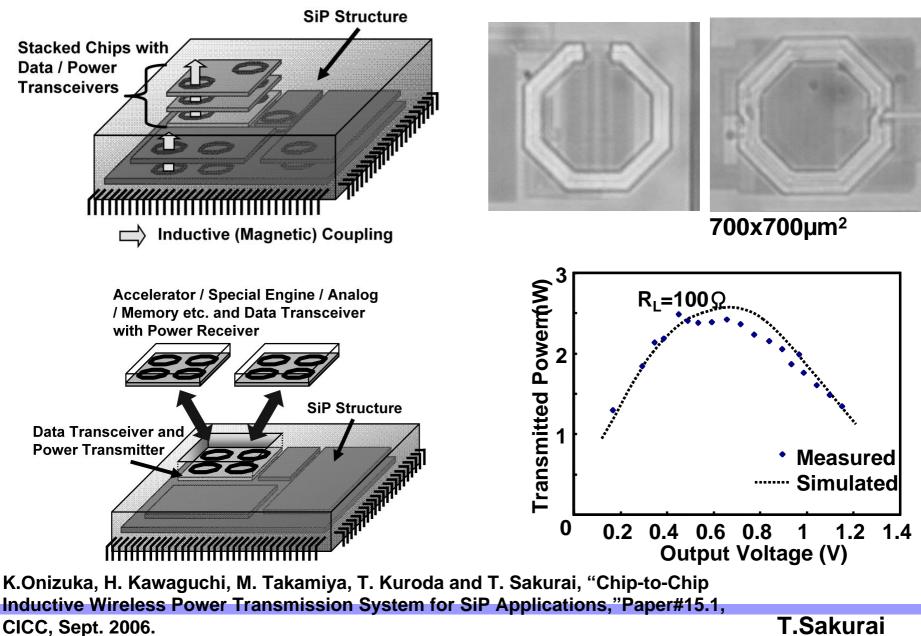

#### **Even wireless power transmission**

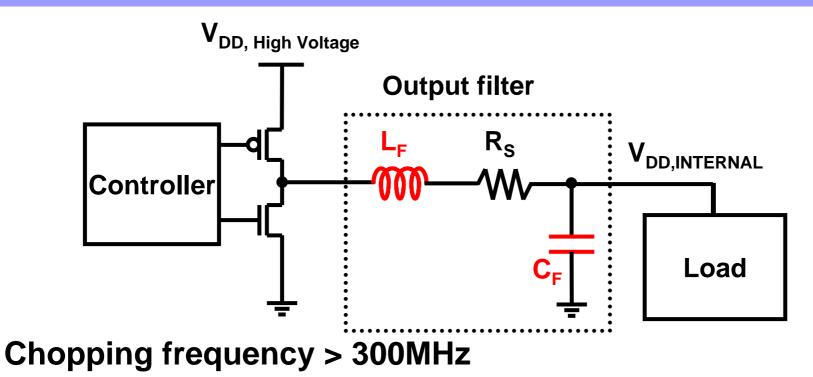

#### **On-chip distributed DC-DC converter**

Need good low-resistive L & high-capacitive C. They are also needed for low-power RF circuits.

➔ Si with L and C

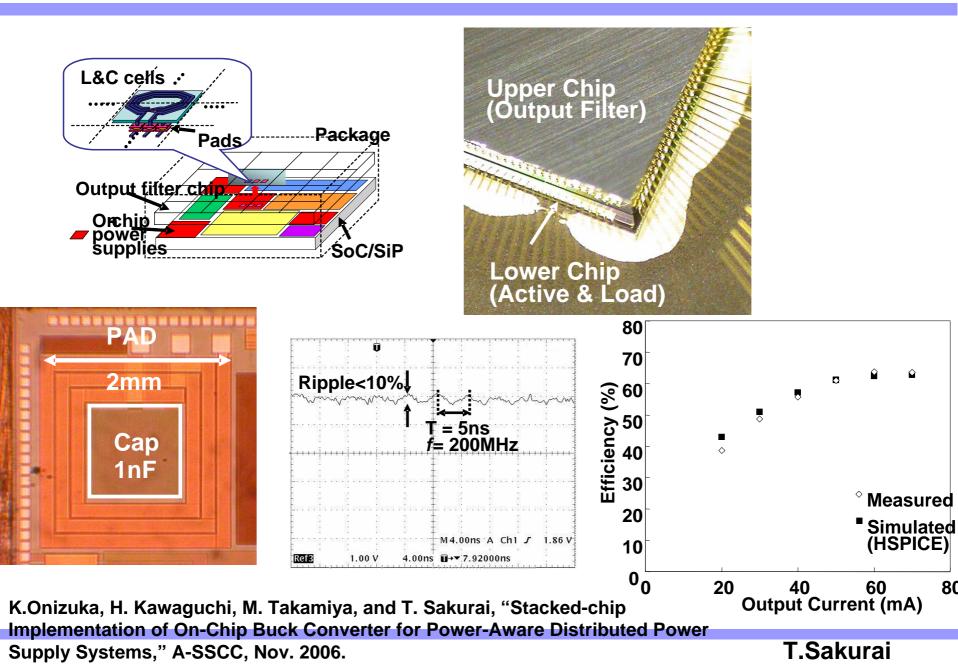

#### **Distributed DC-DC converter by 3D stacking**

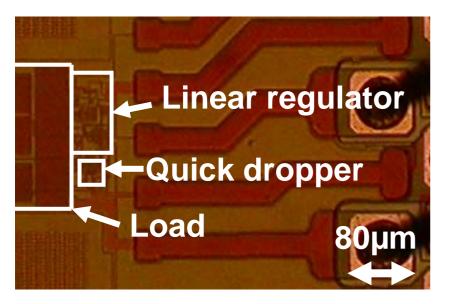

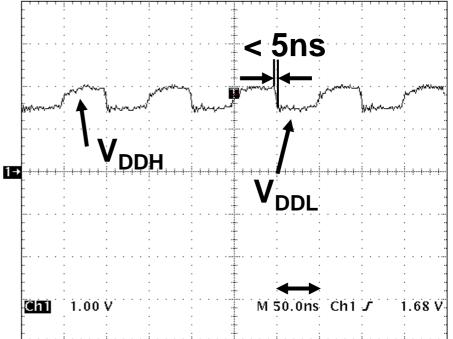

## **5ns transition on-chip power supply**

#### Measurement

#### For 25k-gates equivalent load @ 0.18µm CMOS

#### **Transition time smaller than 5ns**

K.Onizuka and T.Sakurai, "VDD-Hopping Accelerator for On-Chip Power Supplies Achieving Nano-Second Order Transient Time," A-SSCC'05, Paper#6.1, Nov. 2005.

#### **3D Stacking for solving issues**

#### Silicon chips stacking

#### for lower power & lower NRE

Organic sheets stacking for newer applications

#### With design tool implications

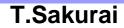

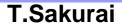

#### New electronics targets physical space

Original drawing: Courtesy of Prof. Morikawa, Univ. of Tokyo

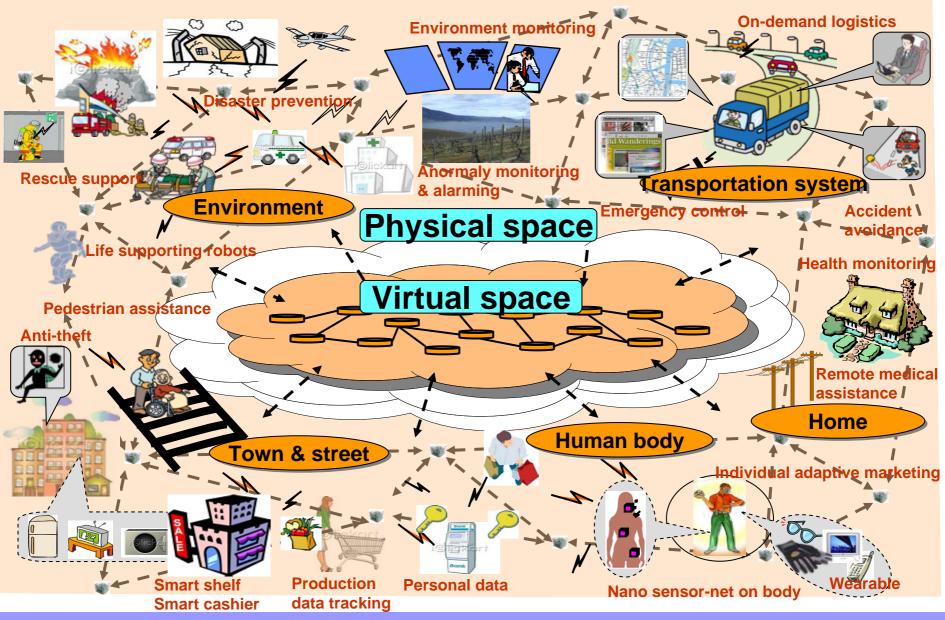

#### Increasing VLSI penetration into people's life

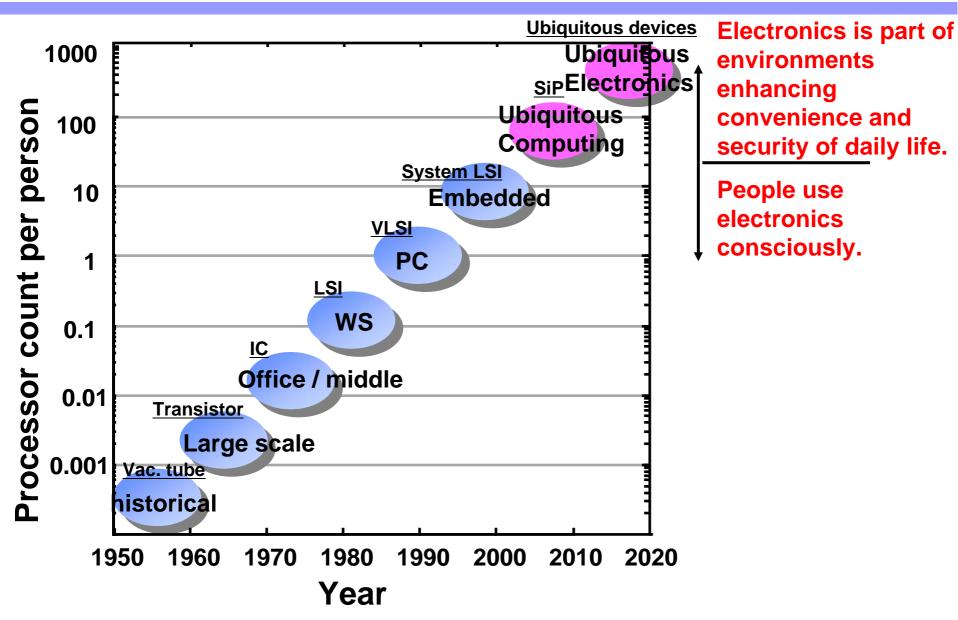

### **Expenditure distribution of Japanese household**

## Ubiquitous electronics is required to provide physical applications.

# Required innovations for ubiquitous electronics

Huge number of devices

- → Extremely low power (3D SiP)

- →Low cost (3D SiP)

Everywhere

→ Very short distance communication (L & C stacked)

→ Ubiquitous energy source (Large-area electronics)

Interfaces to real-world

- → Sensors & actuators (Large-area electronics)

- Heterogeneous systems (Heterogeneous ICs stack)

Design tool needs for 3D hybrid systems synthesis and simulation

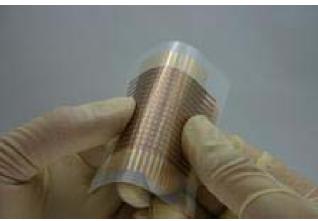

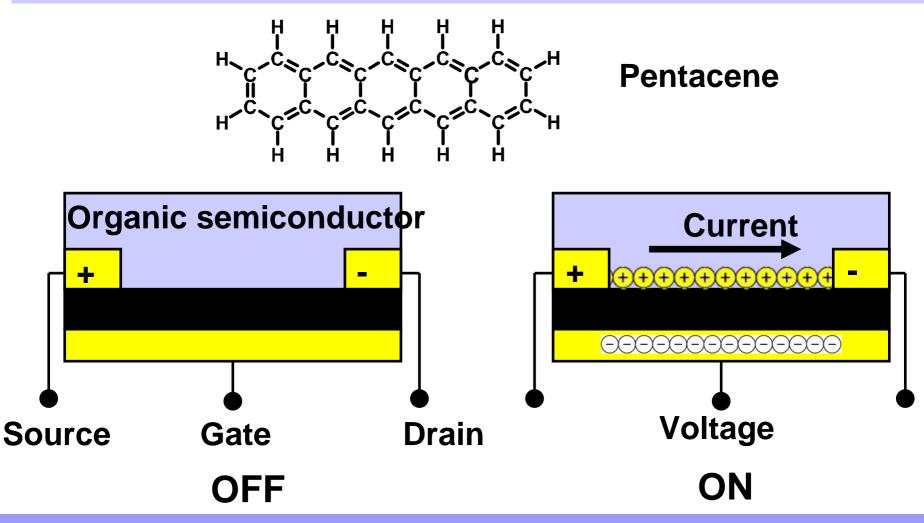

#### **Features of organic IC's**

#### Low-cost manufacturing Mechanical flexibility

Disadvantages

Low speed (<10<sup>-5</sup> of Si VLSI) Low density (<10<sup>-4</sup> of Si VLSI)

#### **Organic electronics**

#### **Printable electronics**

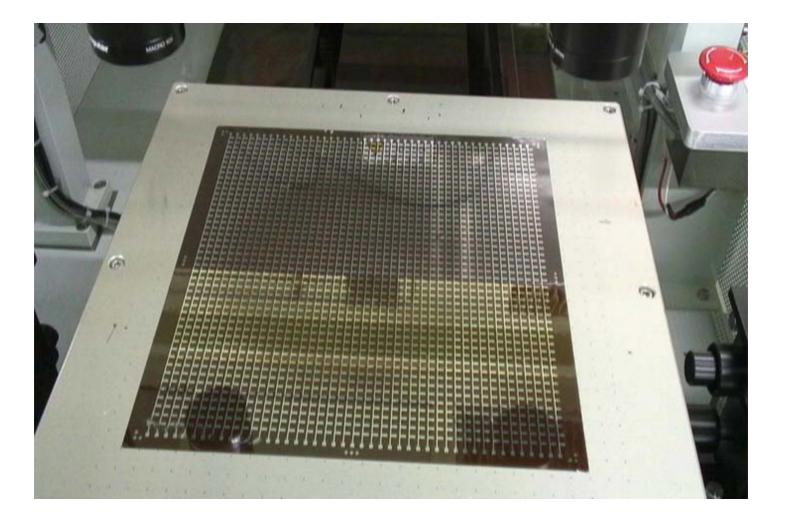

## **Organic transistors**

#### Organic semiconductors: main elements --- C & H Slow but flexible and low-cost manufacturing

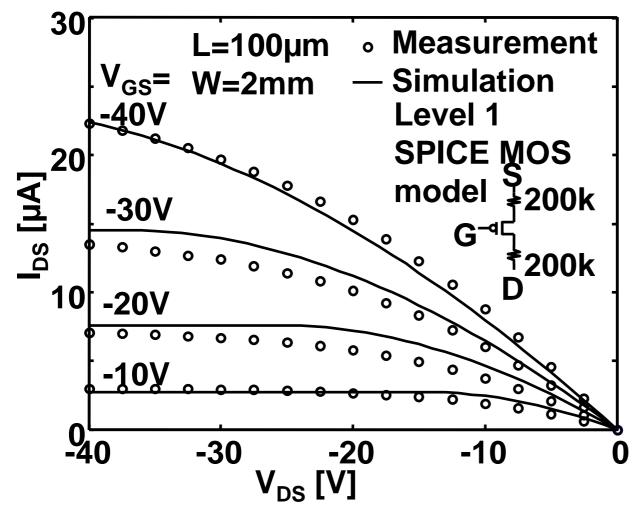

### **SPICE still works**

#### •Match level 1 SPICE MOS model with 200k $\Omega$

Mobility 0.5 ~ 1.4cm<sup>2</sup>/Vs Ion/Ioff >10<sup>6</sup>

#### **Bending proof**

Preferably new model like  $\mu \propto (V_{GS}-V_{TH})^{\gamma}$  (0< $\gamma$ <1)

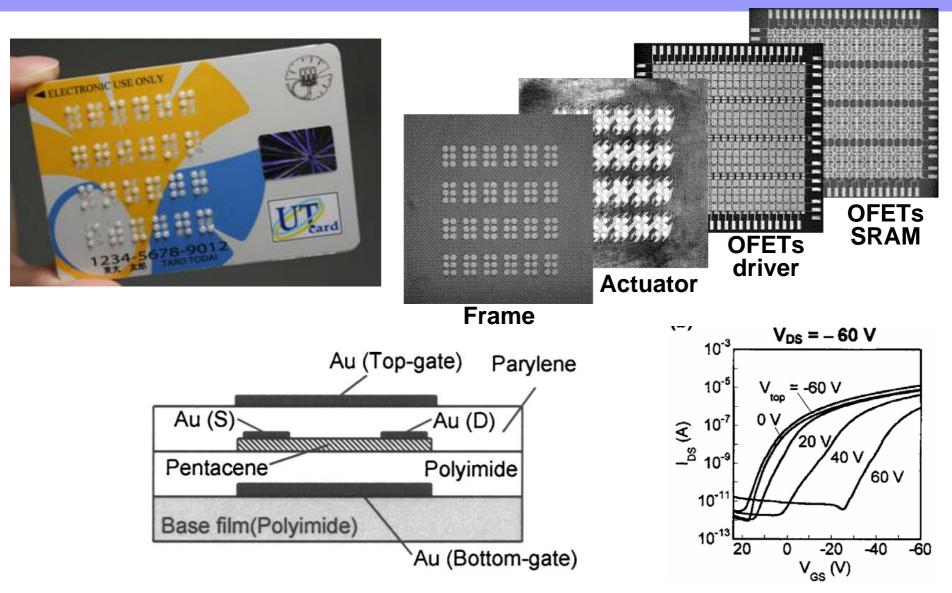

#### Large-area electronics by stacked sheets Slow but low-cost for large-area (Si can't cover)

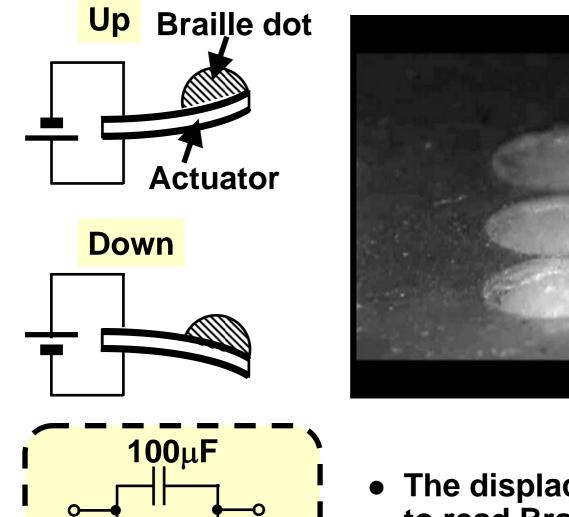

Braille display transmission

## Braille display by organic FETs

Y.Kato, S.Iba, T.Sekitani, Y.Noguchi, K.Hizu, X.Wang, K.Takenoshita, Y.Takamatsu, S.Nakano, K.Fukuda, K.Nakamura, T.Yamaue, M.Doi, K.Asaka, H.Kawaguchi, M.Takamiya, T.Sakurai, and T.Someya, "A Flexible, Lightweight Braille Sheet Display with Plastic Actuators Driven by An Organic Field-Effect Transistor Active Matrix," IEDM'05, Paper #5.1, Dec.2005.

M.Takamiya, T.Sekitani, Y.Kato, H.Kawaguchi, T.Someya, and T.Sakurai, "An Organic FET SRAM for Braille sheet display with back gate to increase the static noise margin," ISSCC'06, Paper #15.4, Feb. 2005.

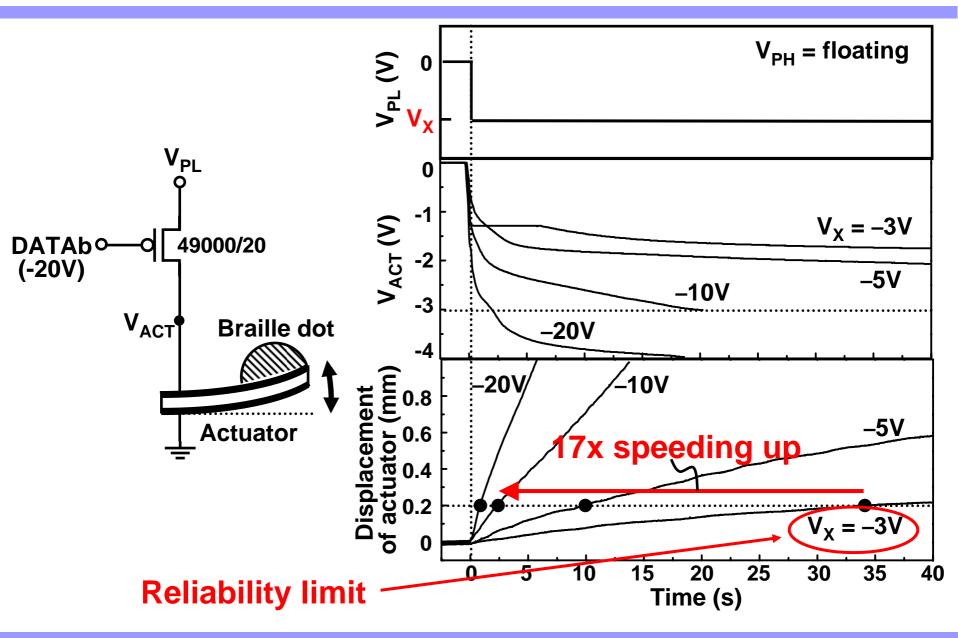

#### **Plastic actuators**

Equivalent circuit

The displacement of the actuators to read Braille is 0.2 mm.

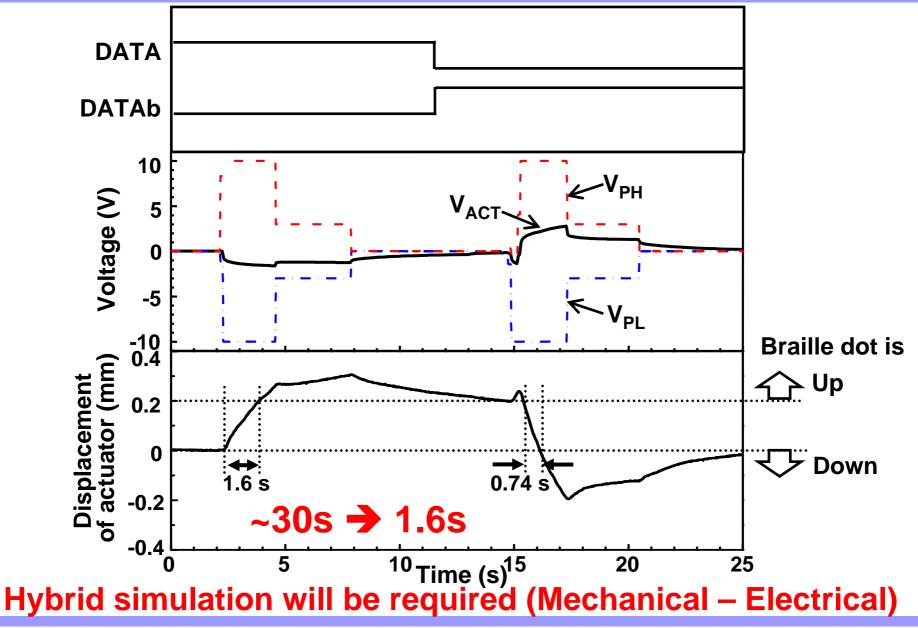

#### Speed up by higher-voltage drive

#### **Overdrive for speed and reliability**

#### Braille sheet display stacking four sheets

M.Takamiya, T.Sekitani, Y.Kato, H.Kawaguchi, T.Someya, and T. Sakurai, "An Organic FET SRAM for Braille Sheet Display with Back Gate to Increase Static Noise Margin," ISSCC'06, Paper#15.4, Feb. 2006.

#### **Braille reading test**

#### All of 4 blind subjects can read our Braille correctly.

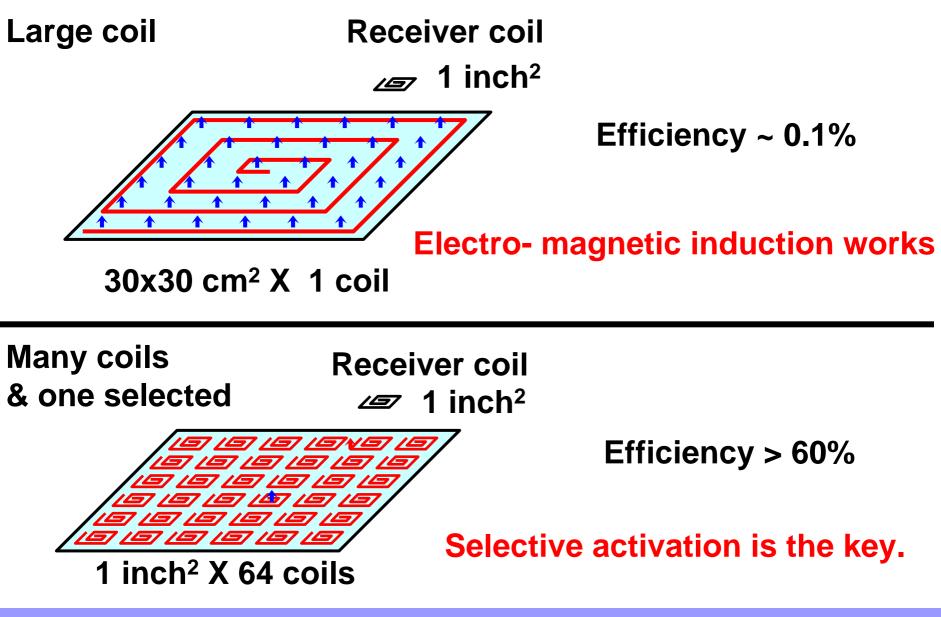

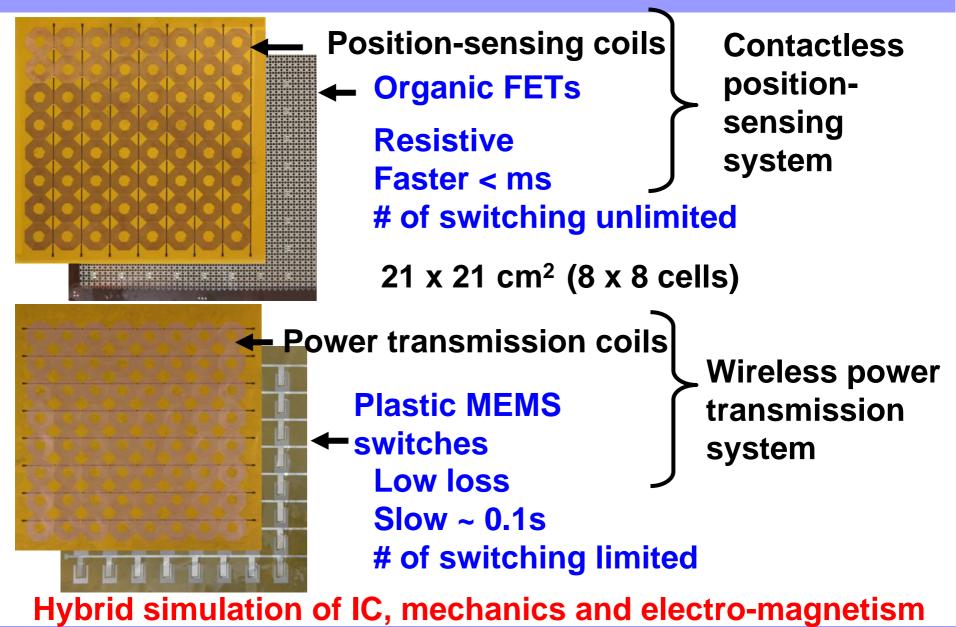

# Wireless power transmission sheet with plastic MEMS switches and OFETs

T.Sekitani, M.Takamiya, Y.Noguchi, S.Nakano, Y.Kato, K.Hizu, H.Kawaguchi, T.Sakurai, and T.Someya, "A large-area flexible wireless power transmission sheet using printed plastic MEMS switches and organic field-effect transistors," Paper#11.1, IEDM 2006, Dec. 2006.

M.Takamiya, T.Sekitani, Y.Miyamoto, Y.Noguchi, H.Kawaguchi, T.Someya and T.Sakurai, "Design Solutions for a Multi-Object Wireless Power Transmission Sheet Based on Plastic Switches," Paper#20.4, ISSCC, Feb. 2007.

## **Position-sensing and selective activation**

#### **Stacking sheets for MEMS and Organic FETs**

#### Wireless power transmission sheet (3Dstacked) Large-area & Low cost Dosition sensing

#### High pov/er

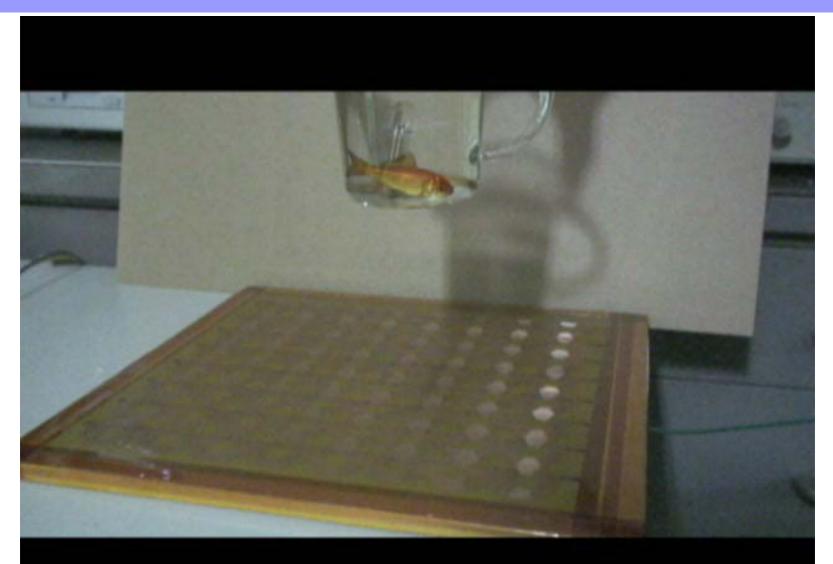

Size : <u>21 x 21 cm2</u> Thickness : <u>1 mm</u> Weight : <u>50 g</u> Efficiency : <u>62.3%</u> Max received power : <u>29.3</u>

**Lightweight & Printable**

#### X'mas tree w/o a battery wirelessly powered

# 21 LEDs 13.56 MHz

**Received power : 2 W**

#### **No electrical shock**

#### I touched it by my hand. No problem ©

#### Wirelessly powered room in the future Providing infrastructure ubiquitous electronics In the wall

TV on a wall Mobile phone & PC & e-accessories

(data can be wireless but USB's wire delivers power)

In the table

#### Ambient illumination

In the floor

Home-care robot

Vacuum cleaner

### Summary

- 3-D stacking, new frontier of integrated circuits, is opening up new electronics.

- Solving issues for higher performance, lower power, lower cost and newer functions

- New design tools for hybrid simulation and synthesis to fully enjoy 3-D stacking