Parameterized Embedded In-Circuit Emulator and Its Retargetable Debugging Software for Microprocessor/Microcontroller/ DSP Processor

#### Presenter: Liang-Bi Chen

imbedded Systems Laboratory National Sun Yat-Sen University Authors: Liang-Bi Chen, Yung-Chih Liu, Chien Hung Chen Chung-Fu Kao, and Ing-Jer Huang

Embedded Systems Laboratory

Dept. of Computer Science and Engineering

National Sun Yat-Sen University, Taiwan, R.O.C.

### Introduction to Embedded ICE

- Preserve the original behavior of a microprocessor

- Embedded ICE contains hardware breakpoint

- Allows instruction breakpoints and data watchpoints to be set

- Programmable through JTAG

- Comparators monitor:

- Address bus

- Data bus

- Control signals

- When there is a match:

- the processor halts execution

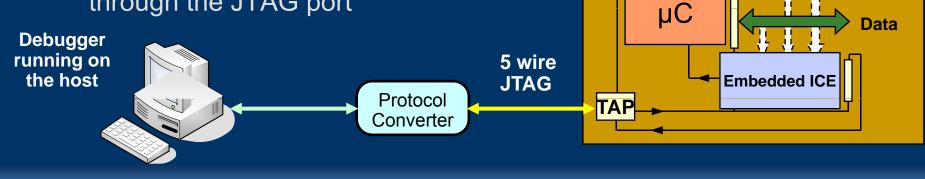

- the debugger allows the user to view the state of the registers and memory through the JTAG port

Control

μP

or

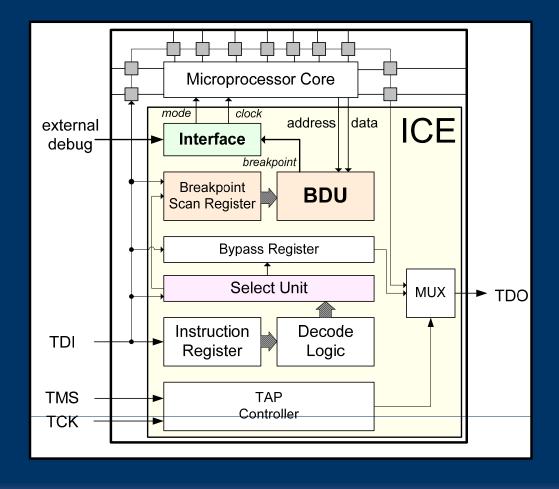

**Block Diagram for the Embedded ICE**

## Our EICE is based on IEEE 1149.1 with some extensions

## JTAG Extensions to Support the EICE Functionality Component Modification

Classification Components TAP controller, Boundary Scan Registers, Bypass Original 1149.1 Register JTAG components Instruction Register, Instruction Decode Logic, Data Modified 1149.1 **Register Selector** JTAG components Core Data Register, Breakpoint Scan Register, Scan-Chain Select Register, Breakpoint Detection Unit New Components

## Feature

- Reusable ability to Reduce HW/SW Development Cost

- In general, EICEs are designed for specific targets.

- Our design can be applied different processors

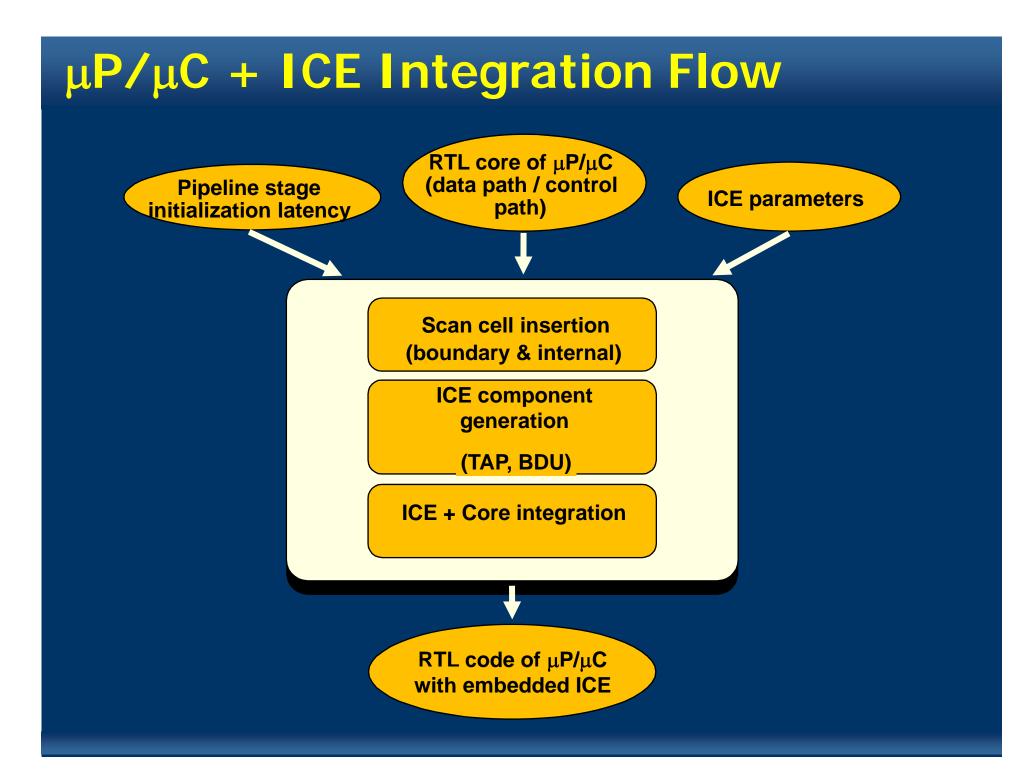

- Easy to Integrate Embedded ICE IP into Processor

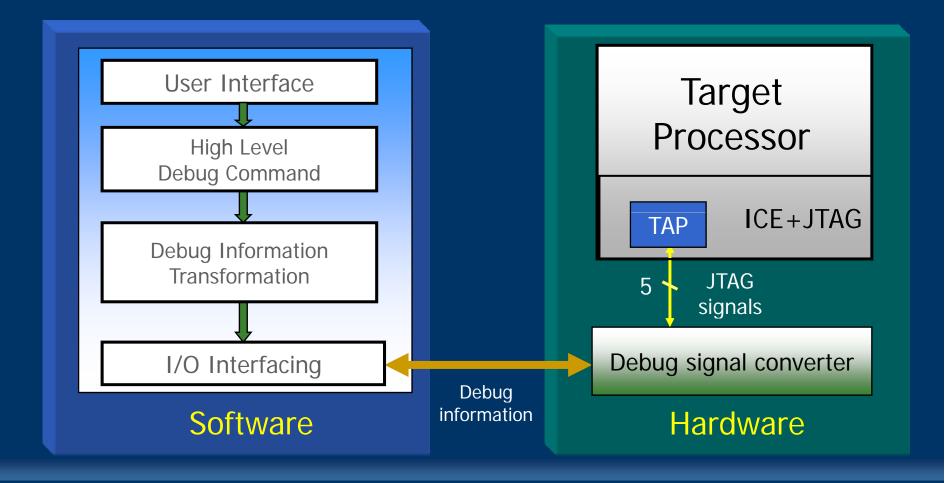

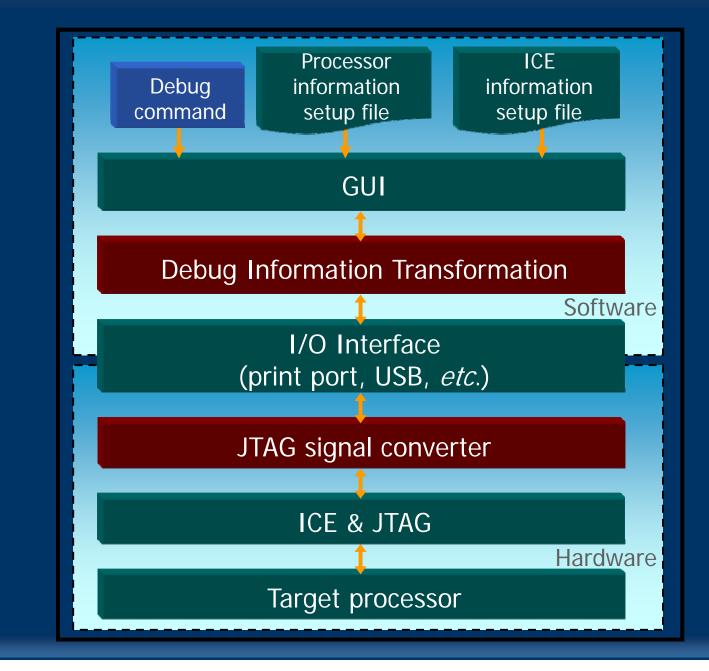

## **Proposed approach**

#### HW/SW co-generate the debugging information

### Retargetable EICE debugging software

### **Integration Consideration**

- Interface between microprocessor and ICE

- Insertion of internal scan cells

- Define test data registers

- Breakpoint scan register

- Breakpoint detection unit

- Test data register selection method

- JTAG instructions extension

- Instruction decoder modification

### **Applications of the Retargetable ICE**

- with 8-bit μC:

- HT48100 (FPGA, chip) ... Holtek

- with 32-bit μP:

- Academic ARM7-like CPU core (SYS32TM Series) (FPGA, chip) ...NSYSU

- SPARC-like core (RTL) ... ACard

- K310 CPU (in progress) ... Himax

# With DSPs:

- PAC DSP (FPGA, chip) ... ITRI-STC,

- "Q" DSP (in progress) ... Himax

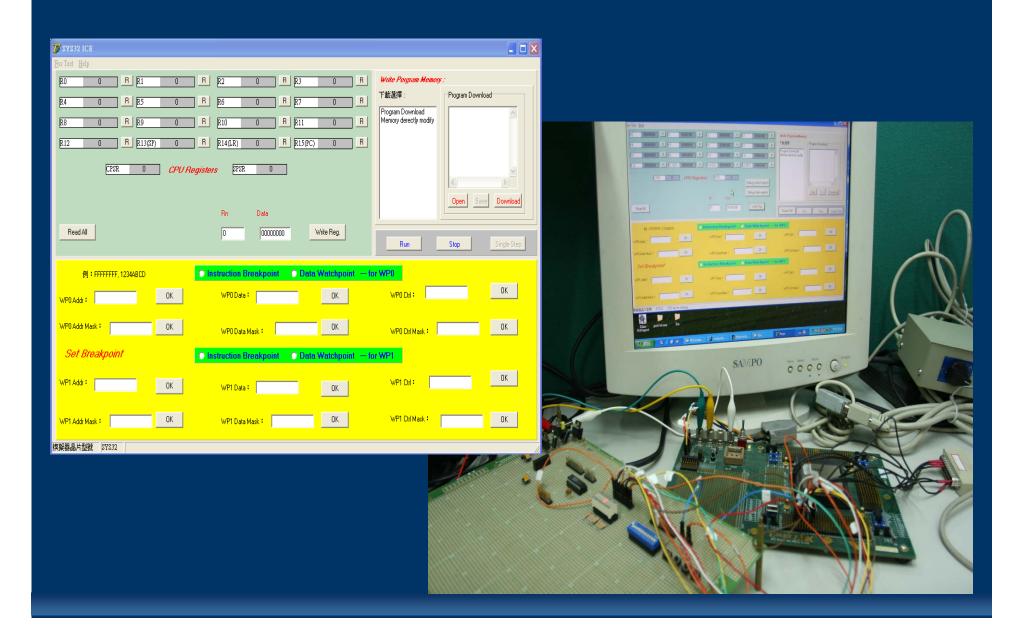

## **Prototyping for Our Designed Environment**

## **Prototyping for ARM Development Environment**

|                                                                    | ExtROM                                                | Prototyping FPGA              |

|--------------------------------------------------------------------|-------------------------------------------------------|-------------------------------|

|                                                                    |                                                       | Processor Core<br>(SYS32TM)   |

|                                                                    | ExtRAM                                                | Embedded ICE                  |

| File Edit Yiew Target Project Build Debug Tools Help               |                                                       |                               |

| 🗅 😹 🖉 🗼 🛍 🛍 💷 🖉 የንምምምም 🕈 🕇 🖊 🎉                                     | 🗶 🗈 🕼 🕼 🕼 🚛 🗶 📉 🚺 Tube 🔫                              | AMBA AHB 🕴 🕴 💱                |

| ile Dam Find Low Level Step Into                                   |                                                       |                               |

|                                                                    |                                                       |                               |

| 0000042C E3A0B01B MOV rll,#0x1b                                    |                                                       | SMI Arbiter TIC Decoder       |

| 00000430 E3A0C01C MOV r12,#0x1c                                    |                                                       |                               |

| 00000434 E3A0D01D MOV r13,#0x1d                                    | R2 00000013 R3 00000014                               |                               |

| 00000438 E1A00000 NOP                                              | R4 0000015 R5 0000015                                 |                               |

| 0000043C E3A00011 MOV r0,#0x11                                     |                                                       |                               |

| 00000440 E3A01012 MOV r1,#0x12<br>00000444 E3A02013 MOV r2,#0x13   |                                                       |                               |

| 00000444 E3A02013 NOV r2,#0x13<br>00000448 E3A03014 NOV r3,#0x14   |                                                       |                               |

| 00000440 E3A03014 H0V 13, F0X14<br>0000044C E3A04015 M0V r4, #0x15 | R10 0000001A R11 0000001B<br>R12 0000001C 3P 0000001D |                               |

| 00000450 E3A05016 NOV r5,#0x16                                     | LR 00000454 PC 00000444                               |                               |

| 00000454 E3A06017 MOV r6,#0x17                                     |                                                       |                               |

| 00000458 E3A07018 MOV r7,#0x18                                     | CPSR 00000010<br>MZCV FTO TRO STATE MODE              |                               |

| 0000045C E3A08019 MOV r8,#0x19                                     | Core / Debug /                                        |                               |

| 00000460 E3A0901A MOV r9,#0x1a                                     |                                                       |                               |

| 00000464 E3A0A01B MOV r10,#0x1b                                    |                                                       |                               |

| 00000468 E3A0B01C MOV r11,#0x1c                                    |                                                       |                               |

| 0000046C E3A0C01D MOV r12,#0x1d                                    | Type Value                                            |                               |

| 00000470 E3A0D01E NOV r13,#0x1e                                    | ARN7TDHI r1 PC=0x0000044C                             |                               |

| 22222 JE & BU 122222 BA                                            | Image <none></none>                                   |                               |

| 00000474 E1A00000 NOP                                              |                                                       |                               |

| 00000478 E3A00012 MOV r0,#0x12                                     |                                                       |                               |

|                                                                    | ARM                                                   | Reduces and States and States |

#### Conclusion

- We propose a parameterized embedded in-circuit emulator and its retargetable debugging software in order to reduce the debugging design procedure time for different target systems.

- The goal is to integrate the EICE component into the microcontroller/microprocessor/DSP processor, and to execute debugging functions via proposed retargetable GUI debugger tool.

- As a result of it, the duration of debugging procedure and time-to-market is reduced.