# Designer's Forum at ASP-DAC Best Ways to use Billions of Devices on a Chip

Panel presentation by

J. Henkel, Univ. Karlsruhe

Seoul, Jan. 25th 2008

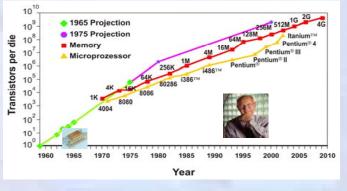

# In the past ...

- □ ... Moore's Law provided a win-win- situation:

- Smaller feature size

- Higher integration density

- Lower power consumption

- Higher speed (performance)

- Less cost (per-transistor costs)

Scalability, as we experienced for the last four decades is at its end as we enter the Nano Era!

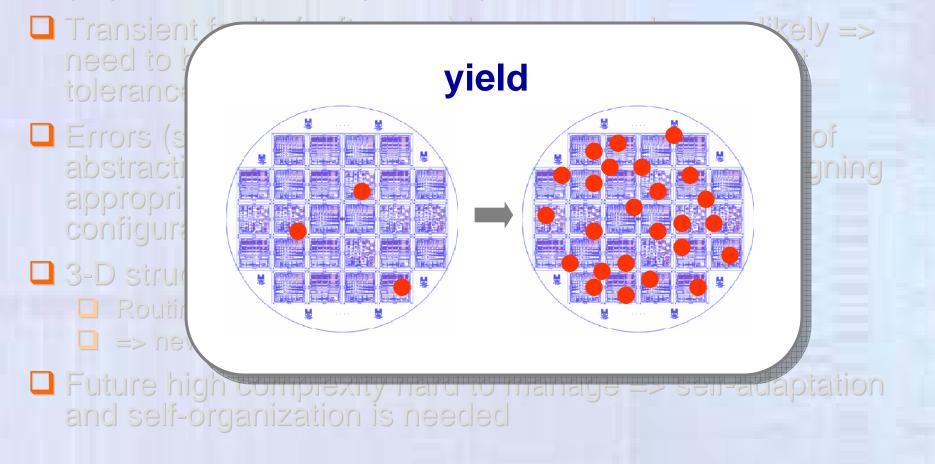

New structures will be hard to integrate => yield decreases drastically => "live" with faults rather than avoiding them (expensive and/or impossible)

New structures will be hard to integrate => yield decreases drastically => "live" with faults rather than avoiding them (expensive and/or impossible)

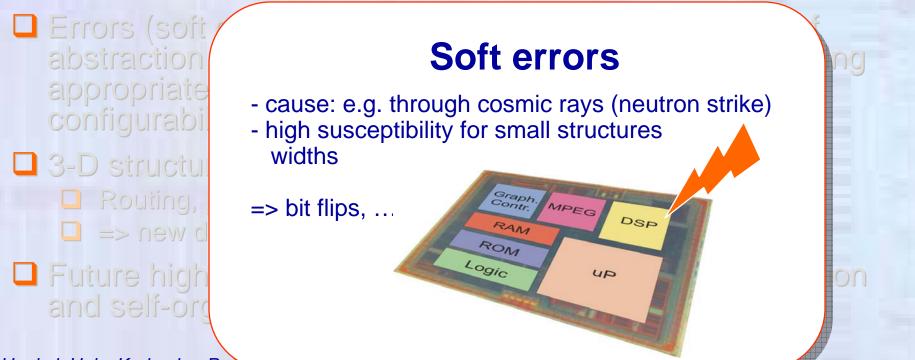

Transient faults (soft errors) become much more likely => need to be considered in the design process => fault tolerance plays a key role

J. Henkel, Univ. Karlsruhe, Pane

Best Ways to use Billions of Devices on a Chip 5

# In the future ...

### Reconfigurability as a means to address errors

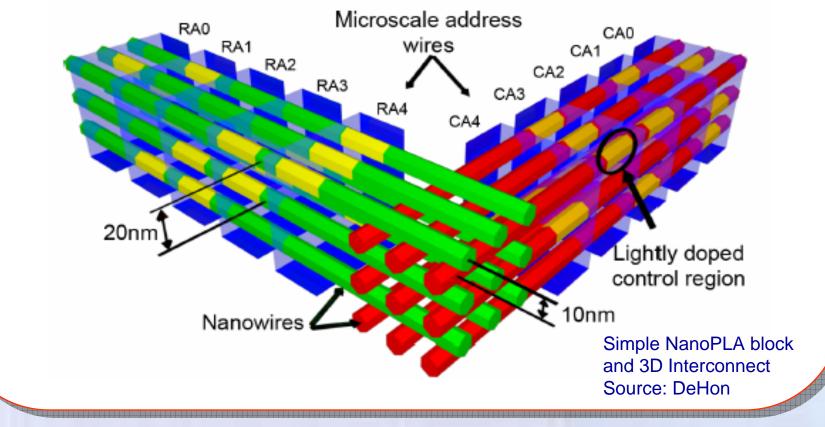

Shown: 3-D PLA

- New structures will be hard to integrate => yield decreases drastically => "live" with faults rather than avoiding them (expensive and/or impossible)

- Transient faults (soft errors) become much more likely => need to be considered in the design process => fault tolerance plays a key role

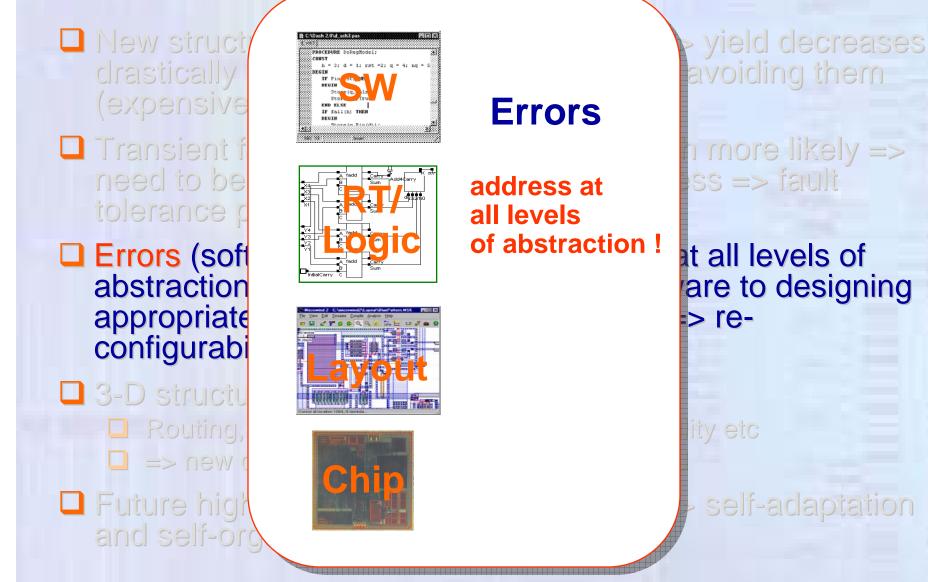

- Errors (soft or hard) need be considered at all levels of abstraction from manufacturing the hardware to designing appropriate software => higher flexibility => reconfigurability

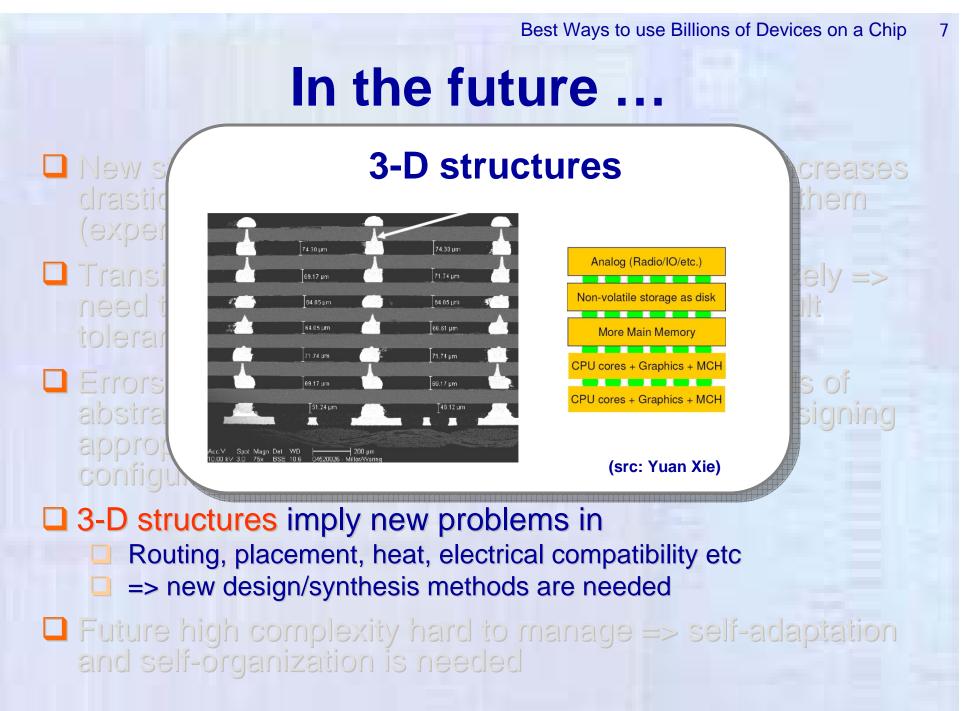

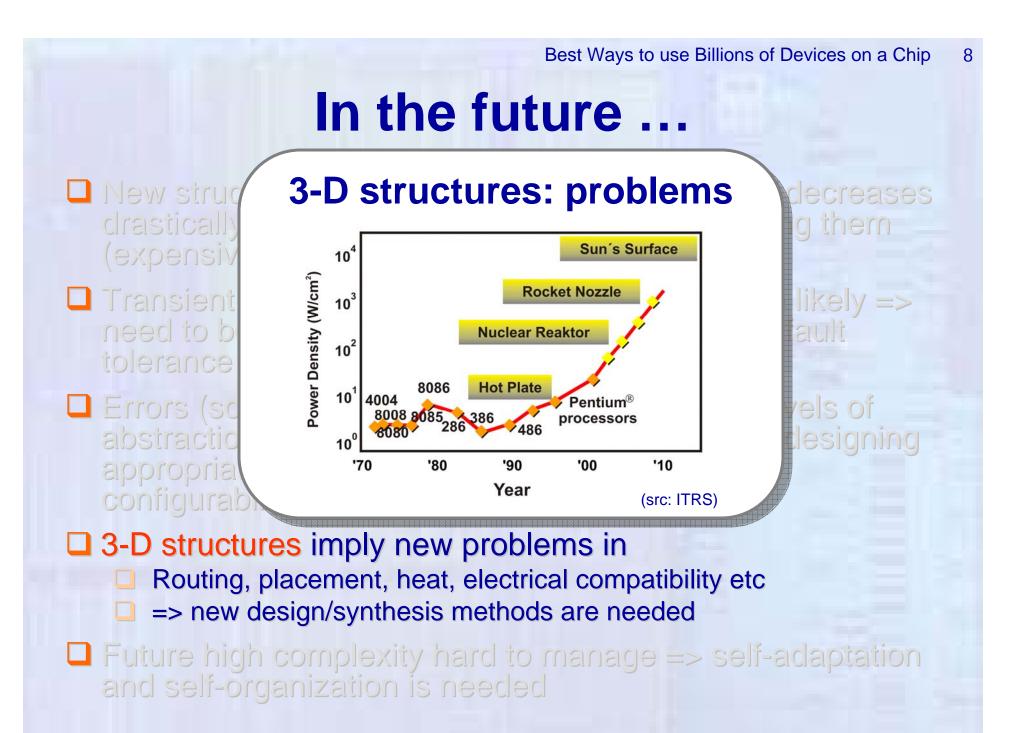

- 3-D structures imply new problems in

- Routing, placement, heat, electrical compatibility etc

- I => new design/synthesis methods are needed

### Future high complexity hard to manage => self-adaptation and self-organization is needed

# **Summary Problems**

- Power (Reduction, Delivery, Distribution)

- Heat (Reduction, Removal, Dealing with hot spots)

- Interconnects (Reduce length/delay, Reduce number)

- Testability / Verification (Reducing associated costs)

- Reliability (Economical redundancy factors, Reconfiguration, Adaptive)

- Communication (Low-power, Non-flooding, Reliable)

- Hybrid integration (Mixed design, Interfacing)

- Logic and coding (Non-Boolean(?), Error correction, Spikes)

- Algorithms (Stochastic / Probabilistic)

- Design complexity (Reduce associated cost by reuse)

Best Ways to use Billions of Devices on a Chip 11

System

Arithmetic

**Center for Functional**

Univ. Karlsruhe

**Device** Nano Structures at

Logic

# **Solutions**

#### Near term solutions:

- Massively parallel, modularity (cells, blocks)

- Regularity (grid processing, cellular arrays)

- Locally connected (near-neighbor connections, crossbar)

- Higher functionality (multiple valued logic, threshold logic)

- Reconfigurability (self-mapping)

#### Medium term solutions:

- Asynchronous (including GALS)

- Fault-tolerance (noise immune,, redundant, self-testing, self-correcting)

### Defect-tolerant (adaptable/reconfigurable)

Redundant, adaptive (self-adaptive, self-organizing, evolvable)

## Bio-inspired (complex functions, self-organizing, self-healing)

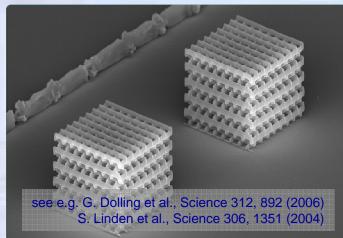

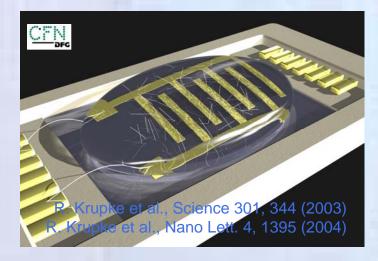

- Nanophotonic (optical communication, GOLE)

- Nanofluidic

- 3D interconnects

- Probabilistic (algorithms, encoding, communication)

#### □ Long term solutions:

- molecular, quantum

- quantum-dot cellular automata

- Adiabatic / reversible

- Bio-compatible

# Multidisciplinary Research Effort at Univ. Karlsruhe

Creation of a NEW FIELD GROUP (est. 2007) to address the high-lighted problems

### Multidisciplinary Research

Computer Science

J. Henkel, W. Karl, ...

Electrical Engineering

J. Becker, J. Leuthold, ...

Physics

G. Schoen, H. Hahn, ...

We do not have as many devices available for computation/communication as we may think we have! **Devices from CFN Karlsruhe**