## Adaptive Inter-router Links for Low-Power, Area-Efficient and Reliable Network-on-Chip (NoC) Architectures

## Avinash Karanth Kodi<sup>†</sup>, Ashwini Sarathy<sup>\*</sup>, Ahmed Louri<sup>\*</sup> and Janet Wang<sup>\*</sup>

<sup>†</sup>Department of Electrical Engineering and Computer Science, Ohio University, Athens, OH 45701 <sup>\*</sup>Department of Electrical and Computer Engineering, University of Arizona, Tucson, AZ 85721 E-mail: <u>kodi@ohio.edu</u>, <u>{sarathya, louri, wml} @ece.arizona.edu</u>

Speaker : Jin Sun

Dept. of Electrical and Computer Engineering, University of Arizona, Tucson, AZ 85721

<u>Sponsored:</u> National Science Foundation (NSF) grants CCR-0538945 and ECCS-0725765 (at the High Performance Computing Architectures and Technologies Lab, University of Arizona, Tucson)

## Talk Outline

- Motivation

- iDEAL inter-router Dual-function Energy and Area-efficient Links for NoC architectures

- Dual-function links

- Design of static & dynamic router buffer

- Performance Evaluation

- Power and area estimation

- Simulation results (power, throughput)

- Design headroom for Negative Bias Temperature Instability (NBTI) related reliability issues

- Conclusion

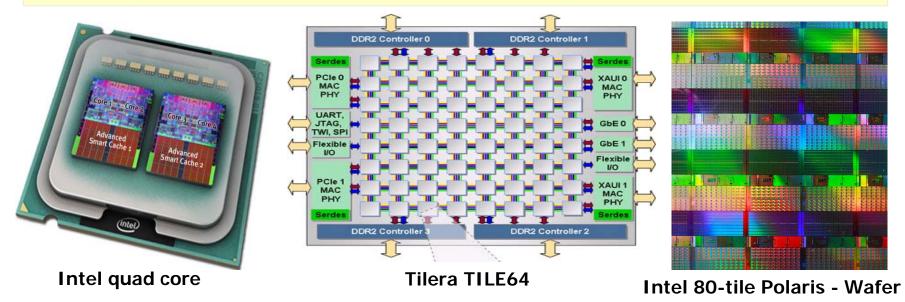

# Motivation for Networks-on-Chips (1/2)

Technology scaling - Increase in transistor density on a single chip

•Chip MultiProcessors (CMPs) and MultiProcessor System-on-Chip (MPSoC) architectures

- Challenges in future scaling of CMPs and MPSoCs :

- Overcoming the increasing wire delays

- Minimizing the power consumption

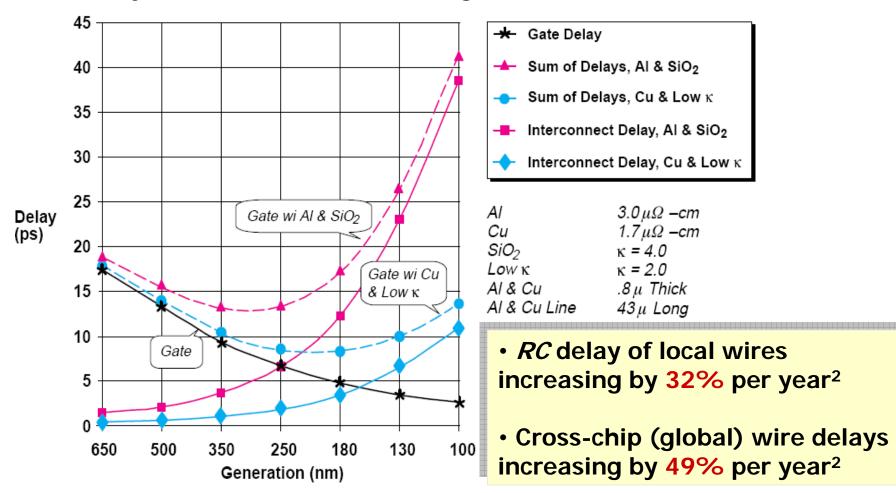

# Motivation for Networks-on-Chips (2/2)

Wire delay constraint with decreasing feature size

<sup>1. 1997</sup> Roadmap of the Semiconductor Industry Association

2. W. J. Dally and J. W. Poulton, *Digital Systems Engineering*, Cambridge University Press, NY, USA, 2001.

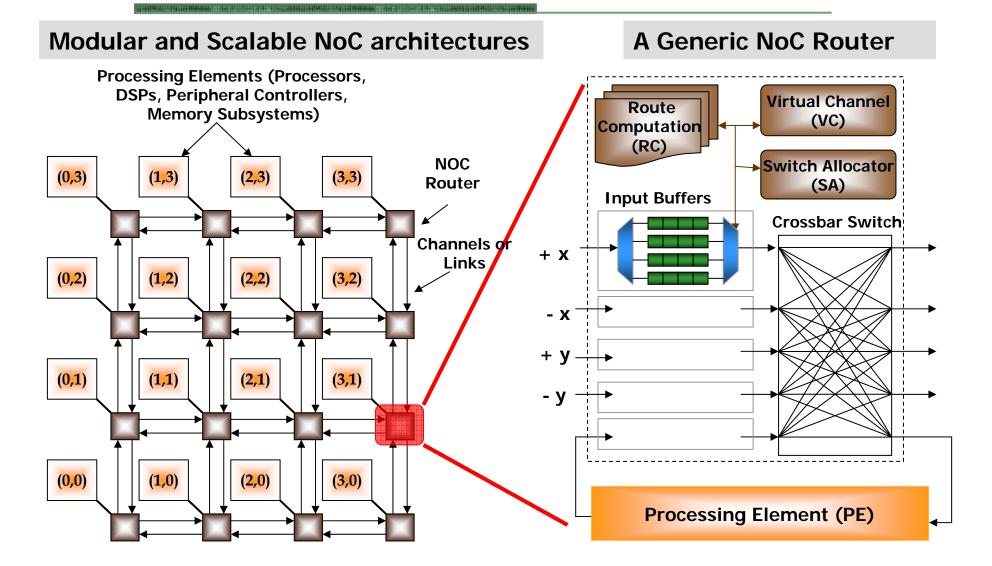

## The Network-on-Chip (NoC) Paradigm

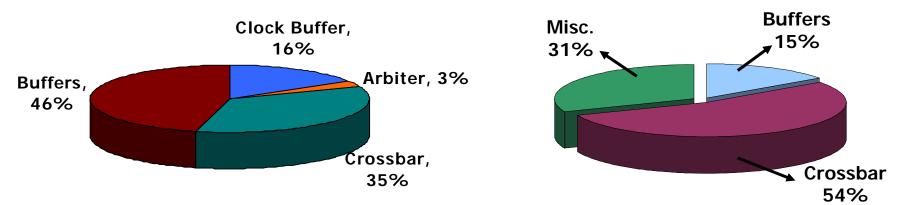

## **Significance of Router Buffers in NoCs**

**Recent NSF-sponsored workshop on On-Chip Interconnection Networks**<sup>[1]</sup>:

- "The most important technology constraint for on-chip networks is power consumption".

- Power consumption of OCINs implemented with current techniques exceeds expected needs by a factor of 10.

Power Break-up in the NoC Router <sup>[2]</sup>

Area profile of a generic NoC Router <sup>[2]</sup>

6

1. J.D.Owens, W.J.Dally, R.Ho, D.N.Jayasimha, S.W.Keckler and L.S.Peh, "Research Challenges for On-Chip Interconnection Networks", IEEE Micro, vol. 27, no. 5, pp. 96 – 108, September-October 2007.

2. S.R.Vangal, *et al.*, "An 80-Tile Sub-100-W TeraFLOPS Processor in 65-nm CMOS", IEEE J. Solid-State Circuits, Vol. 43, no. 1, January 2008.

#### iDEAL – Inter-router Dual-function Energy and Areaefficient Links for NoC architectures

#### **iDEAL – Inter-router Dual-function Energy and Area**efficient Links for NoC architectures

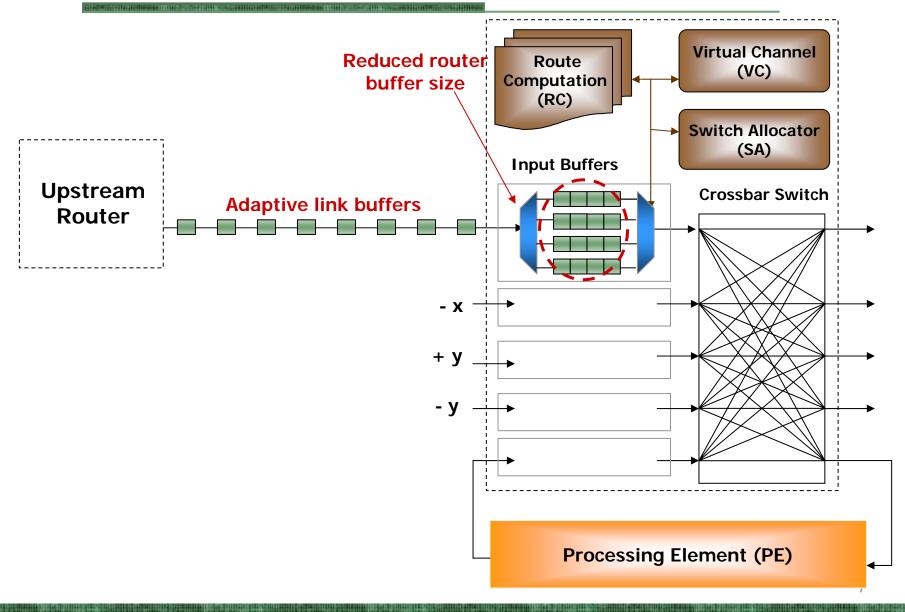

#### **iDEAL** Methodology

- Reduce the number of router buffers (power and area savings)

- Use adaptive link buffers to store data along the links when required (create more storage)

- Dynamic buffer allocation within the router buffers (to sustain performance)

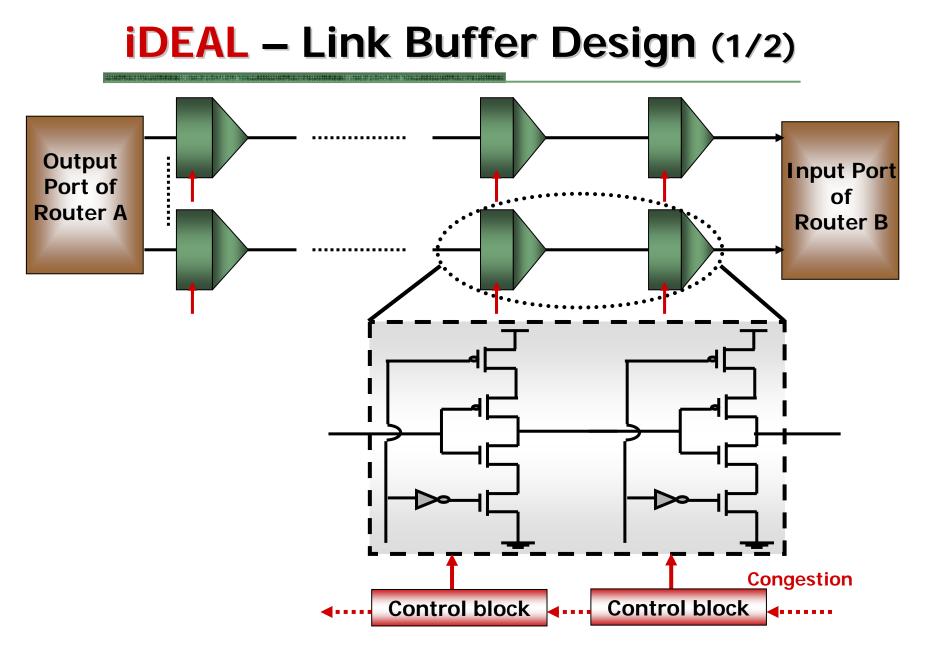

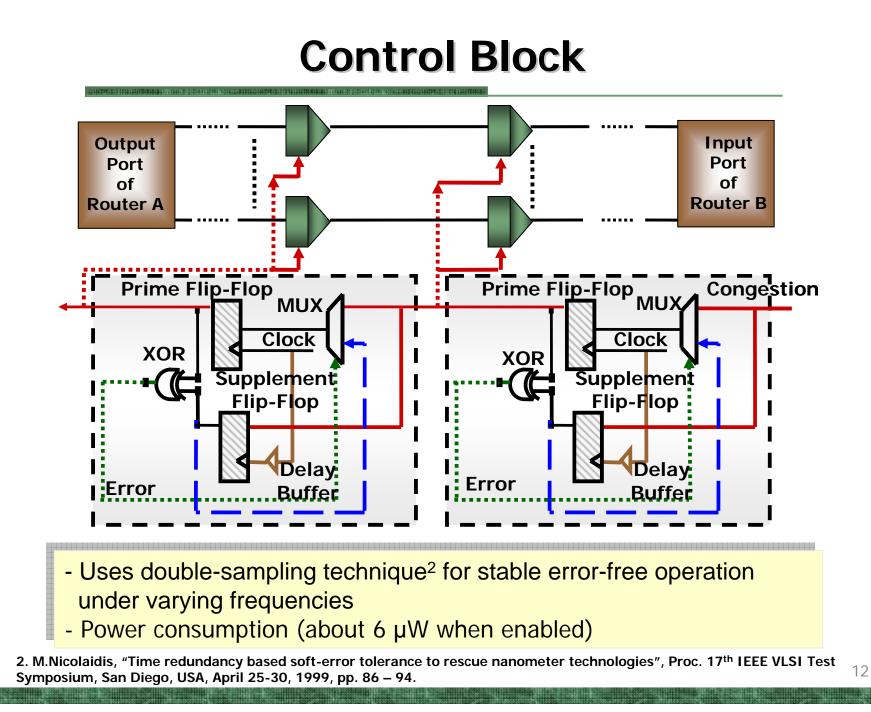

# **iDEAL** – Link Buffer Design (2/2) **Control block Control block**

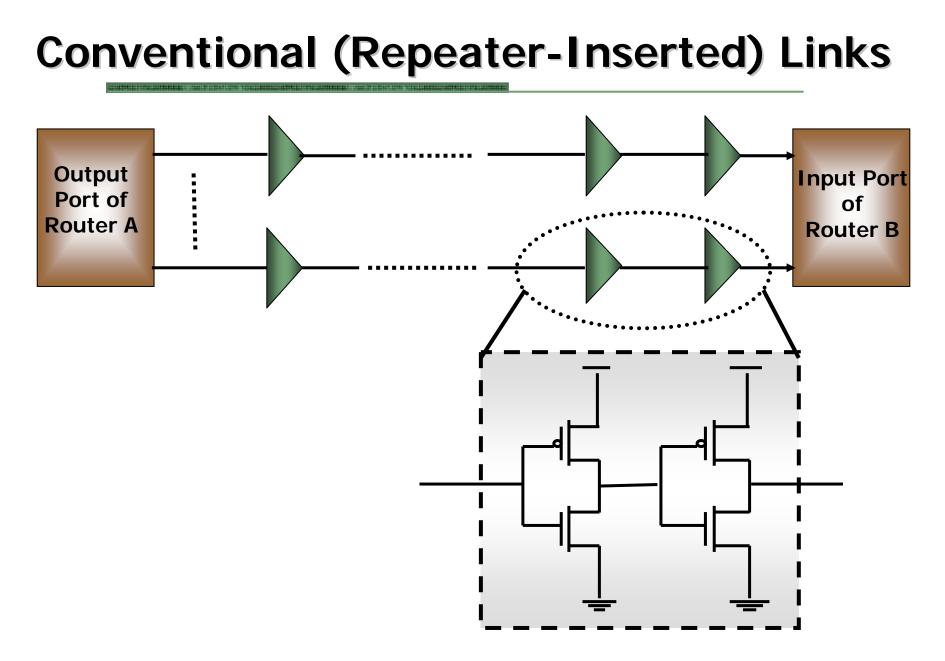

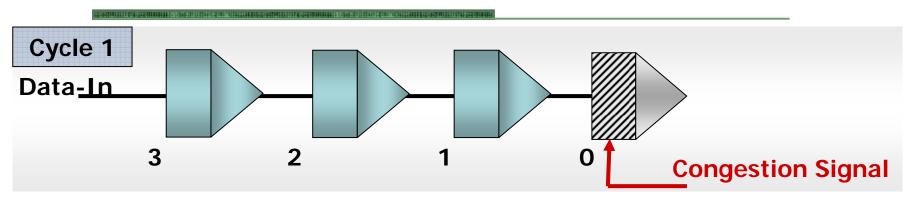

Functions as a conventional repeater when there is no congestion.

Control block is turned 'OFF'.

Repeater tri-stated and holds the sampled value, during congestion.

Control block is turned 'ON'.

## **Dual-function Link**

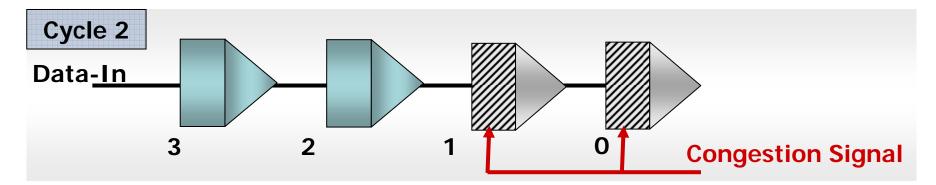

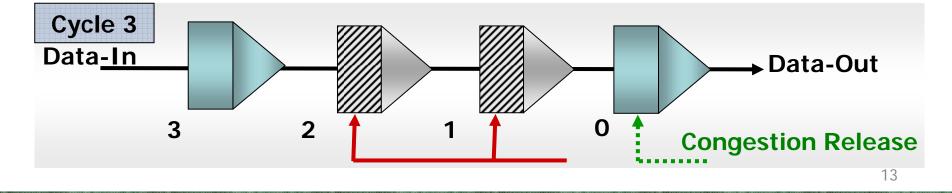

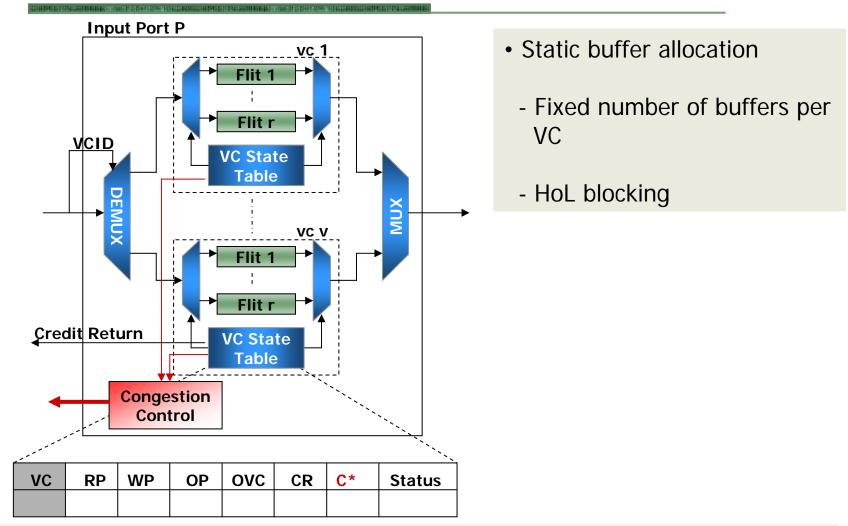

## **Statically Allocated Router Buffer**

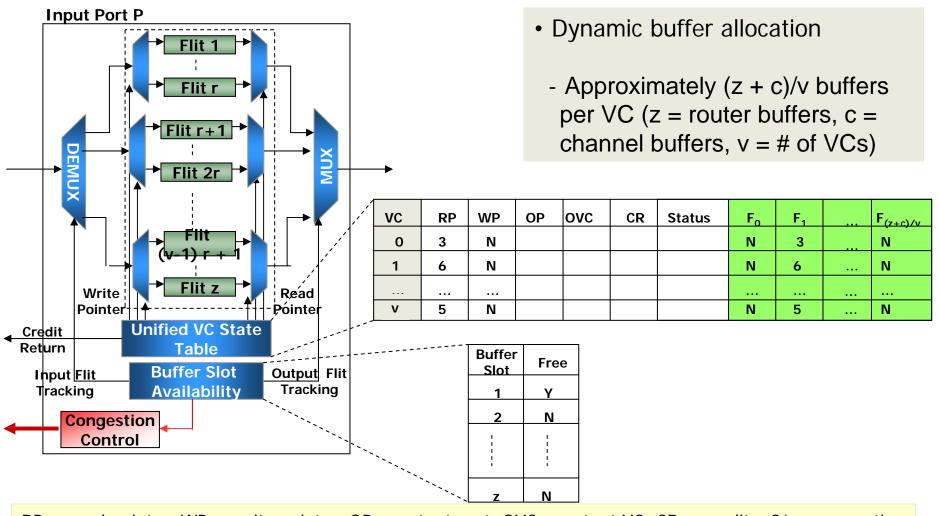

RP = read pointer, WP = write pointer, OP = output port, OVC = output VC, CR = credits, C\* = congestion Status = status of the VC (idle, waiting, RC, VA, SA, ST)

## **Dynamically Allocated Router Buffer (1/2)**

RP = read pointer, WP = write pointer, OP = output port, OVC = output VC, CR = credits,  $C^* = congestion Status = status of the VC (idle, waiting, RC, VA, SA, ST)$

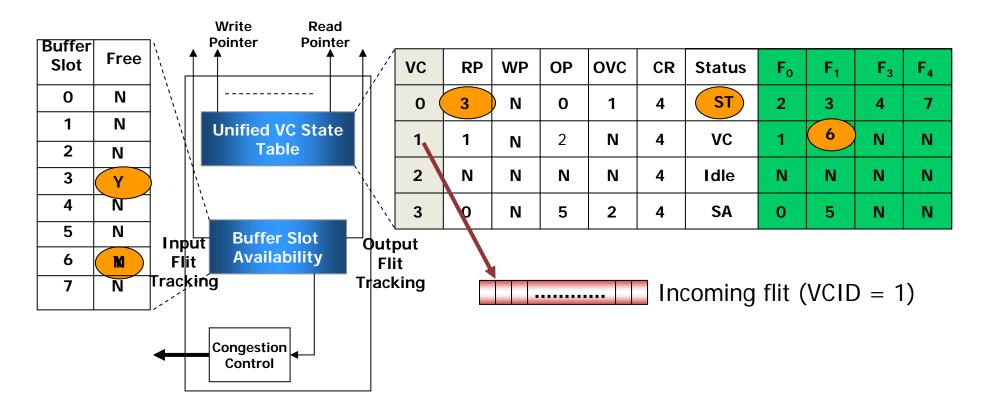

## **Dynamically Allocated Router Buffer (2/2)**

#### • Example illustrating Dynamic buffer allocation in iDEAL

RP = read pointer, WP = write pointer, OP = output port, OVC = output VC, CR = credits,  $C^* = congestion Status = status of the VC (idle, waiting, RC, VA, SA, ST)$

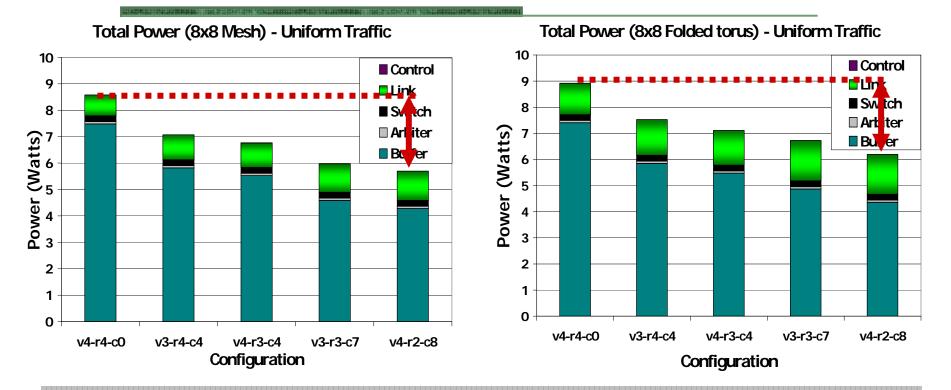

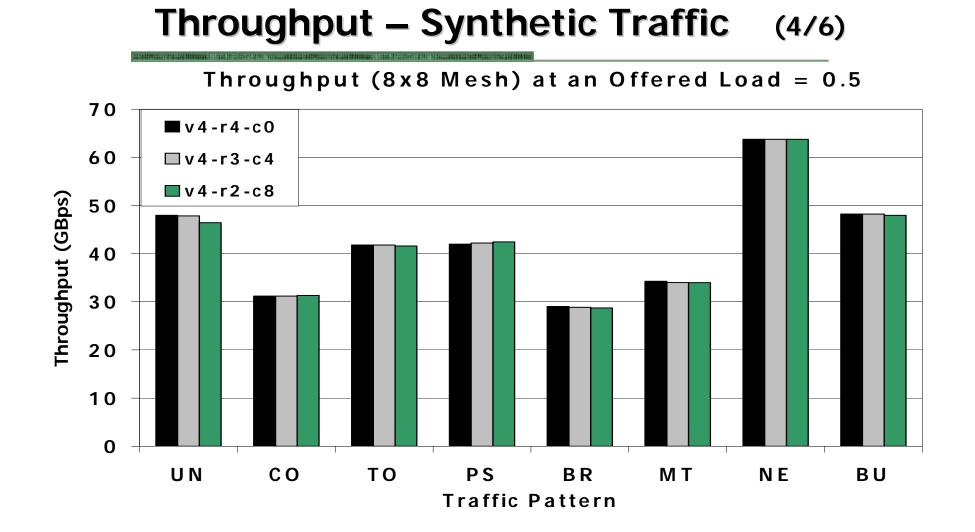

## **Performance Evaluation**

- Evaluated on a cycle-accurate on-chip network simulator

- Simulated 8 x 8 Mesh and 8 x 8 Folded Torus topologies

- Synthetic benchmarks such as uniform, and non-uniform workloads (Butterfly, Complement, Perfect Shuffle, Matrix Transpose, Bit Reversal) as well as SPLASH-2 suite benchmarks (FFT, LU, MP3D, WATER, RADIX) were evaluated

- Parameters evaluated include throughput, latency and overall network power

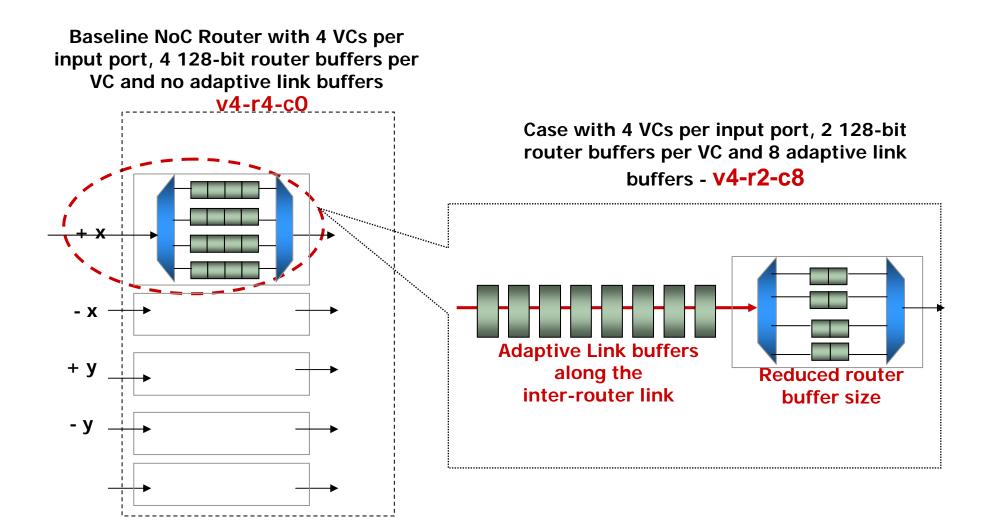

- Considered 5 different configurations  $(vn_v rn_R cn_C)$  $(n_v = No. of VCs per input port, n_R = No. of router buffers per VC, n_C = number of channel buffers)$

- Baseline = 440

- 434, 428, 344, 531

## **Different Test Cases Considered**

## Power Estimation – Summary with values from Synopsys Design Compiler

| vn <sub>v</sub> –<br>rn <sub>R</sub> –<br>cn <sub>c</sub> | Buffer<br>Power<br>(mW) | Mesh<br>Link +<br>Control<br>Power (mW) | Folded<br>Torus<br>Link +<br>Control<br>Power (mW) | Mesh<br>Total Power<br>(Buffer +<br>Link)<br>(mW) | %<br>Change | Folded<br>Torus<br>Total<br>Power<br>(Buffer +<br>Link)<br>(mW) | %<br>Change |

|-----------------------------------------------------------|-------------------------|-----------------------------------------|----------------------------------------------------|---------------------------------------------------|-------------|-----------------------------------------------------------------|-------------|

| v4-r4-c0                                                  | 19.54                   | 2.45 + 0                                | 3.94 + 0                                           | 21.99                                             | -           | 23.48                                                           | -           |

| v4-r3-c4                                                  | 14.51                   | 2.90 + 0.0012                           | 4.39 + 0.0012                                      | 17.42                                             | -20.78      | 18.91                                                           | -19.46      |

| v4-r2-c8                                                  | 11.57                   | 3.55 + 0.02                             | 2 5.04 + 0.02                                      | 2 15.14                                           | -31.15      | 16.63                                                           | -29.17      |

| v3-r4-c4                                                  | 15.09                   | 2.90 + 0.0012                           | 4.39 + 0.0012                                      | 18.00                                             | -18.14      | 19.49                                                           | -16.99      |

| v3-r3-c7                                                  | 12.56                   | 3.49 + 0.0180                           | 4.98 + 0.0180                                      | 16.06                                             | -26.96      | 17.55                                                           | -25.25      |

$n_{V}$  = number of VCs per input port,  $n_{R}$  = number of router buffers per VC,  $n_{C}$  = number of link buffers

## Area Estimation – Summary with values from Synopsys Design Compiler

| vn <sub>v</sub> – rn <sub>R</sub> -<br>cn <sub>c</sub> | Buffer Area<br>(µm²) | Link Repeater<br>Area (µm²) | Total Buffer + Link<br>Area (μm²) | % Change |

|--------------------------------------------------------|----------------------|-----------------------------|-----------------------------------|----------|

| v4-r4-c0                                               | 81,407               | 8,960                       | 90,367                            | -        |

| v4-r3-c4                                               | 63,991               | 6,656                       | 70,647                            | -21.8    |

| v4-r2-c8                                               | 48,066               | 10,240                      | 58,306                            | -35.5    |

| v3-r4-c4                                               | 63,250               | 6,656                       | 69,906                            | -22.6    |

| v3-r3-c7                                               | 50,373               | 9,344                       | 59,717                            | -34.0    |

$n_V$  = number of VCs per input port,  $n_R$  = number of router buffers per VC,  $n_C$  = number of link buffers

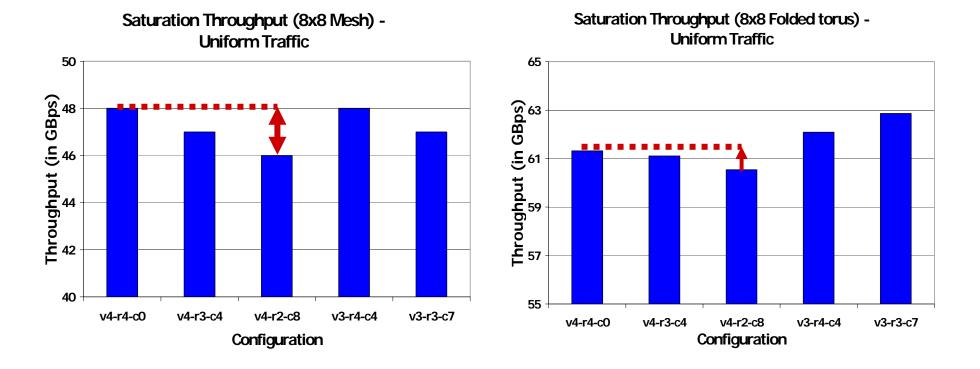

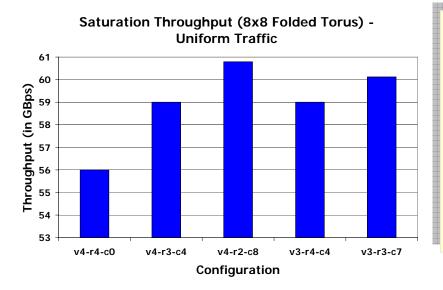

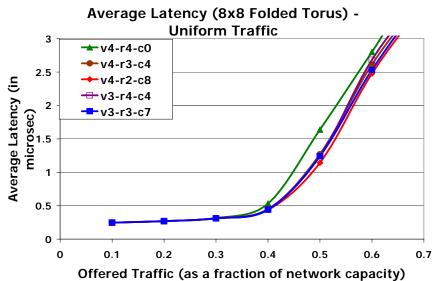

## **Network Simulation Results**

(1/6)

Uniformly distributed traffic

⇒ Only about 3% drop in throughput for the v4-r2-c8 case

(428 = 4 VCs per port, 2 router buffers per VC, 8 link buffers)

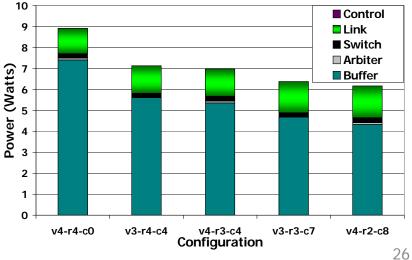

## **Network Simulation Results**

(2/6)

Total power consumed for a network load of 0.5

> Nearly 30% savings in overall network power for the v4-r2-c8 case

(428 = 4 VCs per port, 2 router buffers per VC, 8 link buffers)

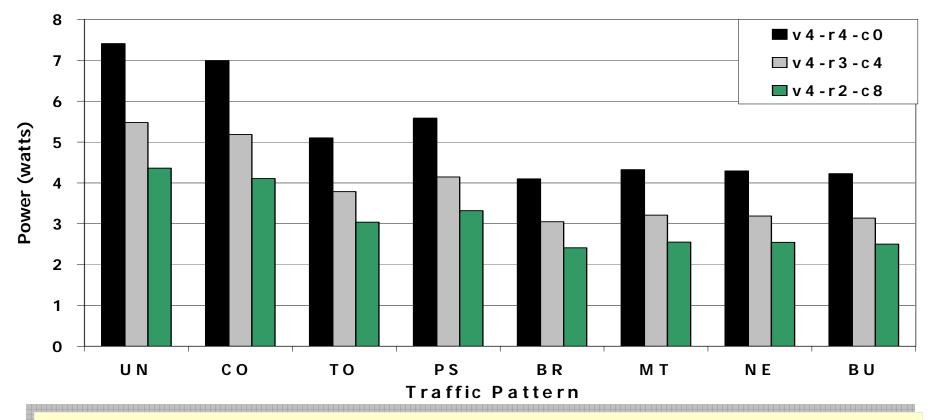

### Buffer Power – Synthetic Traffic (3/6)

Buffer Power (8x8 Mesh) at an Offered Load = 0.5

- Reduction in power for all configurations, under all traffic patterns, compared to the baseline (440)

- For example, under Complement traffic the 4-2-8 configuration achieves 40% savings

• No significant decrease in throughput under any traffic pattern, using Dynamic allocation

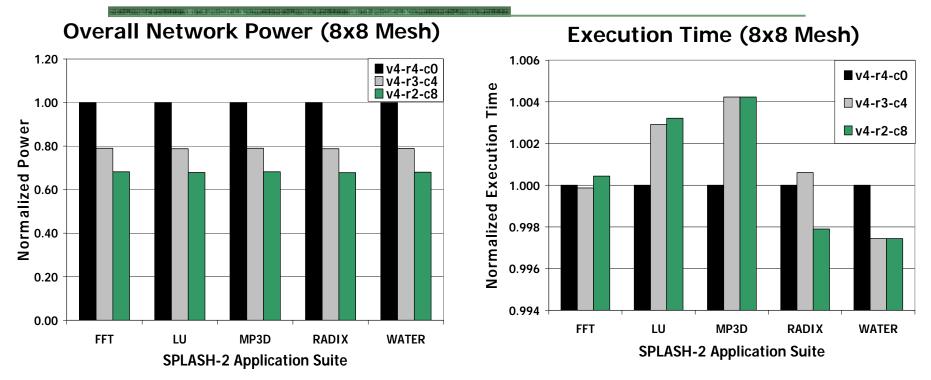

## Simulation results for the SPLASH-2 suite (5/6)

Nearly 30% savings in overall network power for the v4-r2-c8 case with only about 1% drop in performance

(v4-r2-c8 = 4 VCs per port, 2 router buffers per VC, 8 link buffers)

## **Aggressive Speculation**

- Aggressive speculation by increasing the number of credits available to 8

- Additional credits are accounted for by the link buffers

$\Rightarrow$  Saturation throughput improves by 10% for the 428 case

## **Design Headroom for NBTI-related issues**

- Negative Bias Temperature Instability (NBTI) affects PMOS gates with a '0' input. Additional circuits may be employed to change the input of 'Idle' PMOS gates to '1' <sup>3</sup>.

- iDEAL architecture 'moves some of the buffers from the router to the links' and provides a low-power area-efficient solution with

- Reduced power density and temperature in the routers, thereby alleviating NBTI-related degradation

- Sufficient design headroom for the Thermal Design Power (TDP) of the auxiliary circuits

$$\begin{split} \text{TDP}_{\text{NoC}} &\leq \text{P}_{\text{saved}} \\ \text{TDP}_{\text{NoC}} &= \text{K x S}_{\text{r}} \\ \text{(P}_{\text{saved}} &= \text{power reduction achieved by iDEAL, K} &= \text{impact of the area on the TDP,} \\ \text{S}_{\text{r}} &= \text{area reduction achieved by iDEAL)} \end{split}$$

3. J.Abella, X.Vera and A.Gonzalez, "Penelope: The NBTI-aware processor", Proc. 40<sup>th</sup> Annual ACM/IEEE Intl. Symp. Micro Arch. (MICRO-40), Chicago, IL, USA, December 1-5, 2007, pp. 85 – 96.

## Conclusion

- **iDEAL** architecture provides a low-power area-efficient solution for NoCs, by reducing power consumption through circuit-level and architecture-level techniques.

- Simulation results show that by reducing the buffer size in half, a 30% savings in overall network power and 35% savings in overall area is achieved.

- There is only a marginal 1-3% drop in performance, under dynamic buffer allocation. (note: Performance degradation has been solved already)

- Further, the significant reduction in power and area provide sufficient headroom for monitoring NBTI effects.

## Questions? kodi@ohio.edu