# **1D-16**: A 52-mW 8.29mm<sup>2</sup> 19-mode LDPC Decoder Chip for Mobile WiMAX Applications

Xin-Yu Shih, Cheng-Zhou Zhan, Cheng-Hung Lin, An-Yeu (Andy) Wu

Graduate Institute of Electronics Engineering,

Department of Electrical Engineering,

National Taiwan University.

Jan. 20th, 2009

#### **Motivation**

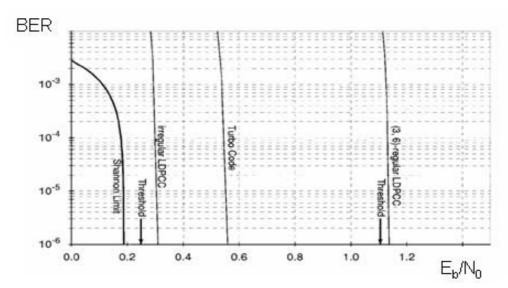

- ☐ First introduced by Gallager in 1962. [1]

- ☐ Rediscovered by MacKay In 1995. [2]:

- Excellent error-correcting performance near the Shannon limit.

- Highly parallel decoding scheme.

- □ Become more popular in advanced communication systems (Mobile WiMAX) with advanced VLSI technology.

1D-16 PP 2

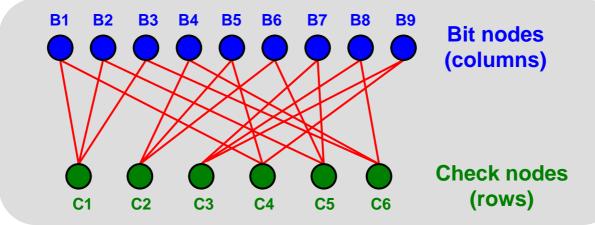

### **Low-Density Parity-Check Codes (LDPC)**

☐ Parity check matrix : very sparse matrix

☐ Bipartite graph

1D-16 \_\_\_\_\_\_ PP.

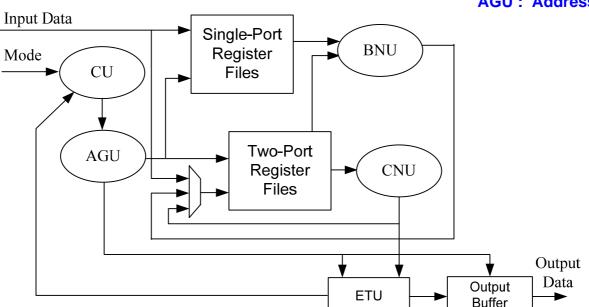

## **Proposed Design Techniques**

- ☐ Overlapped Operations of BNUs & CNUs

- □ New Early Termination Scheme

- ☐ Distributed Memory Banks

Mode

☐ Reconfigurable Architecture

**CU: Counter Unit**

AGU: Address Generator Unit

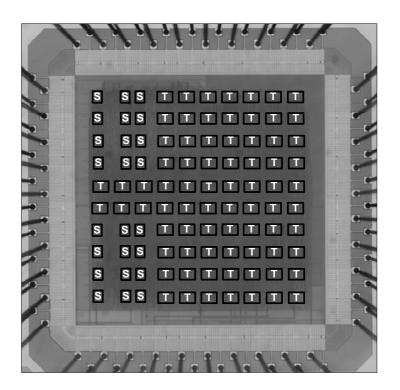

## **Efficient Checkerboard Layout Scheme (ECLS)**

- ☐ Divided memory bank (architecture)

- Activation of memory bank in need

- Small address decoder inside memory

- > Reduced power

- ☐ Distributed memory bank (physical)

- > Evenly data transmission

- > Lower routing complexity

- > Reduced area

## **Comparison Table**

|                      | JSSC'02              | ISCAS'05              | TCAS-I'06             | JSSC'06                  | This work                |

|----------------------|----------------------|-----------------------|-----------------------|--------------------------|--------------------------|

| Multi-mode           | No                   | No                    | No                    | 7 modes                  | 19 modes                 |

| Spec                 | (1024,512)           | (2048,1732)           | (1024,512)            | (2048,128*k)<br>k = 8~14 | (96*k, 48*k)<br>k = 6~24 |

| Code<br>Construction | Random               | RS-based              | QC-based              | Turbo-<br>Interleaved    | QC-based                 |

| Technology           | 0.16um               | 0.18um                | 0.18um                | 0.18um                   | 0.13um                   |

| Parallelism          | Fully                | Fully                 | Partial               | Partial                  | Partial                  |

| Iterations           | 64                   | 32                    | 8                     | 16                       | 2 ~ 8                    |

| Chip Area            | 52.5 mm <sup>2</sup> | 17.64 mm <sup>2</sup> | 10.08 mm <sup>2</sup> | 14.3 mm <sup>2</sup>     | 8.29 mm <sup>2</sup>     |

| Frequency            | 64 MHz               | 100 MHz               | 200 MHz               | 125 MHz                  | 83.3 MHz                 |

| Throughput           | 1 Gbps               | 3.2 Gbps              | 985 Mbps              | 640 Mbps                 | 30~111 Mbps              |

| Power                | 690 mW               | N/A                   | N/A                   | 787 mW                   | 52 mW                    |

1D-16

#### Conclusion

- ☐ An efficient IC strategy with four design techniques and efficient checkerboard layout scheme (ECLS).

- ☐ Features of our LDPC decoder design :

- ➤ Multi-mode design (19-mode)

- ➤ Smaller chip area (8.29mm²)

- ➤ Higher hardware utilization (50%→75%)

- ➤ Lower decoding latency (68.75%)

- ➤ Flexible decoding throughput (30Mbps~111Mbps)

- ➤ Lower power consumption (52mW @ 83.3 MHz)

1D-16 PP. 7