Department of Electronic and Computer Engineering

HKUST The Hong Kong University of Science and Technology

# Low Energy Level Converter Design for Sub-V<sub>th</sub> Logics

**Authors: Hui Shao and Chi-Ying Tsui**

Department of Electronic and Computer Engineering The Hong Kong University of Science and Technology Hong Kong SAR., P. R. China

## Introduction

- Sub-V<sub>th</sub> logic operations can reduce the circuit power consumption dramatically

- Voltage difference between different voltage domains

- Level converter (LC) is needed

- > Sub-V<sub>th</sub> digital core <-> I/O interface

- > Sub-V<sub>th</sub> digital core <-> analogue blocks ...

- Conventional LC can not operate for sub-V<sub>th</sub> input signal

- NMOS sub-V<sub>th</sub> conducting current cannot overcome the PMOS current

- ► Output cannot be pulled down

- Positive feedback cannot be triggered

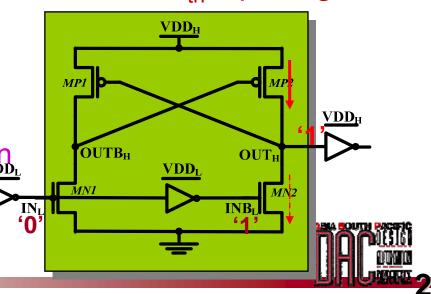

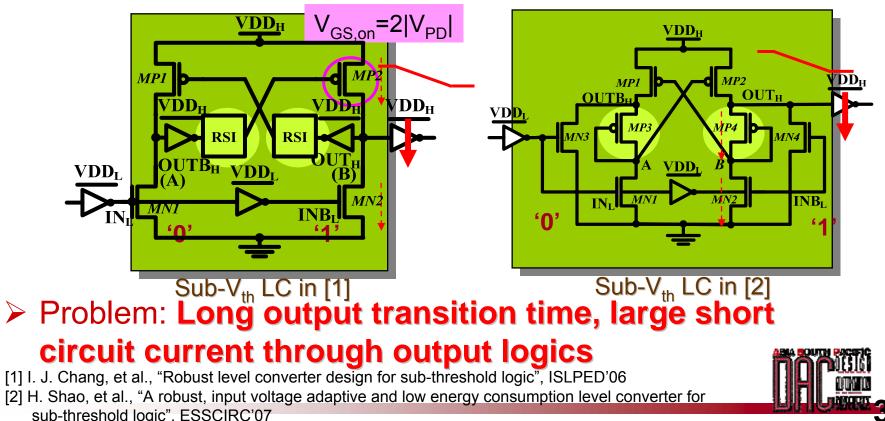

# **Previous Sub-V<sub>th</sub> LC Designs**

- Limit the PMOS current so that the NMOS sub-V<sub>th</sub> conducting current can trigger the positive feedback

- ► LC in [1]: RSI to limit the PMOS |V<sub>GS</sub>| voltage

- ► LC in [2]: PMOS diodes to limit the PMOS pull up strength

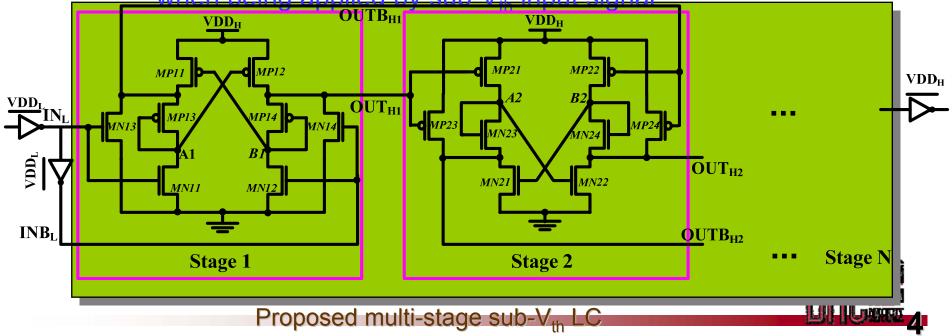

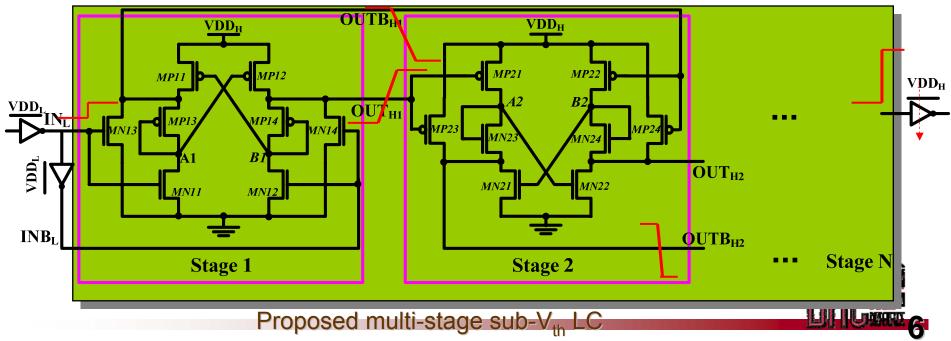

# **Proposed Multi-stage Sub-V<sub>th</sub> LC**

#### Circuit structure:

Odd stage: previously proposed sub-V<sub>th</sub> LC in [2]

> Output '0'→'1' transition is always earlier than '1' to '0' transition when being applied by sub-V<sub>th</sub> input signal

Even stage: sub-V<sub>th</sub> LC with upside down connections

> Output '1'→'0' transition is always earlier than '0' to '1' transition when being applied by sub-V... input signal

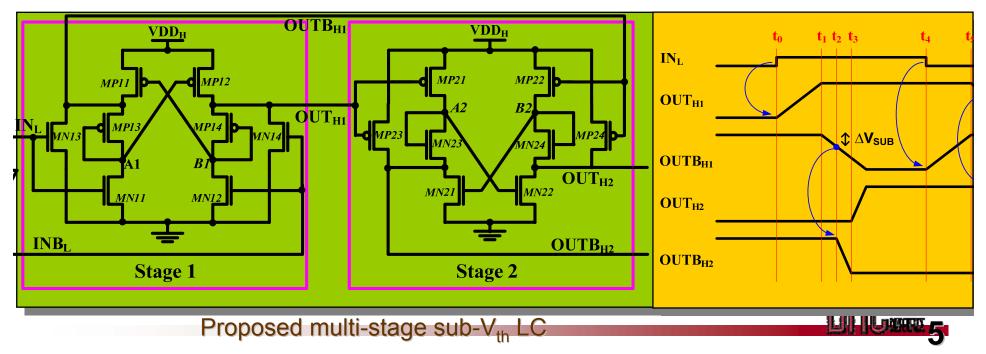

# **Operation of Multi-stage Sub-V<sub>th</sub> LC**

- $t_0$ :  $IN_L$  changes from '0' to sub- $V_{th}$  '1'.

- $t_1$ : OUT<sub>H1</sub> goes firstly to VDD<sub>H</sub>.

MP21,MP23 off, Short circuit current though the left branch of the 2nd stage is eliminated.

- t<sub>2</sub>: OUTB<sub>H1</sub> keeps being discharged which triggers the positive feedback in 2nd stage

OUTB<sub>H2</sub> is pulled down by the positive feedback in 2nd stage.

MN22 off. Short circuit current through the right branch of the 2nd stage is greatly reduced.

- $t_3$ : OUTB<sub>H1</sub> keeps decreasing.

Output of the 2nd stage flips faster than that of 1st stage.

## **Operation of Multi-stage Sub-V<sub>th</sub> LC**

Operation of the multi-stage LC

- 1<sup>st</sup> stage: convert sub-V<sub>th</sub> signal to nominal high voltage

- 2<sup>nd</sup>-N<sup>th</sup> stages: Sharpen the LC output with positive feedback in each stages

- The energy overhead due to multi-stage structure is small

Circuit total energy reduction (incl. output logics) is reduced

## **Experimental Results**

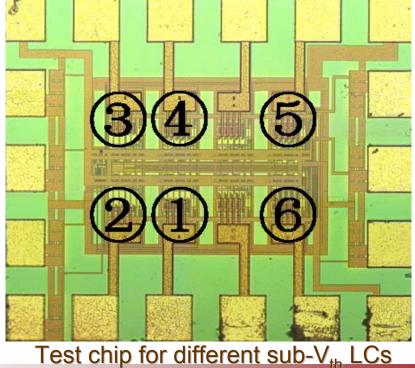

➢ Different sub-V<sub>th</sub> LCs were designed (TSMC 0.18 µm)

Same transistor sizes for different LC schemes

sub-V<sub>th</sub> LC in [1]

sub-V<sub>th</sub> LC in [2]

④proposed 3-stage sub-V<sub>th</sub> LC

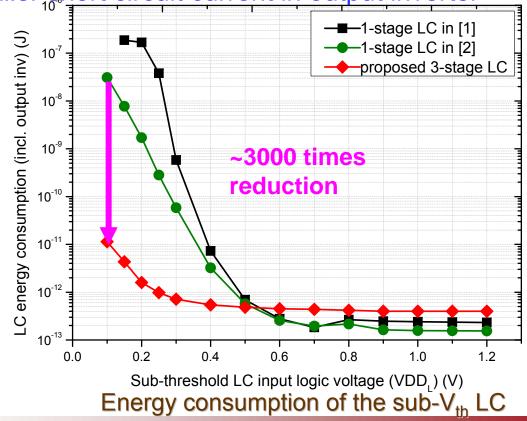

#### **Measurement Results**

- A typical sized inverter is connect to LC output, and the short circuit energy consumption is included

- Multi-stage LC has a lower energy than single stage LC

- > Smaller short circuit current in output inverter

### **Experimental Results**

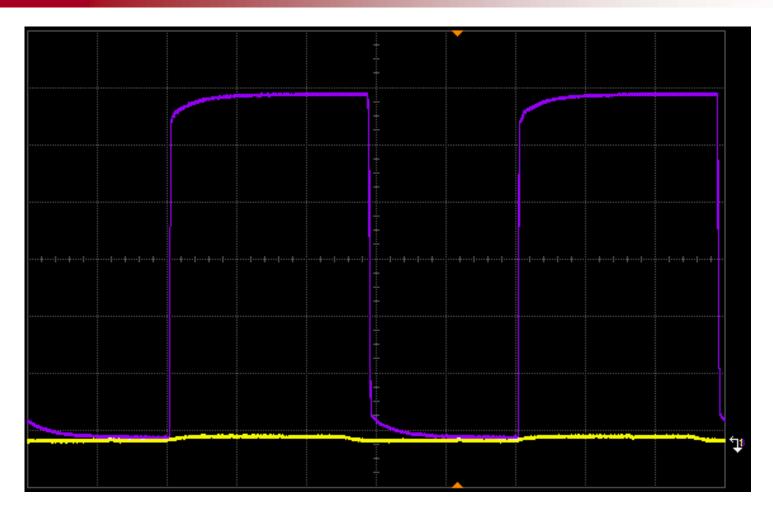

Input (100mV) and output (1.8V) waveforms of the proposed 3-stage sub- $V_{th}$  LC (measurement)