#### ASP-DAC 2009

# Fast False Path Identification Based on Functional Unsensitizability Using RTL Information

Presenter Yuki Yoshikawa<sup>1</sup>

Satoshi Ohtake<sup>2</sup>, Tomoo Inoue<sup>1</sup> and Hideo Fujiwara<sup>2</sup>

<sup>1</sup> Hiroshima City University, Japan

<sup>2</sup> Nara Institute of Science and Technology, Japan

\*This work has been supported in part by STARC

## Outline

Background

- False path

- Adverse effect of false paths

- Over-testing of delay faults

- Inaccurate estimation of a system clock period

Our proposed method

False path identification using RTL information

Experimental result

Conclusion

For high performance VLSIs,

- high quality delay fault testing, and

- accurate estimation of a circuit delay is an important issue

False paths interfere

- accurate timing delay testing

- -Over-testing

- accurate estimation of a system clock period

- Degradation of circuit performance

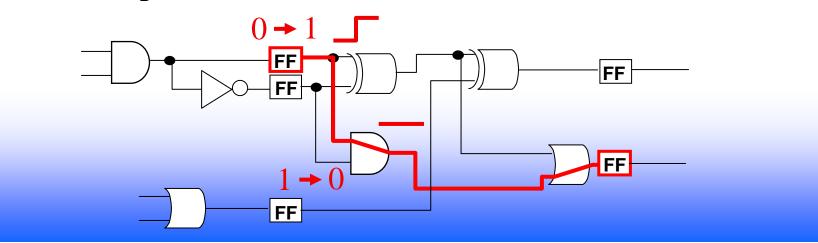

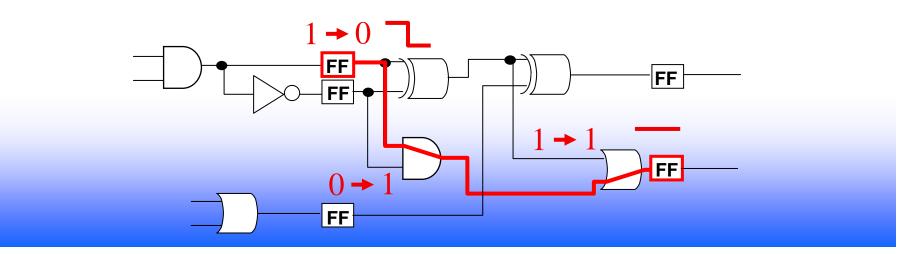

No transition occurs at the start point of a path, or a transition at the start never reaches the end of the path, or the captured value at the end is never propagated to any PO

- Path delay faults on a false path are untestable

- Transition faults are not activated along a false path

- The propagation delay on a false path does not affect its circuit performance

No transition occurs at the start point of a path, or a transition at the start never reaches the end of the path, or the captured value at the end is never propagated to any PO

- Path delay faults on a false path are untestable

- Transition faults are not activated along a false path

- The propagation delay on a false path does not affect its circuit performance

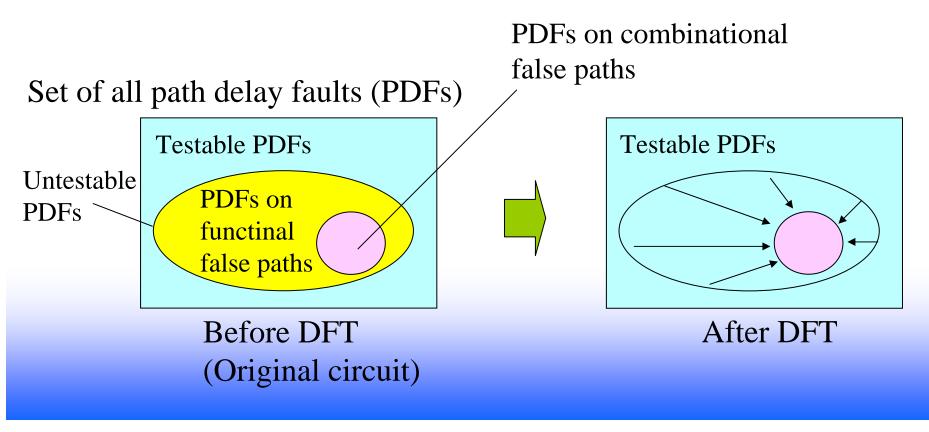

#### Over-testing

- To test faults that are untestable in an original circuit

- It induces yield loss, futile test generation time and futile test application time

A strategy for over-testing reduction

- False path identification for an original circuit

- Exclusion of PDFs on the identified false paths from the target of testing

To reduce over-testing, it is important to identify as many false paths as possible with small computational time

7

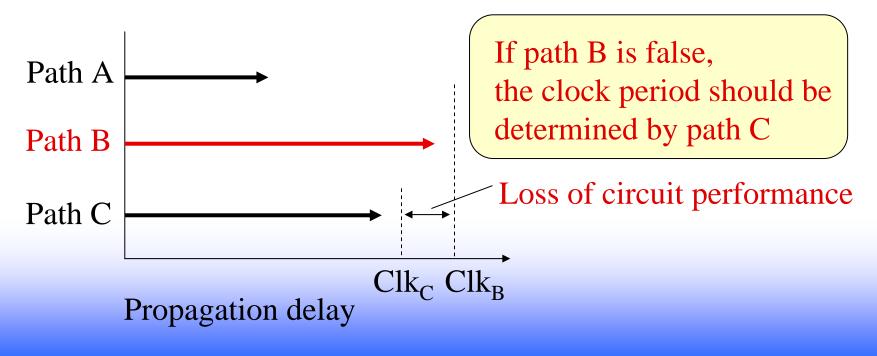

The system clock period of a circuit is determined according to the propagation delay on the longest path

If the longest path in a circuit is false, the system clock period is inaccurately determined, and thus the maximum performance is missed

Gate-level false path identification

- For combinational circuit [Cheng'96], [Kajihara'97], [Reddy'01]

- For sequential circuit [Kristic'96]

GL approaches would take much time to handle many paths

### RT-level false path identification

False path identification using RTL information and its application to over-testing reduction for delay faults [Yoshikawa'07]

The method identifies non-robust untestable paths at RTL The time required for the identification is much faster than GL • Our objective is to identify false paths at RTL based on functional unsensitizability of PDFs

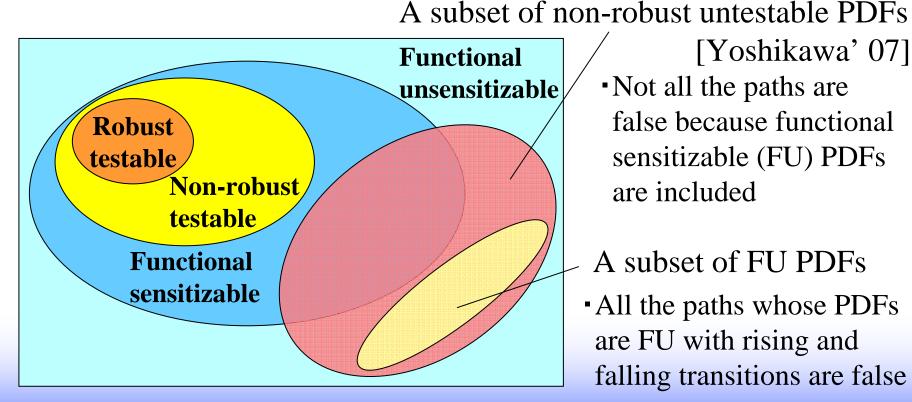

Path delay fault classification [K. T. Cheng]

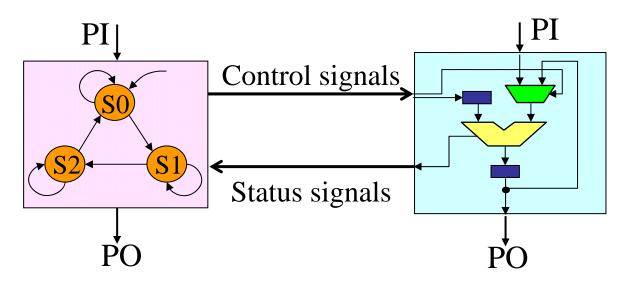

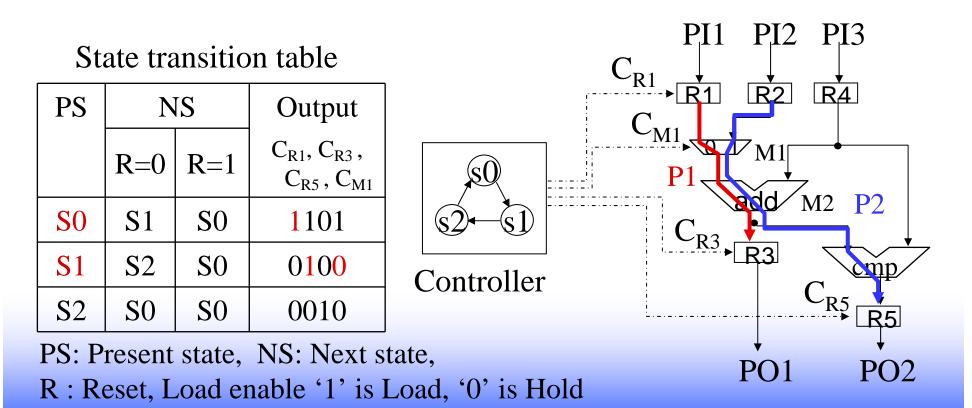

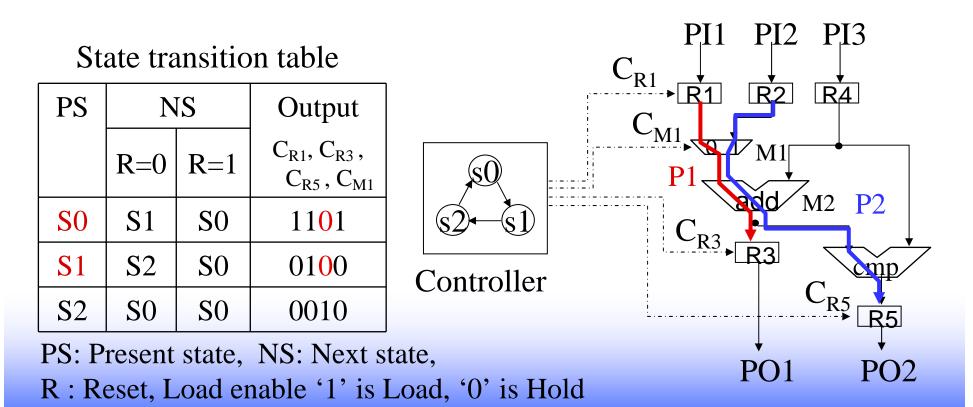

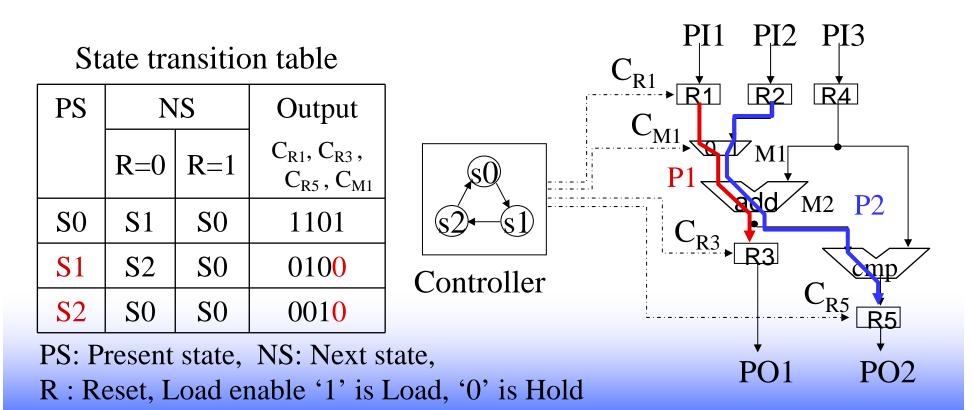

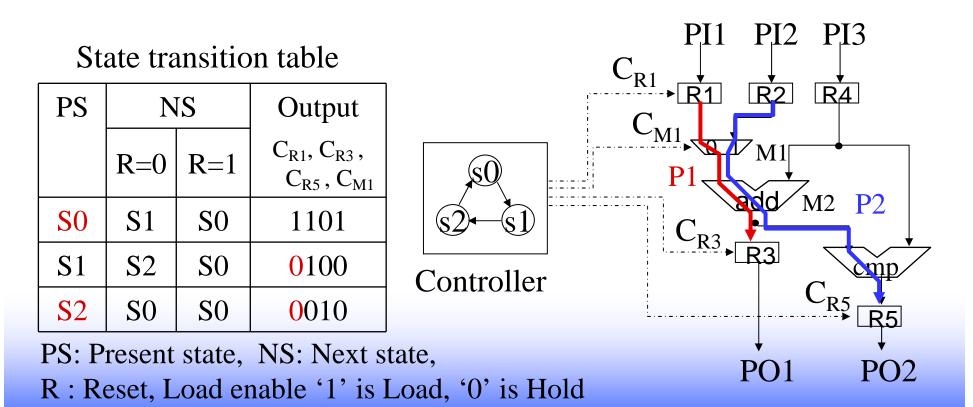

Controller

- Represented by an FSM

- State transitions are completely specified

Data path

Represented by interconnection of registers, multiplexers and combinational operation modules

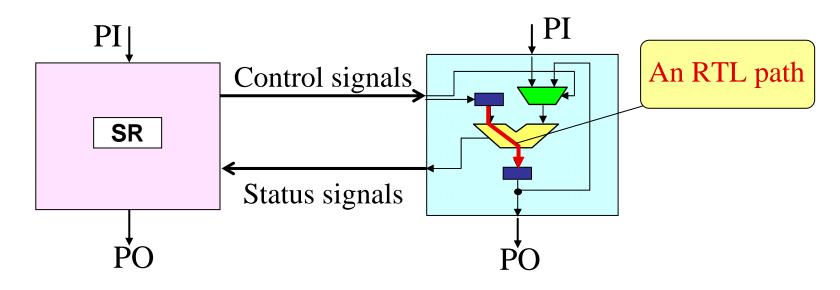

#### RTL path

- starts from a register or a PI and ends at a register or a PO

- only passes through combinational modules

- is a bundle of gate-level paths

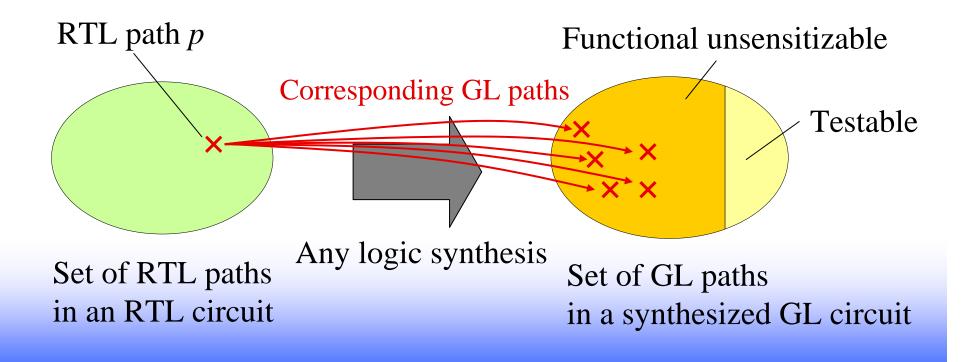

## RTL functional unsensitizable (RTL-FU) path

#### RTL-FU path

An RTL path *p* is RTL-FU if all gate-level paths corresponding to *p* are functional unsensitizable for any logic synthesis

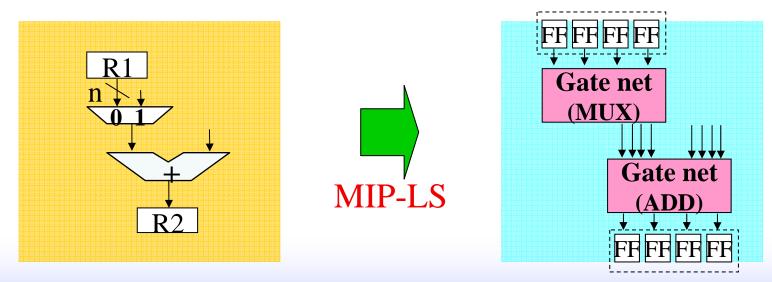

To clarify the correspondence between an RTL path and its GL paths, we consider Module Interface Preserving Logic Synthesis (MIP-LS)

It transforms each RTL module and RTL signal line into its own gate-level netlist and single-bit signal lines

A mapping from an RTL path to its GL paths is also proposed [Iwata' 08]

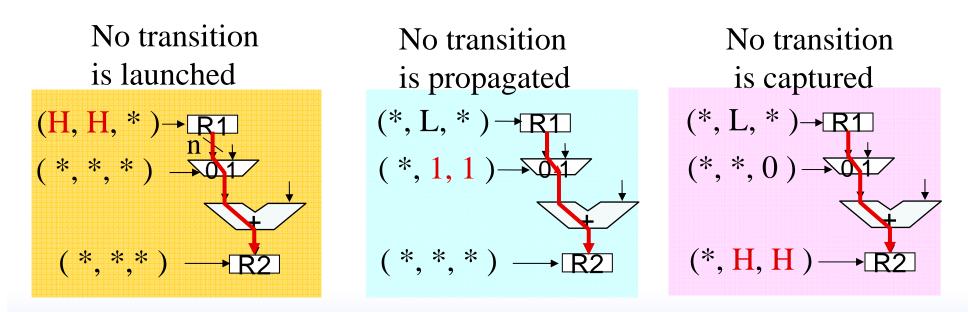

An RTL path *p* is RTL-FU if at least one of the following three conditions is satisfied for any state transition

(H: Hold, L: Load, \*: L or H or 0 or 1)

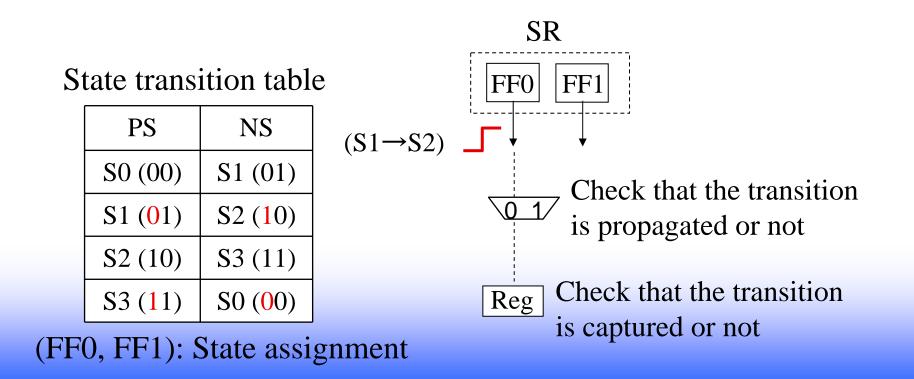

For each FF(SR-ff) in an SR,

by considering a state assignment and state transitions, we can know the time when a transition occurs

- Evaluate the number of RTL paths that are identified as RTL-FU by our method

- Evaluate the number of gate-level paths that are corresponding to the identified RTL-FU paths

|         | Bit   |        |         | Area        | # RTL paths |             |  |

|---------|-------|--------|---------|-------------|-------------|-------------|--|

| Circuit | width | # Regs | #States | NOT gate: 2 | DR to DR    | SR-ff to DR |  |

| Tseng   | 8     | 7      | 5       | 2,975       | 20          | 42          |  |

| Paulin  | 8     | 8      | 6       | 3,391       | 29          | 67          |  |

| JWF     | 8     | 15     | 8       | 4,758       | 153         | 408         |  |

| MPEG    | 8     | 241    | 163     | 77,554      | 651         | 2,152       |  |

| RISC    | 32    | 39     | 10      | 81,086      | 10,181      | 38,122      |  |

Circuit characteristics of benchmarks

## Number of RTL paths identified as RTL-FU

|         | DR     |      |       | SR-ff: Rise |        |        | SR-ff: Fall |        |        |

|---------|--------|------|-------|-------------|--------|--------|-------------|--------|--------|

| Circuit | #RTL   | #RTL | #RTL  | #RTL        | #RTL   | #RTL   | #RTL        | #RTL   | #RTL   |

| (RTL)   | path   | FU   | NRU   | path        | FU     | NRU    | path        | FU     | NRU    |

| Tseng   | 20     | 2    | 6     | 42          | 5      | 13     | 42          | 6      | 11     |

| Paulin  | 29     | 0    | 13    | 67          | 17     | 25     | 67          | 19     | 30     |

| JWF     | 153    | 69   | 119   | 408         | 172    | 285    | 408         | 226    | 319    |

| MPEG    | 651    | 0    | 32    | 2,152       | 0      | 64     | 2,152       | 0      | 64     |

| RISC    | 10,181 | 707  | 1,233 | 38,122      | 28,217 | 28,411 | 38,122      | 15,176 | 18,968 |

•DR: RTL paths starting from registers in a data path

•SR: RTL paths starting from FFs of the state register in a controller

•RTL-NRU (Non-robust untestable): identified by our previous method

For JWF and RISC, many RTL paths were identified as RTL-FU

For MPEG, there is no RTL paths identified as RTL-FU

The time required for identifying RTL-FU paths is a few seconds

#### Number of GL paths corrsp. to identified RTL-FU paths

|         | DR      |              |              | SR-ff     |                |                | Total          |         |                |

|---------|---------|--------------|--------------|-----------|----------------|----------------|----------------|---------|----------------|

| Circuit | #GL     | #GL          | #GL          | #GL       | #GL            | #GL            | #GL            | #GL     | #GL            |

| (Gate)  | path    | FU           | NRU          | path      | FU             | NRU            | path           | FU      | NRU            |

| Tseng   | 13,056  | 534          | 5,910        | 944       | 139            | 465            | 14,000         | 673     | 6,375          |

| Paulin  | 96,912  | 0            | 41,278       | 95,310    | 24,135         | 39,434         | 192,232        | 24,135  | 80,712         |

| JWF     | 60,150  | 12,710       | 18,182       | 101,622   | 53,064         | 79,404         | 161,772        | 65,774  | 97,586         |

| MPEG    | 833,696 | 0            | 2,048        | 2,602,624 | 0              | 70,624         | 3,436,320      | 0       | 72,672         |

| RISC    | 57.6 B  | 2.1 <i>B</i> | 3.8 <i>B</i> | 223.7 B   | 140.8 <i>B</i> | 141.4 <i>B</i> | 281.3 <i>B</i> | 142.9 B | 145.2 <i>B</i> |

•We extracted #GL paths of RISC under the constraint of PrimeTime.

•Unit *B* means Billion

- For Paulin and JWF, our method identified 24,135 (13%) and

65,774 (41%) GL FU paths within 1 second

- For RISC, 142.9 billion GL FU paths were identified by our proposed method within 10 seconds

- For Paulin, it takes 50 hours to identify 10,000 as NRU by TetraMax

We have proposed a method for identifying functional unsensitizable paths using RTL information

- The identified paths are false paths

- The time required for identification is much faster than GL approaches

24

The information of the identified false paths can be used in order to reduce over-testing, and area and performance optimization during logic synthesis RTL path p is RTL-FU if at least one of the following four properties is satisfied for any consecutive two cycles t and t+1

- No transition is launched at the output of the start register Rs in cycle t irrespective of the delay of the load-enable signal applied to Rs and/or input data delivered to Rs

- Even if a transition is launched at Rs, it never reachesthe end register Re along p in cycle t+1 irrespective of the delay of the off-inputs on p

- The reached value is never captured into Re in cycle t+1 irrespective of the delay of the load-enable signal applied to Re

- The captured value of Re at cycle t+1 never affects any PO at the latter cycles irrespective of the delay of the off-inputs of RTL modules on all the propagation paths from Re to any PO