Defect-Aware Thresholder in the Sense Amplifier of Nanowire Crossbar Memories

14<sup>th</sup> Asia and South Pacific Design Automation Conference – ASPDAC January 22, 2009 – Yokohama, Japan

> M. Haykel Ben Jamaa, David Atienza Yusuf Leblebici, Giovanni De Micheli

Ecole Polytechnique Fédérale de Lausanne (EPFL)

# **Motivation**

- Silicon nanowire crossbar circuits are a promising post-CMOS candidate:

- Higher density

- Regular organization

- Multiple functions

- Interfacing the nanowire crossbars and the rest of the CMOS chip is still challenging:

- Bridging the scales is not reliable

- Crossbar circuits need special test procedures

- Decoder test is required

### Outline

- Introduction

- Decoder Test

- Current Variability Model

- Simultation Results

- Conclusions

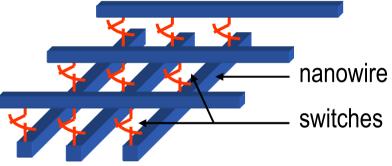

# **Organization of Nanowire Crossbars**

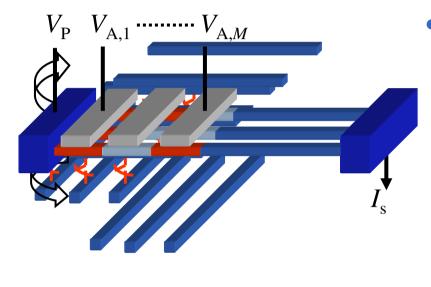

- Two parts of the crossbar circuit [DeHon'03]:

- Crosspoints: functional region

- Decoder: interfacing CMOS⇔SiNW

## **Nanowire Decoders**

- Task of the decoder: unique addressing of every nanowire by the outer CMOS circuit.

- Matching the sub-lithographic to lithographic pitch is technologically expensive.

- Cost-efficient and CMOS-compatible decoders generally provide a stochastic addressing.

- Unpredicted number of nanowires with a given address: axial [DeHon'03], radial [Savage'06], random contact decoder [Hogg'06]

- Unpredictable threshold voltage (V<sub>T</sub>) of access transistors: axial, mask-based [Beckman'05], gate-all-around decoders [Ben Jamaa'07]

# **Decoder Variability**

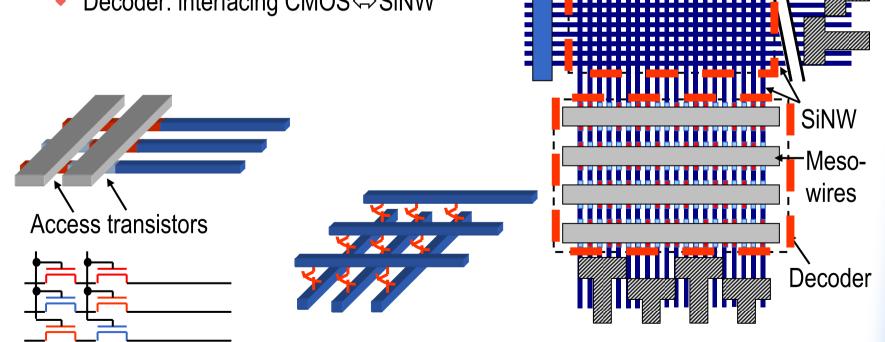

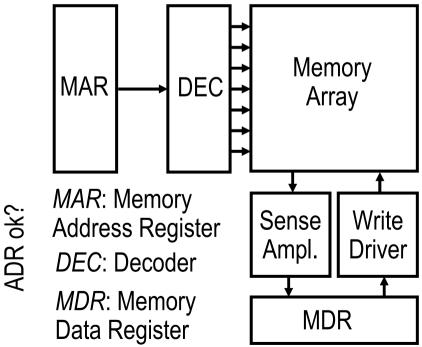

• Current-based memory operations [Cerofolini'07]

# **Testing Nanowire Decoders**

- Variability of  $V_{\rm T} \rightarrow$  pattern sensitivity faults

- Expensive functional testing [Abadir'83, Adams'03].

- Efficient algorithms for crossbar memories?

- Reducing memory test complexity by first testing decoder

- Challenges:

- How can we test nanowire array decoders?

- What are the thresholder design constraints?

- How do design and test mutually influence on each other?

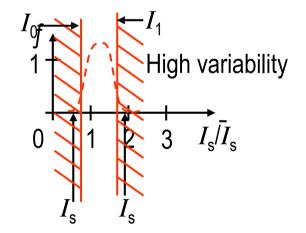

### Variability-Induced Decoder Errors

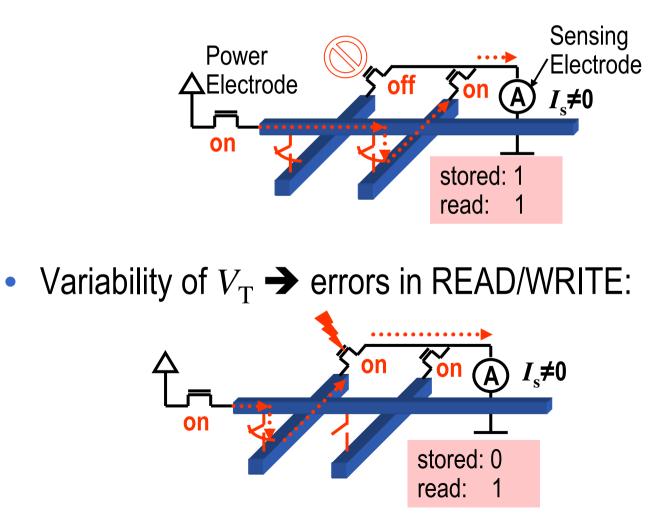

- In the absence of variability, sensed current  $I_s$  fixed value  $\bar{I}_s$

- With high variability, *I*<sub>s</sub> follows a stochastic distribution *f*:

- Single NW addressed, but current lower than noise level

- Single NW addressed, but current higher than level of 2 NWs

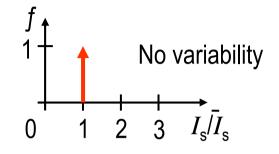

# **Bootstrap Decoder Test**

- Linear complexity

- No additional physical resources

## **Test Quality**

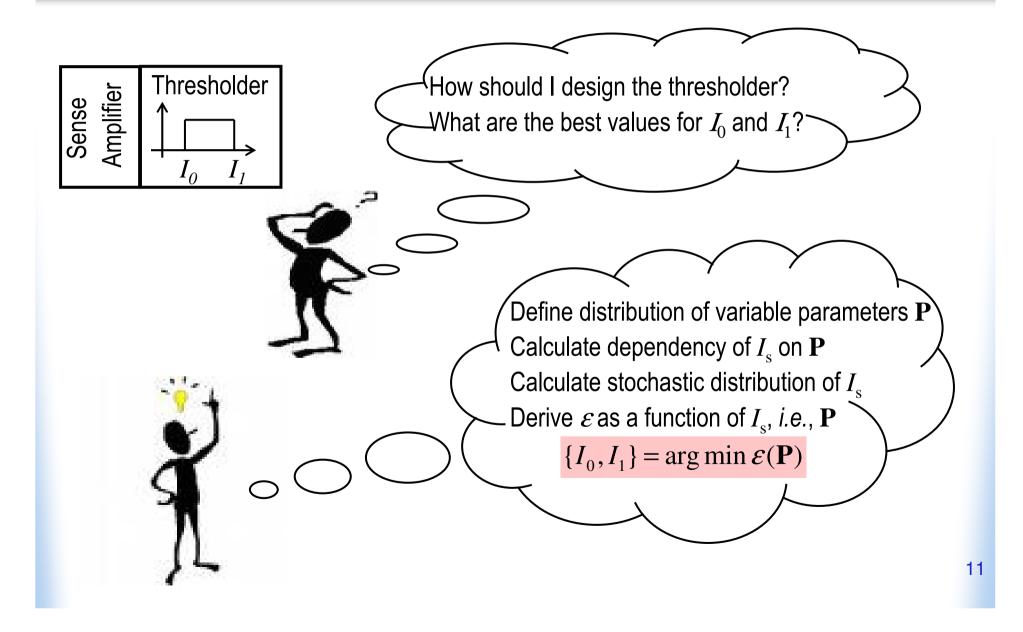

- Thresholder must identify absence of addressed NWs:

- Maximize  $Pr_1 = Pr \{I_s < I_0, \text{ given that: } I_s \text{ delivered by } = 0 \text{ NW} \}$

- Thresholder must identify uniquely addressed NWs:

- Maximize  $Pr_2 = Pr \{I_0 \le I_s \le I_1, \text{ given that: } I_s \text{ delivered by } = 1 \text{ NW} \}$

- Thresholder must identify unintentionally addressed NWs:

- Maximize  $Pr_3 = Pr \{I_1 < I_s, \text{ given that: } I_s \text{ delivered by } \ge 2 \text{ NW}\}$

- The best test maximizes all 3 events → test quality improves by minimizing test error defined as:

$$\mathcal{E} = 1 - \Pr_1 \times \Pr_2 \times \Pr_3$$

#### **Test-Aware Thresholder Design**

# **Variability of Circuit Under Test**

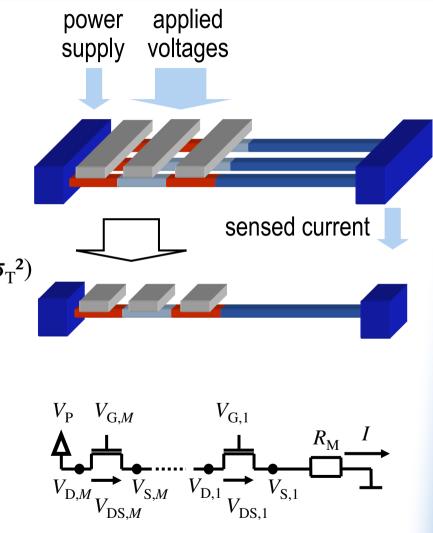

- Circuit under test:

- Full NW layer

- Defect-free case: 1 NW

- Circuit reduced to a series of M transistors and a resistor R<sub>M</sub>

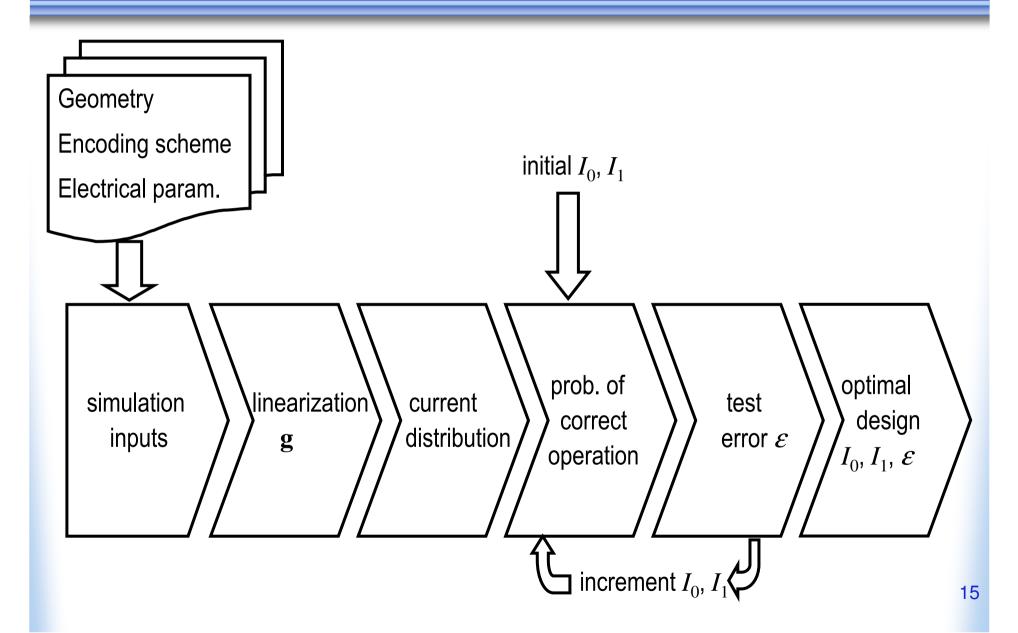

- Model parameters:

- Gaussian parameters:  $V_{T,i} \sim N(V_T^{OP}, \sigma_T^2)$

- Model-fixed parameter: R<sub>M</sub>

- Extrinsic parameter:  $V_{\rm P}$

- Variability model:

- Sensitivity analysis:  $I=I^{OP}+\delta I$

- Linearization:  $\partial I = \mathbf{g}^{\mathsf{T}} \cdot \partial V_{\mathsf{T}}$

- Small signal conductance vector g

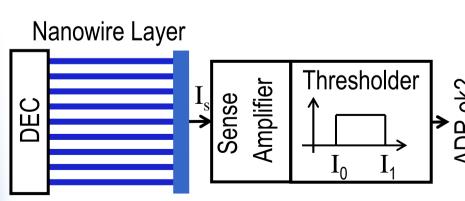

#### **Current Components**

- Array of *N* nanowires

- Current through the NW array:

- $I_{\rm u}$ : Useful signal caused by a single addressed NW

- $I_{\rm in}$ : Intrinsic noise caused by  $N_{\rm in}$  non-addressed NWs

- $I_{dn}$ : Defect-induced noise caused by  $N_{dn}$  badly addressed NWs

# **Distribution of Current Components**

- Useful signal:

- *I*<sub>on</sub>: on-current

$$I_{\rm u} \propto N(I_{\rm on}, \|\mathbf{g}\|^2 \sigma_{\rm T}^2)$$

- Intrinsic noise:

- *I*<sub>off</sub>: off-current

$$I_{\rm in} = N_{\rm in} \times I_{\rm off}$$

- Defect-induced noise:

- Defects in NW *i* described by  $\mathbf{s}_i$

- N<sub>di</sub> defective NWs shift mean value, and increase std-deviation

#### **Simulation Flow**

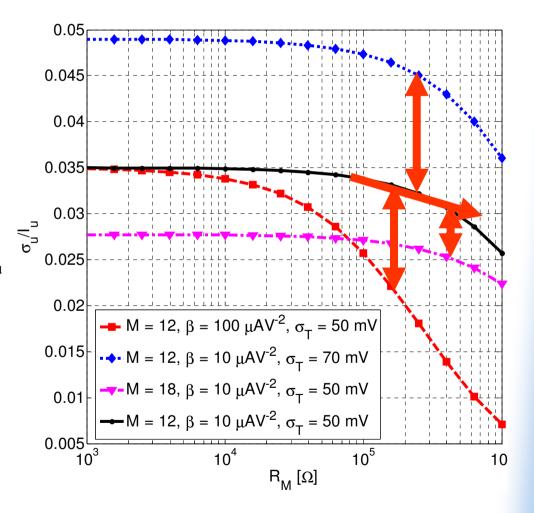

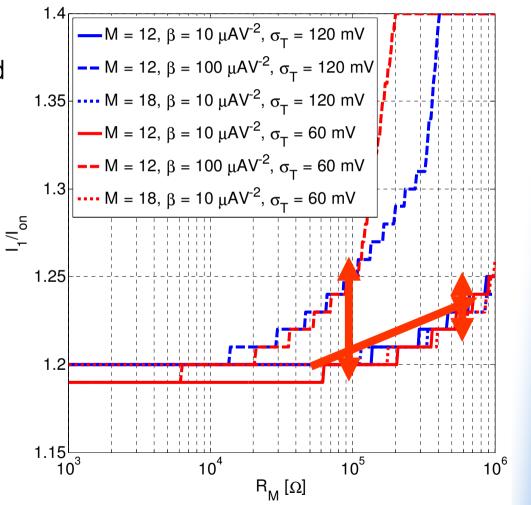

## **General Signal Variation**

- Distribution of  $I_u$  and  $I_{di}$  with similar qualitative behaviours

- $I_{\rm u}$  distribution improves with:

- $R_{\rm M}$   $\uparrow$ :  $\sigma_{\rm u}$  decreases faster than  $\bar{I}_{\rm u}$

- $\beta \uparrow$ : higher current injection

- $\sigma_{\rm T}\downarrow$ :  $\sigma_{\rm u}$  scales linearly with  $\sigma_{\rm T}$

- $M \uparrow$  :  $\sigma_{\rm u} \sim 1/\sqrt{M} \downarrow$  faster than  $\bar{I}_{\rm u}$

# **Thresholder Parameters**

- Influence of parameters:

- β: weak 10× → 4%

- $R_{\rm M}$ : stronger only if combined with  $\beta \rightarrow$  unlikely

- M: weaker

$I_1 \approx 1.2 \times I_{\rm on}$

- Fixing range of  $I_0$ :

- Not too small to filter noise

- Not too large to detect useful signal

$I_0 \approx 0.7 \times I_{\rm on}$

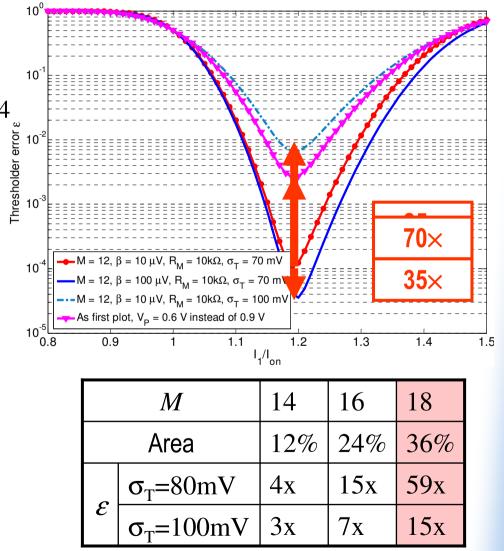

#### **Test Error**

- Typical parameters:: *E* ~10<sup>-4</sup>

Impact of parameters on *E*

- Impact of parameters on  $\mathcal{E}$ .

| Parameter                     | $I^{\mathrm{OP}}$ | δI                     | Impact  |

|-------------------------------|-------------------|------------------------|---------|

| $V_{ m P}\downarrow$          | $\rightarrow$     | _                      | 8       |

| $\sigma_{_{ m T}}$ $\uparrow$ | _                 | 1                      | 8       |

| β ↑                           | 1                 | _                      | 0       |

| $M\uparrow$                   | $\downarrow$      | $\downarrow\downarrow$ | $\odot$ |

# Conclusions

- Decoder test necessary to reduce crossbar memory test complexity caused by decoder variability

- Stochastic and perturbative current model used to quantify test error

- Robust thresholder against technology and parameter variation

- Typical test error ~10<sup>-4</sup>, better test with higher supply voltage, stronger access devices and redundant decoder design