#### Challenges to EDA System from the View Point of Processor Design and Technology Drivers

Mitsuo Saito

#### Chief Fellow / VP Engineering Toshiba Corporation Semiconductor Company

## Contents

- Semiconductor Technology and Microprocessor Trend

- Our Processor Design Experiences

- Early Struggles for Processor Design

- Meet with Playstation

- Development of Graphics and Emotion Engine for Playstation 2

- Towards Cell Broadband Engine (Cell)

- Development of Cell Processor

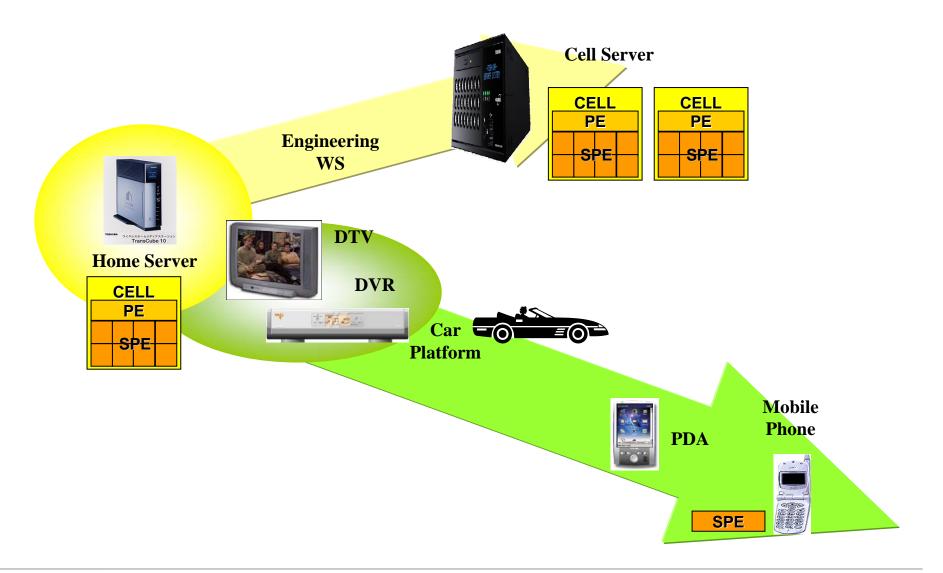

- Targets of Cell Processor

- Towards SpursEngine

- What is SpursEngine

- Makimoto's Wave and What we have done?

- Historical Analysis of Development

- Today's Situation and Challenge to EDA system

- What is necessary now?

- What will happen next?

- Summary

TOSHIBA

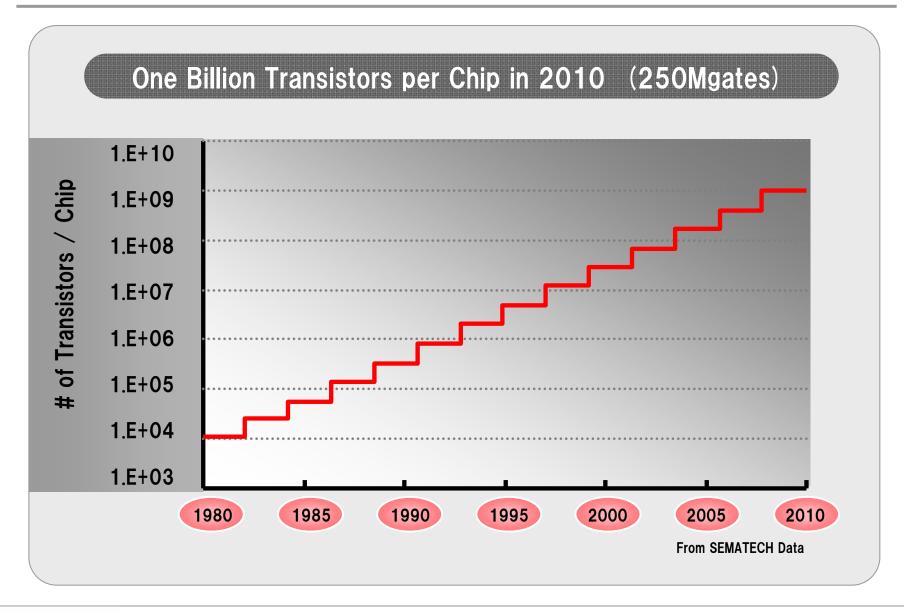

#### Still Semiconductor Roadmap is Working : Moore's Law

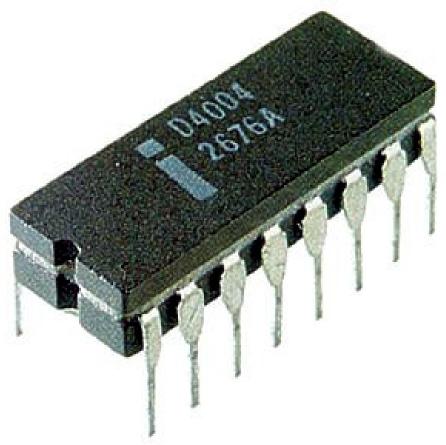

#### First Micro Processor was born in 1971

- Intel 4004

- DIP16P, Address bus 12 bit, Data bus 4 bit

- Clock 741KHz

- P-MOS 10um

- 🔳 Tr. 2300

- 🔳 11/15/1971

#### From : Wikipedia

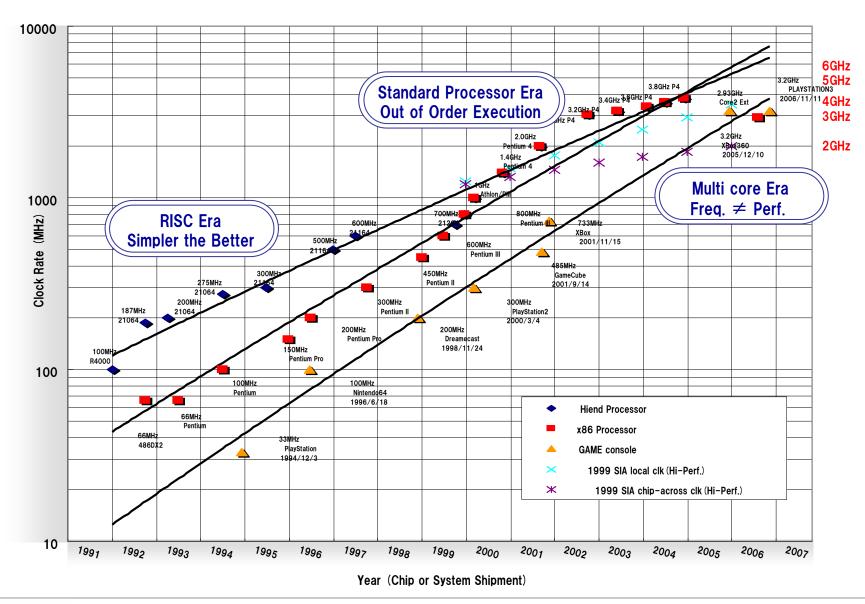

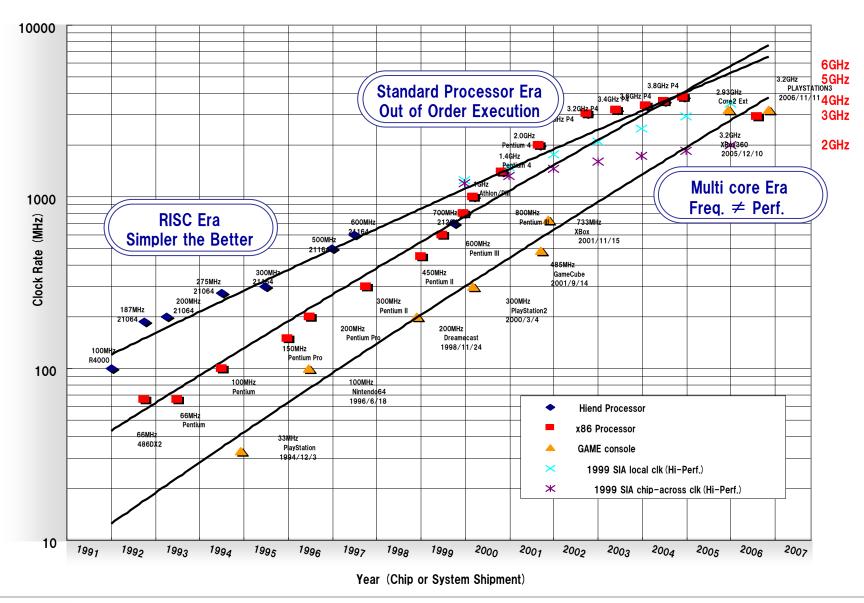

#### **Processor Clock Rate per Year**

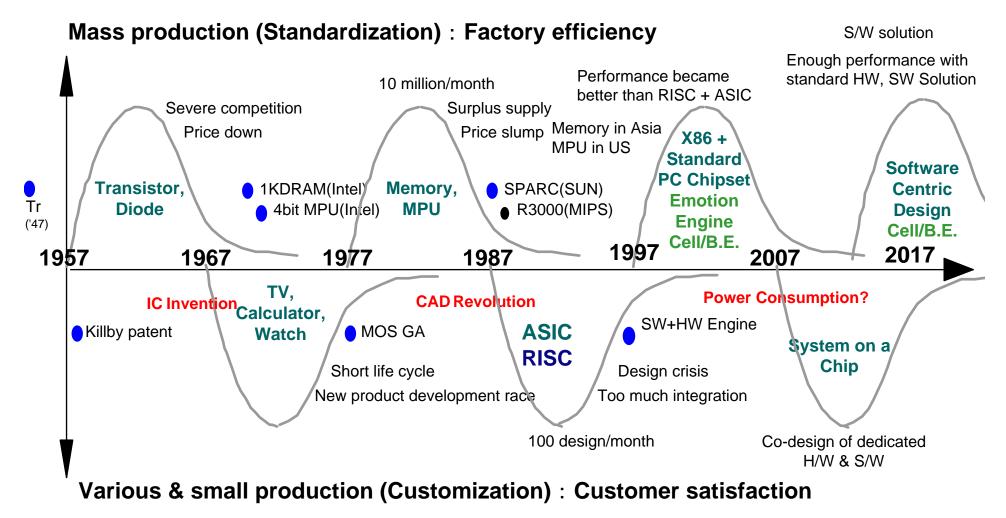

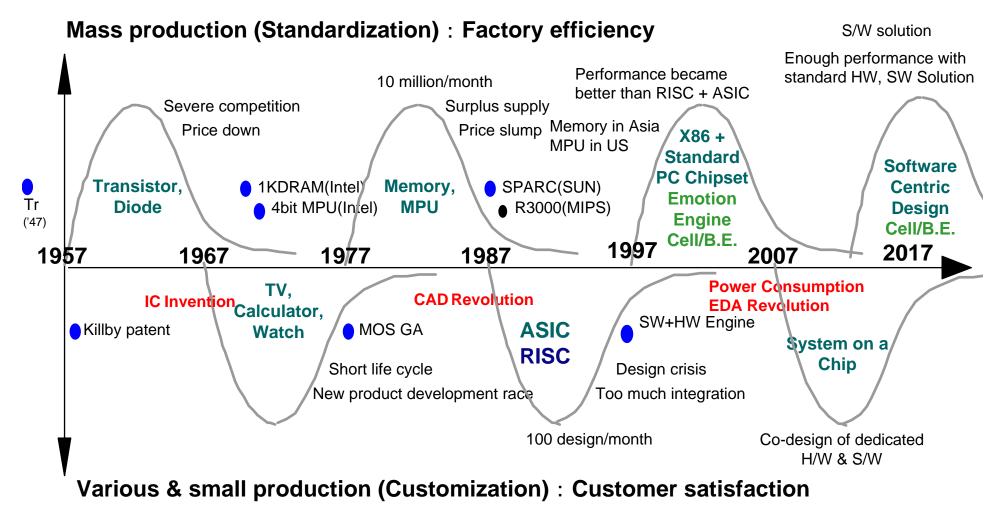

#### Waves to Standardization and Customization

Source : Makimoto' s Wave

TOSHIBA

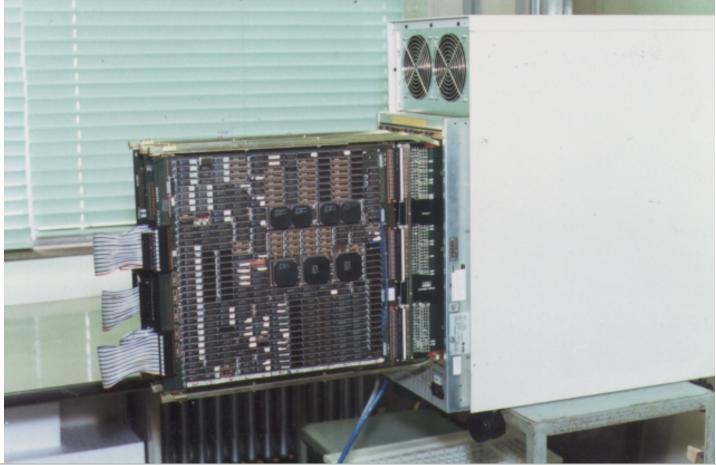

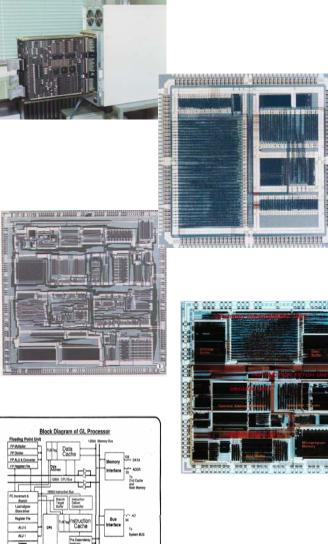

## AI Workstation (1986)

- Maybe the last paper and pencil based Design!

- Processor was a board based

- About 100 sets were sold, and reasonable revenue

## Al Processor Chip (1988)

•Silicon Compiler "Genesil" was Used

Performance 12 MIPS @Dhrystone Registers  $32bit \times 32$  $32bit \times 2$ Buses Bus Cycle 1 Clock min Clock Freq. 16MHz Max 1.2um 2 Layer Process Metal CMOS Tr.Cnt 113K 299pin PGA Package

TOSHIBA Leading Innovation >>>

## First TRON Processor TX1 (1988)

#### •Proprietary HDL (H<sup>2</sup>DL) was used

| Performance 5 MIPS |                                            |

|--------------------|--------------------------------------------|

| Registers          | 32bit × 16                                 |

| Buses              | 32bit × 2                                  |

| Bus Cycle          | 2 Clock min                                |

| Clock Freq.        | 25MHz Max                                  |

| Process            | 1.0um 2 Layer<br>Metal CMOS<br>155-pin PGA |

| Package            |                                            |

|                    |                                            |

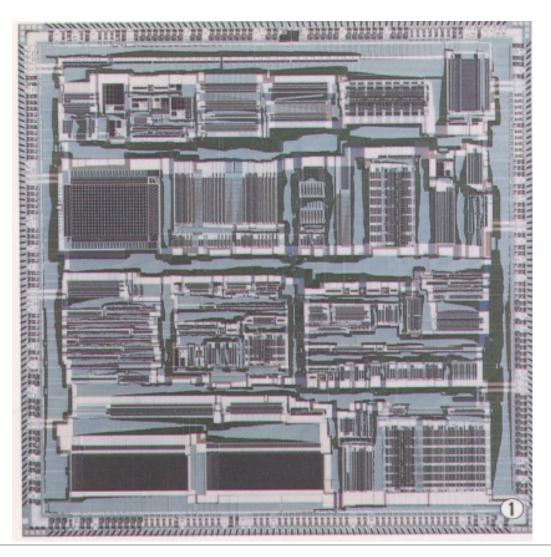

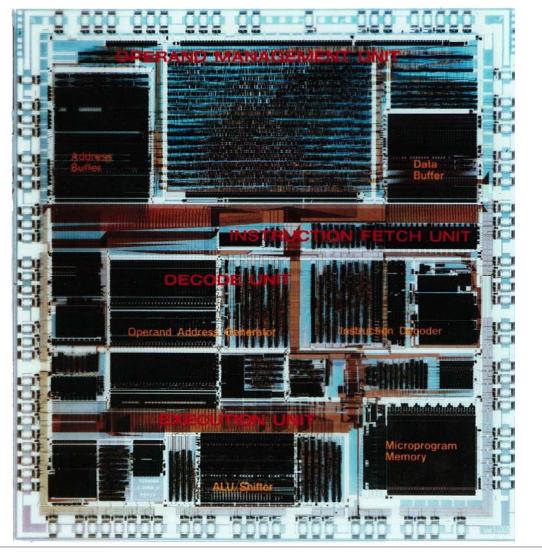

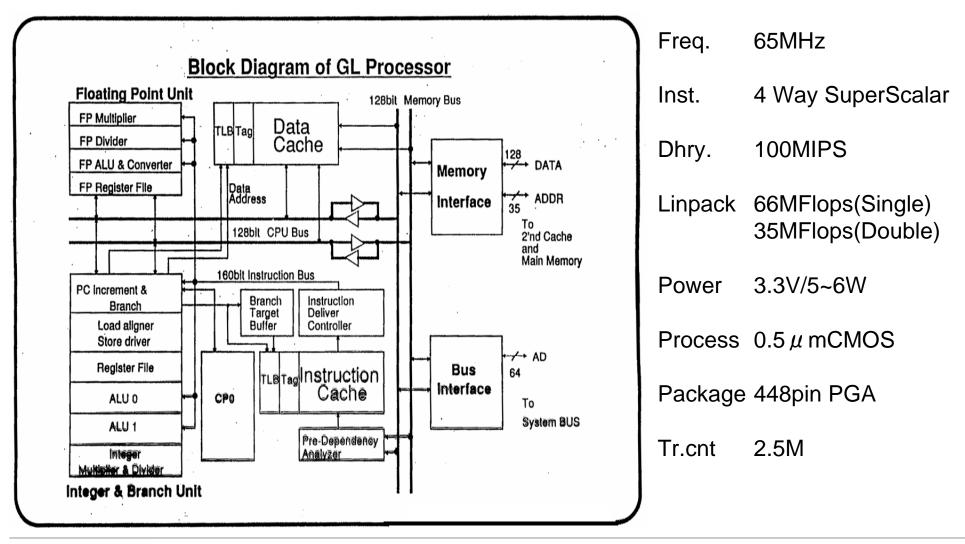

# Incomplete GL Processor (1990)

#### •Proprietary HDL (H<sup>2</sup>DL) was used

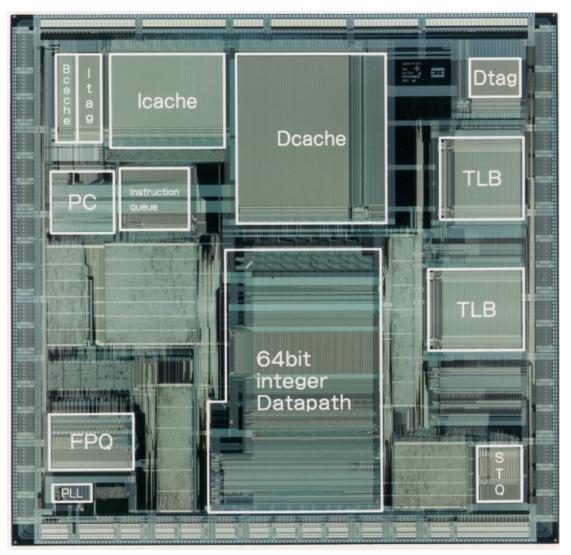

## **RISC Processor R8000 (1993)**

#### •Verilog was used

Jointly developed with Silicon Graphics Inc.

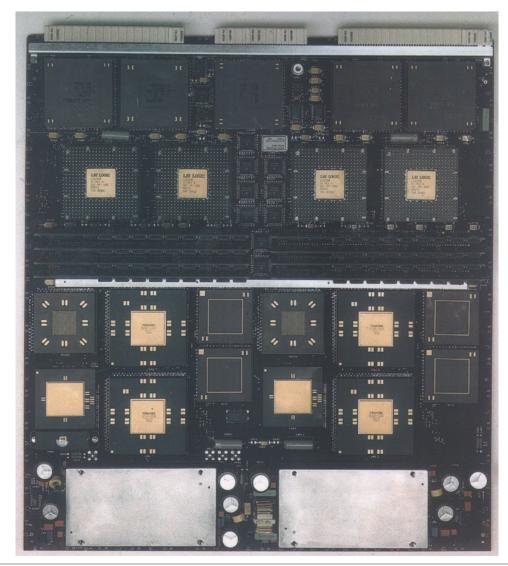

## **R8000 Based Computer Board**

#### Designed by Silicon Graphics Inc.

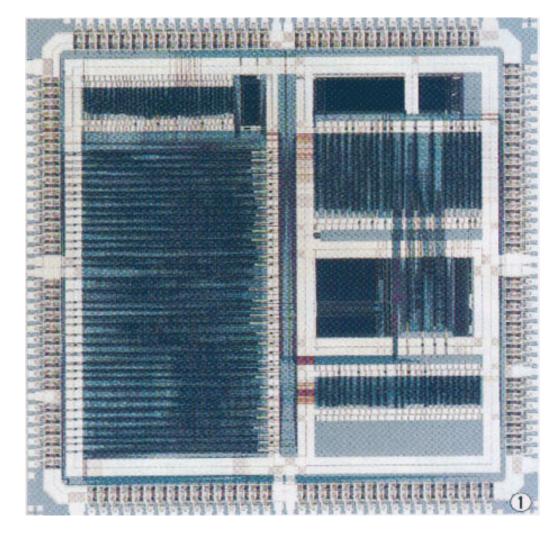

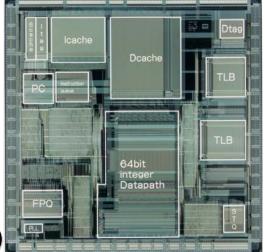

## Embedded RISC Processor TX39(1995)

#### Verilog was used

- •First Embedded RISC

- •32bit MIPS Architecture

- •40MHz/43MIPS

- •500mw

- •4KB I cache / 1KB D cache

- •4K page MMU (32 entry)

## "GSP" in 1988

- Gouraud Shading 10M Pixel/sec 30K Polygons/sec

- Flat Shading 160M Pixel/sec

- Lines

1M Lines/sec

- Clock 20MHz

- Technology

1.2 μ mCMOS

- Transistor Count 130K Transistors

- Chip size

- 11.5 × 11.3mm

- Package 144pin Flat Package

### Molecular model image by GSP

- 5160 Polygons

- 6.4 frames/Sec

- 8 bit/pixel

- 16bit Z Buffer

## **First Generation Playstation**

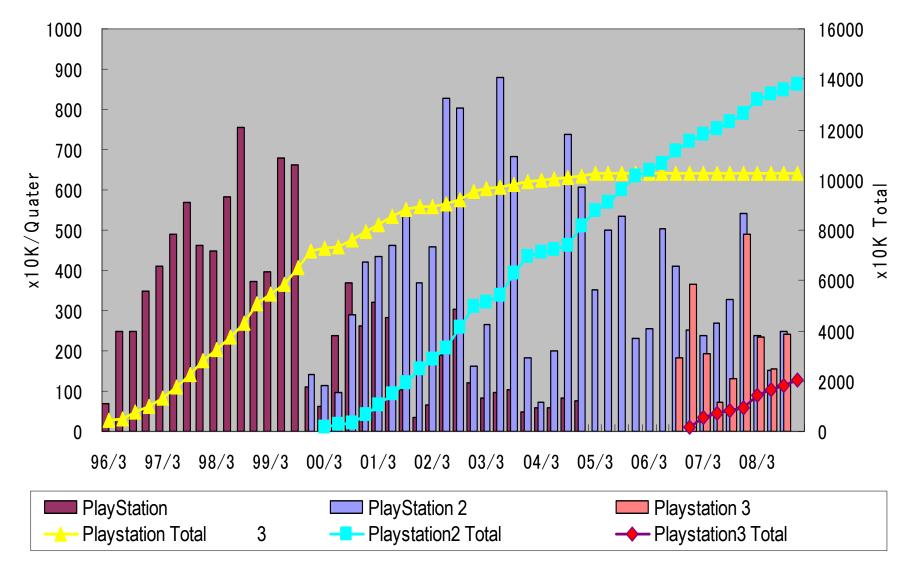

### **Playstation Shipment History**

From: http://www.scei.co.jp/corporate/data/

TOSHIBA Leading Innovation >>>

### Playstation was very successful, though

- Original business model was not making money from Hardware but Software license. In reality, could make money even from hardware, mainly because of semiconductor cost down.

- 3D graphics could get very good reputation. But It's performance was not good enough yet. Emotion of the characters couldn't be presented!

- By considering game console life cycle, hardware performance should be competitive at least for a few years

- An epoch-making graphic chip was the key for the next generation

- Embedded DRAM technology based graphics was employed

- Main processor had to have enough performance correspond to very high performance graphics. Special processor had to be developed

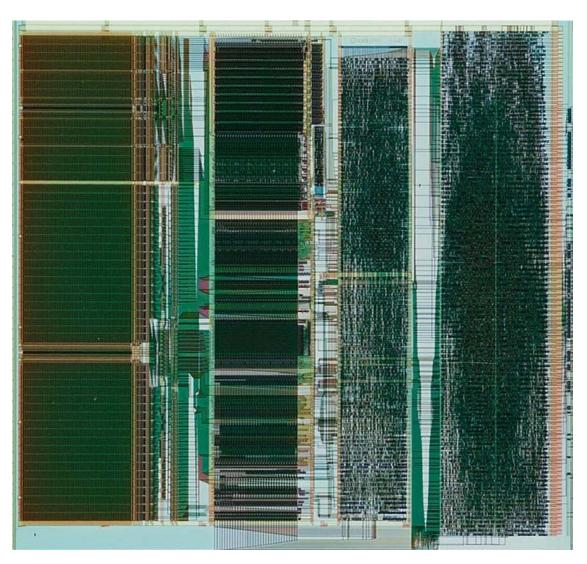

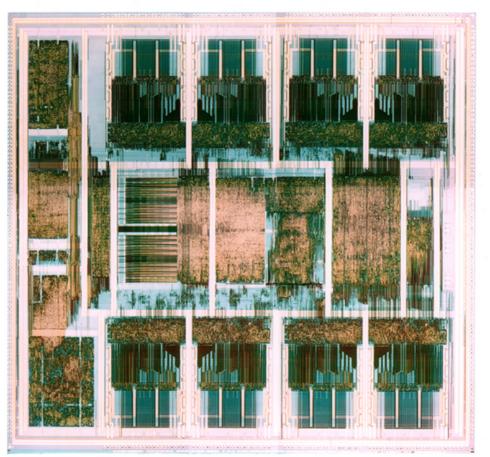

#### "Graphics Synthesizer "(GS)

- 16.6mm × 16.8mm

- 32Mbit Embedded DRAM

- 0.25 µ m

- 47.7 M transistors

- Designed by SONY, SCE and Toshiba

- Fabricated by SONY

**GRAPHICS SYNTHESIZER**

16.6mm x 16.8mm (279mm<sup>2</sup>) 42.7M transistors 0.25µm

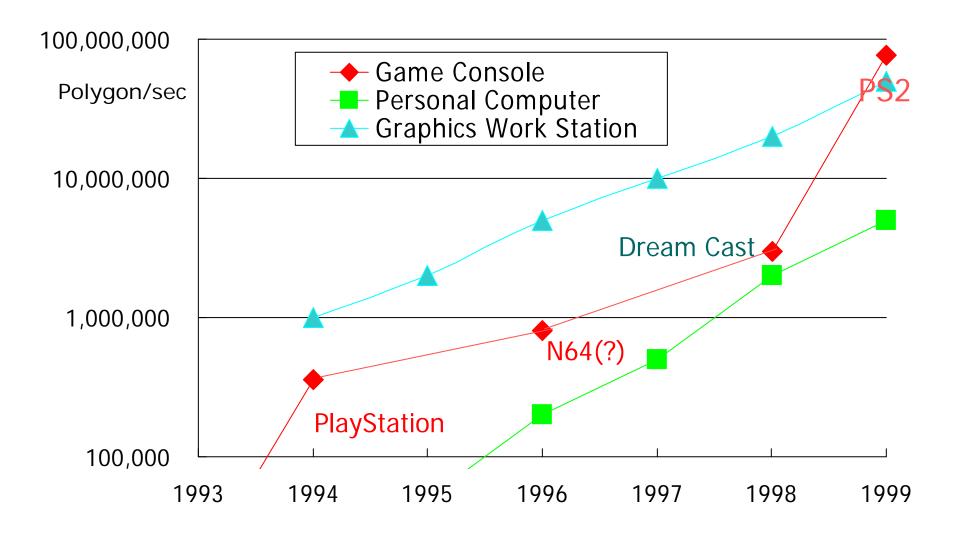

## **Rendering performance Trend**

Copyright © 2009 Toshiba Corporation, All rights reserved.

TOSHIBA

### How Emotion Engine was born?

- Toshiba could develop and provide the graphics chip for the first generation Playstaion. However, processor chip was provided by US company.

- Some engineers in Toshiba semiconductor division, began to consider to propose not only graphics but main processor for next generation Playstation, and it was called "Emotion Engine" afterwards.

- Started to approach to SCEI a few month after first generation Playstation was launched (12/3/1994).

- SCEI was interested in proposed Geometry Engine architecture, and started a joint technical investigation

- After main concept of Emotion Engine was accomplished, Toshiba team has started to develop the processor portion at the Silicon Valley office in 1996, before an agreement was done.

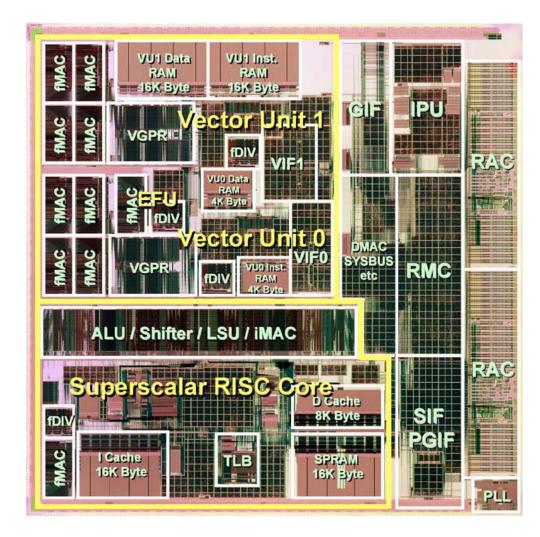

#### **Emotion Engine Die Photo**

15.02mm x 15.04mm Frequency : 300MHz Transistors : 13.5M Power : 18Watts Design Rule : 0.25um Gate Length : 0.18um Designed by SCE and Toshiba Fabricated by Toshiba

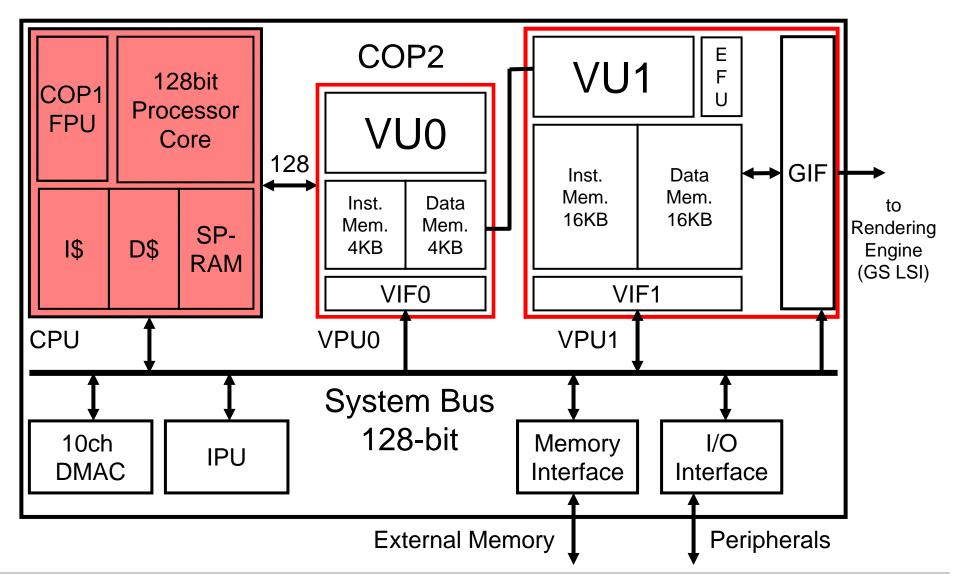

#### **Emotion Engine Block Diagram**

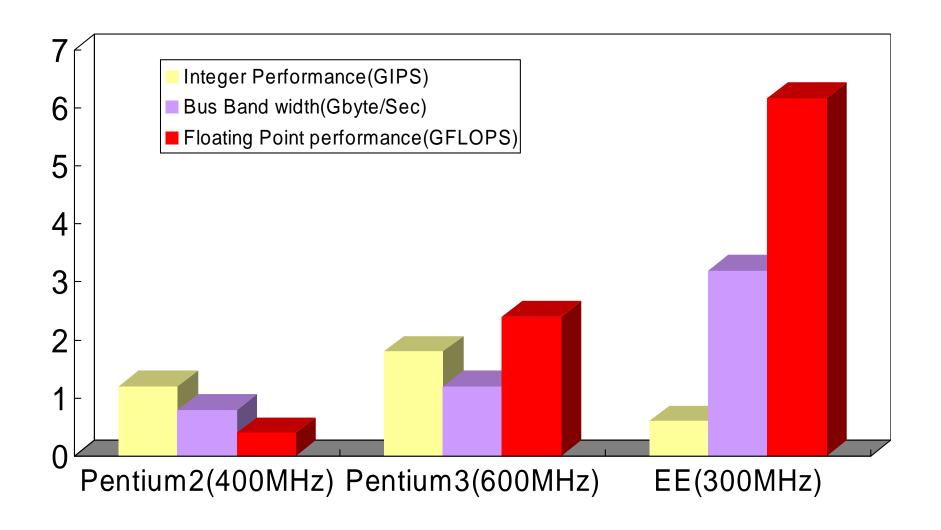

## **Emotion Engine Peak Performance**

Copyright © 2009 Toshiba Corporation, All rights reserved.

TOSHIBA

#### **Emotion Engine Development History**

- Spring 1997: Joint Development Agreement was done (Schedule was defined)

- Spring 1998 : Design Completion has been delayed because of many Bugs of CPU and not enough speed

- Had to report Six month delay from the original schedule

- Spring 1998 : Reorganize and enhance development team (82 engineers from Toshiba Japan), and Reset the Target date and specification

- #1 Design Completion 7/1998

- Chip size=17x14.1mm2

- Aug. 1998 : EE#1 Design completion (8 month Delay)

- Relaxation of the target frequency(300MHz=>200MHz)

- Agreed to Relax voltage and temperature constraint

- Oct. 1998 : Shipped the first sample and SCE started the system evaluation

- Dec. 31 1998 : Shipped the software developable revised samples

- Feb. 1999 : Presented at the conference (ISSCC), fair reputation

- Mar. 1999 : Next generation Playstation technical overview was presented at PlayStation Meeting 1999, and big impact on all over the world! EE#2 Design completed as scheduled and achieved 300MHz Target EE#3 Shrunken version(0.18um) development has been started

Leading Innovation >>>

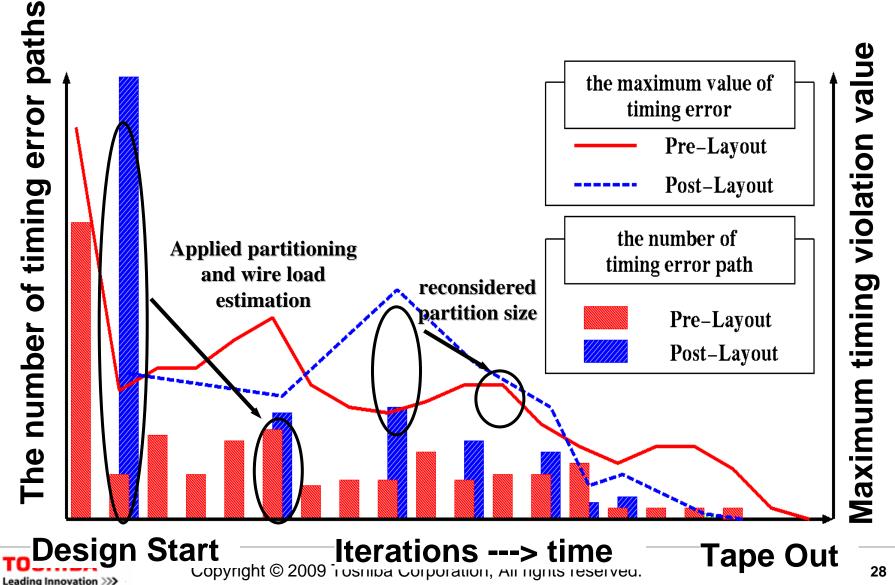

With 0.25/0.18 um design rule, controlling interconnect delay has become significant task in LSI design projects.

Designer is able to do "what-if" analysis.

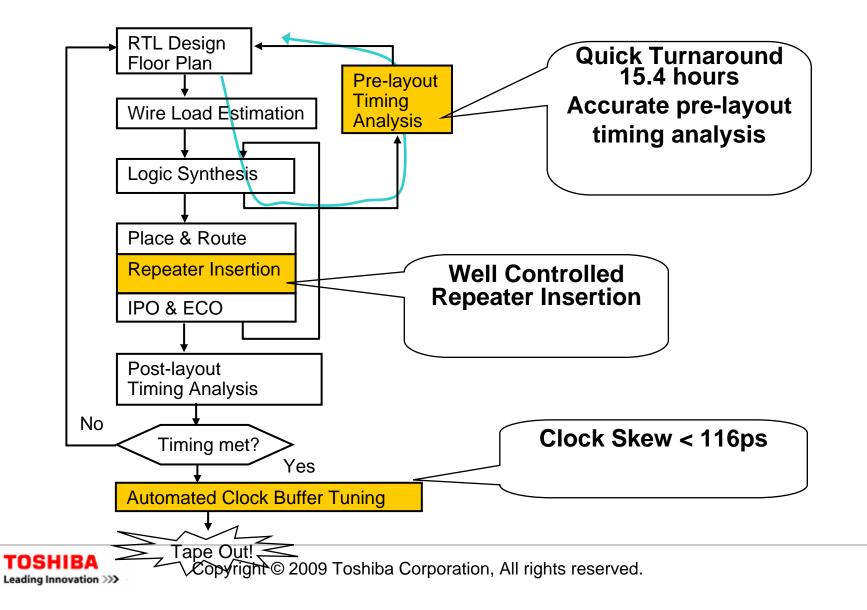

### **Timing Design Flow**

#### **Timing Closure - Results-**

### **Clock Skew Management**

- Clock skew must be minimized for

- > the maximum clock rate,

- evading a race condition.

- Automated Clock design, e.g. CTS, is established in Standard Cell rich ASIC.

- In Contrast, half of EE is occupied by custom blocks (CB's). Manual tuning is timeconsuming.

- We developed an automated clock tuning method.

## Playstation2

### **Beyond Playstation2**

- Jan. 1999 : The Investigation of the processor for the next-generation Playstation started internally in Toshiba

- > At first, investigated the possibility to develop in Silicon Valley

- Investigated IBM as a partner, they were not interested so much at first

- From the experience of Playstation2

- We didn't have to use the existing processor architecture, because Playstation can have enough volume to be a standard by itself

- From DVD capability experience, It will not be only a game console but the center for the entertainment in home

- Broadband network will be popular and have very big impact

- Basic concept of the next generation processor

- > Not just for Game console, but should be useful in various applications

- So, it must be scalable

- > The real-time computation will be the key for gaming and networking

- > New computer architecture should be employed for the new world

- Development Team

TOSHIBA

- By talking directly from Kutaragi-san to IBM, SCEI, IBM, and Toshiba have agreed to set up the joint development team

- We have agreed to develop next generation general purpose processor, and three company join the project, totally even share of the resource and the right

### **Cell BE Development Project**

- Established main campus in IBM Austin

- For the quick startup

- Reserve excellent engineers

- Multiple sites were mandatory

- Overcome management difficulty by frequent tele-conference

- Network infrastructure was very effective for the information sharing

- Joint Development team has been established

- Each part was consist of mixture of three companies engineers

- For the good communication to collaborate smoothly

- Necessary also for the technical transfer to each company

- After target was clarified, development was relatively smooth

- Quick termination of culture friction was achieved

- Flexible resource allocation was possible

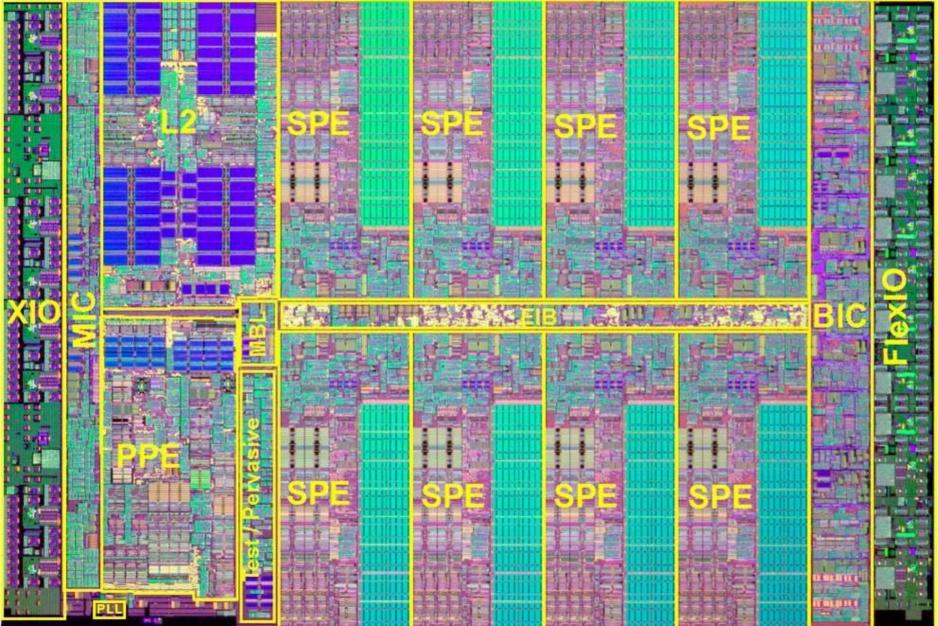

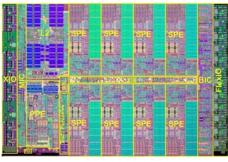

## **Cell BE Die Photo**

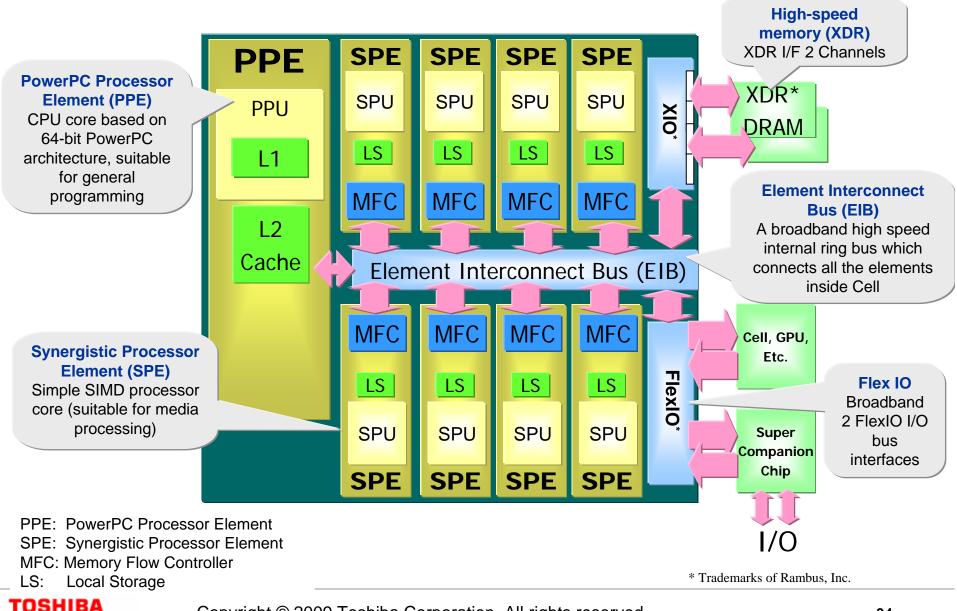

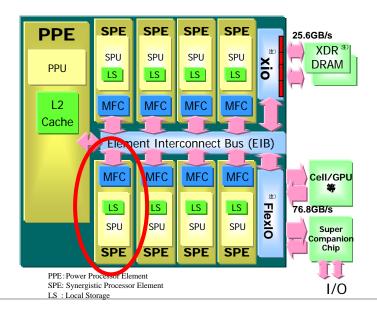

## **Cell Block Diagram**

Copyright © 2009 Toshiba Corporation, All rights reserved.

#### Cell BE Major Development Topic

- Apr. 2000 : Architecture investigation has been started among three companies

- Big culture gap, and lot of friction

- > Various candidates were investigated, and concluded almost same as present one

- Mar. 2001 : Public announcement of Joint development

- Started project by setting the campus in Austin

- Sep. 2001 : Toshiba has started to investigate the function of Peripheral chip

- Apr. 2004 : Cell BE first sample was accomplished and worked!

- Feb. 2005 : First technical presentation at ISSCC conference

- Big impact all over the world

Leading Innovation >>>

- Aug. 2005 : Toshiba presented peripheral chip and SPE asign software idea

- Oct. 2005 : Toshiba demonstrated at CEATEC exhibition

- One of the biggest impact demonstration

- All major TV station mentioned in the news program

- Apr. 2006 : Toshiba started to provide Cell BE development set

- Sep. 2006 : IBM won a Cell BE based super computer for the national research Lab.

- Nov. 2006 : SCEI launched Playstation3 with Cell BE

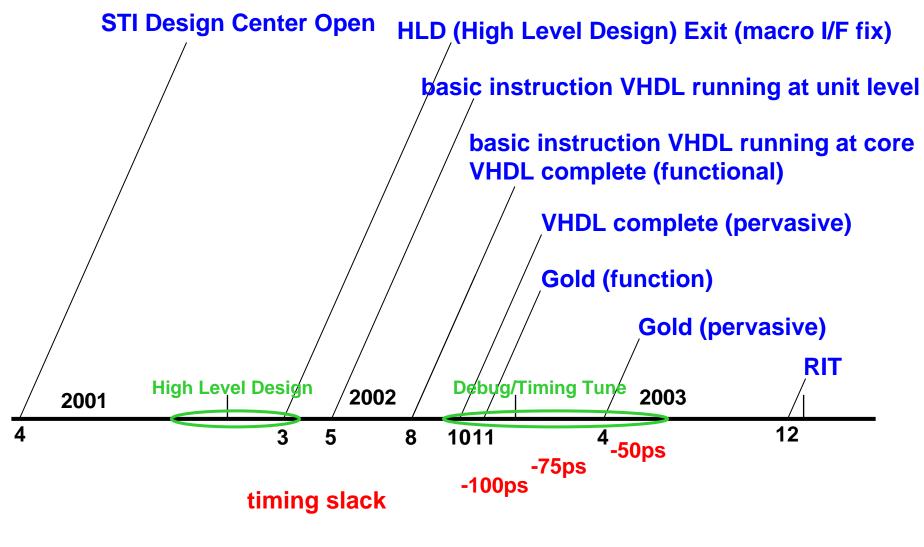

### Cell BE (SPU) Design History

#### -200ps

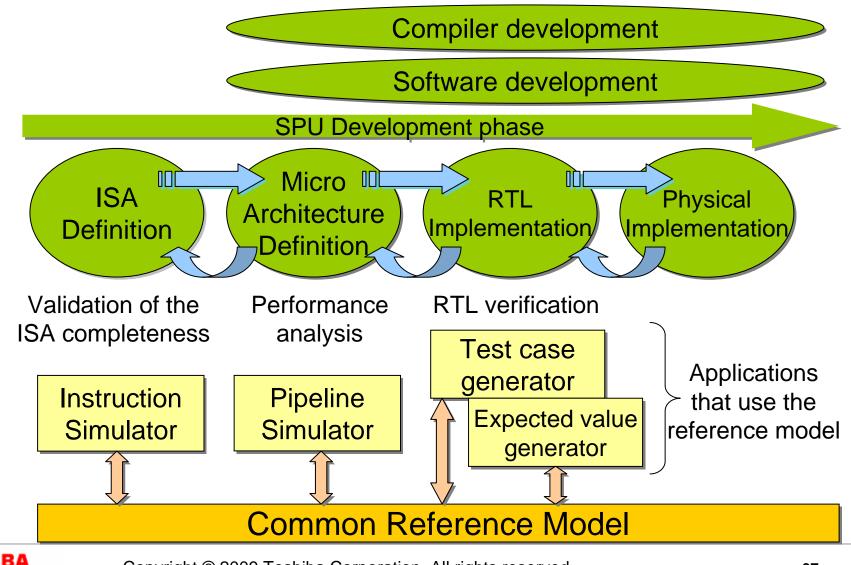

### Each Reference model for SPU Development phase

TOSHIBA Leading Innovation >>>

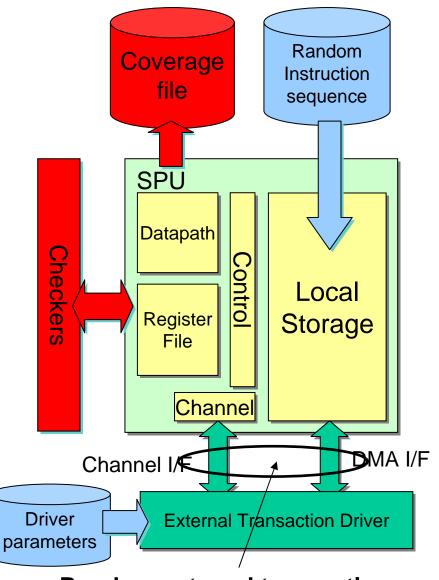

## **SPU Verification Strategy**

#### Coverage Based Verification

- Test items are written as coverage events

- Executes simulation random test cases until all the coverage events are hit.

- Random instruction sequences

- Random external transactions

- The checkers check SPU logic correctness while simulation

- Coverage files are generated as a simulation results

#### Random external transactions

## Synergistic Processor Element Feature

#### New architecture for the data processing

- Media and floating point computation

- RISC type instruction set

- High level language oriented

- SIMD based instruction scheme

- 128 bit width Parallel execution (e.g. 4x32bit)

- Large 128bit width 128 entry register file

- 256KB Local store, not Cache

- Rich performance monitoring capability

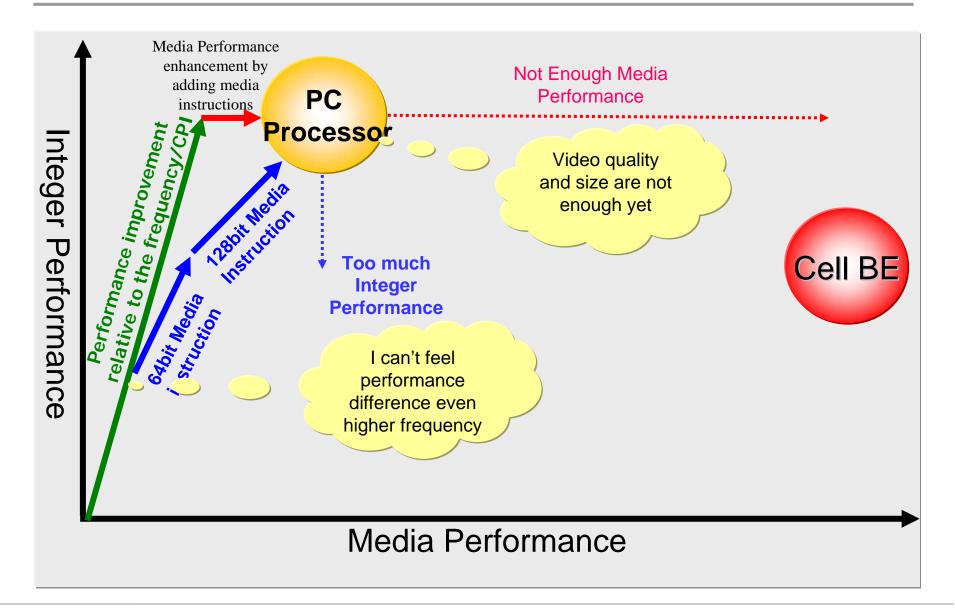

### **Cell BE positioning as a Processor**

### **Cell BE Proposes New Computer Direction**

#### New computer direction proposed by Cell BE

#### To show hardware feature as is to the user

- Program must be written by considering HW structure and memory size

- Need knowledge about HW

#### > Instead, let user know what is going on in the computer

- Easier performance tuning

- Especially for realtime system

#### > Overwhelming cost performance is achieved

Very Small SPE sometimes provide twice of performance of PC processor

#### Maybe new direction since RISC is proposed

More than 20 years ago

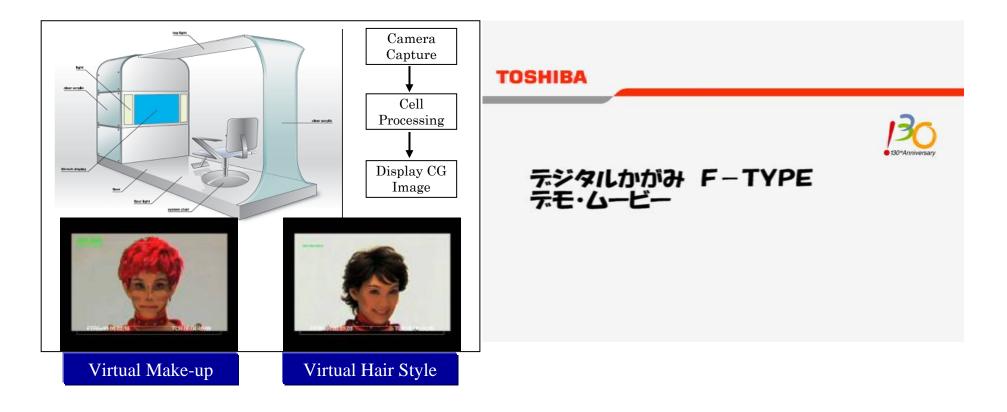

### **Real-time Face Tracking**

Camera captures the face of the person facing the "mirror", and in real-time, the rendered image is projected in the "mirror".

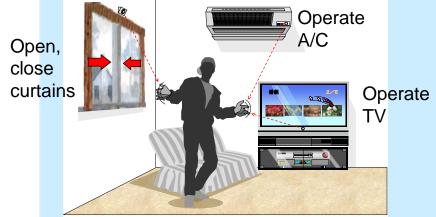

## Hand Gesture User Interface

- Operate products using hand gestures (hand position, motion)

- > Deviceless remote control.

- Applicable for a variety of daily life objects.

<sup>•</sup> Three hand share can be recognized

. GUI Control by recognized image

TOSHIBA Leading Innovation >>>

Copyright © 2009 Toshiba Corporation, All rights reserved.

Hand gesture controlled media player equipment prototype

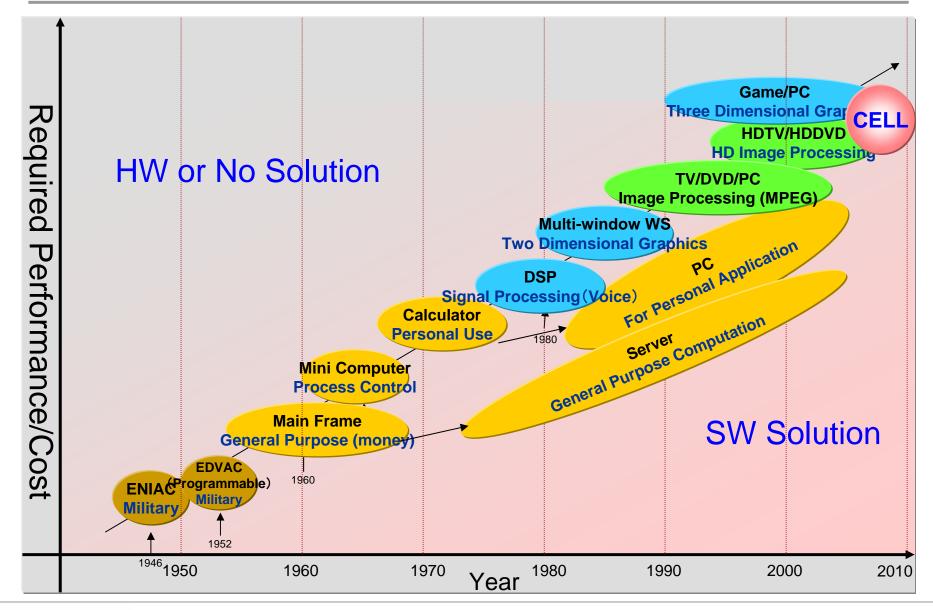

### Trend of HW→SW

TOSHIBA Leading Innovation >>>

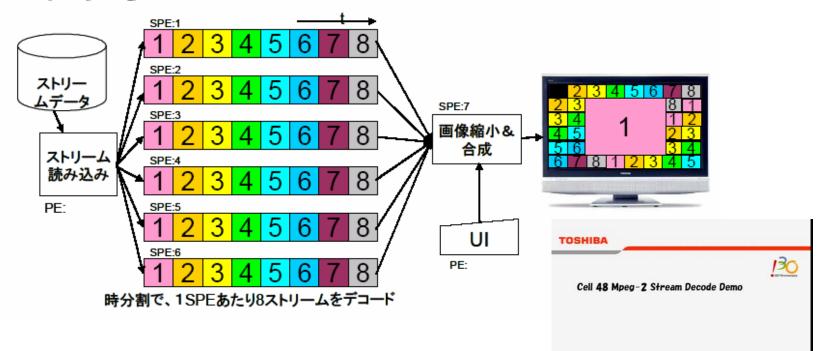

### 48 Streams (MPEG2) Decode Demo

- MPEG2 (About 4Mbps) · · · 720 x 480

- Read out 48 streams from HDD and Decode

- Shrink to 1/3 and arranged to one picture for displaying on the TV

### Hard to Find Customers in this Field

So, by Focusing on Video Application for PC!

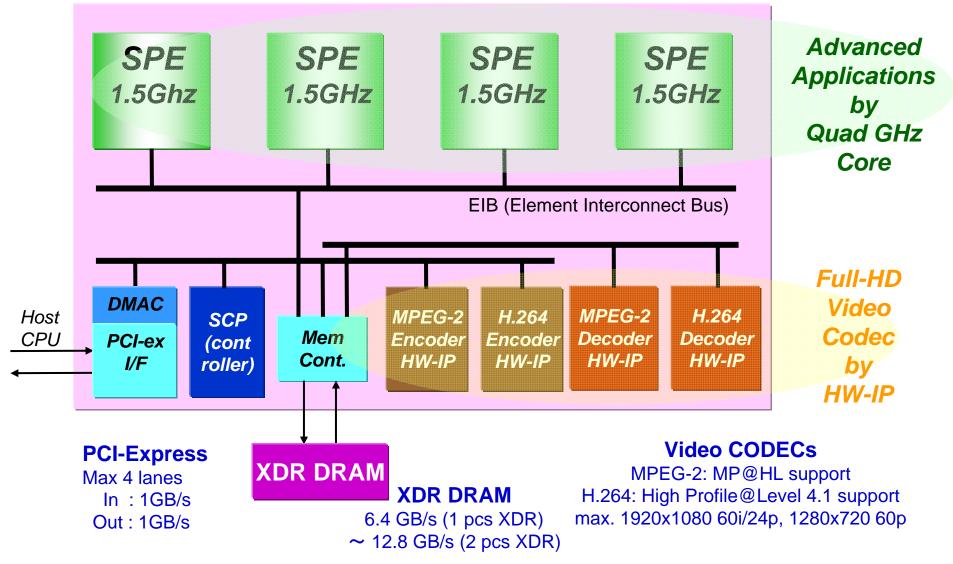

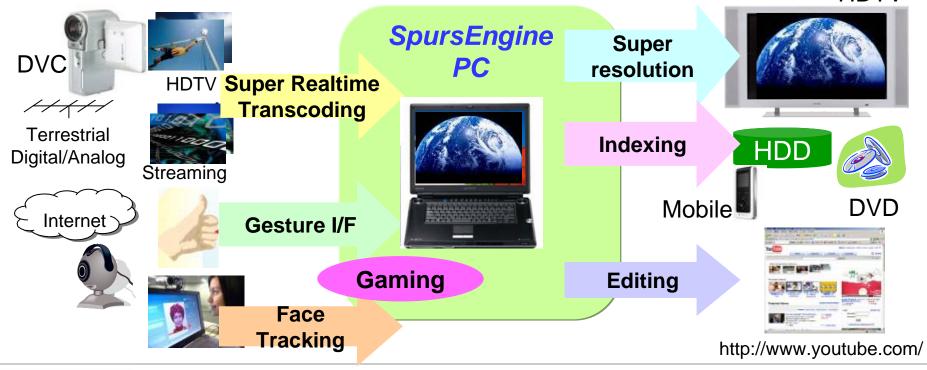

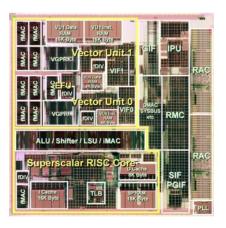

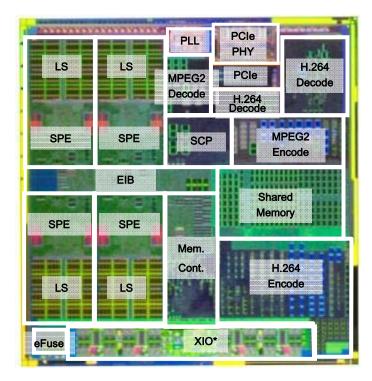

### SpursEngine<sup>™</sup> Block Diagram

XDR<sup>™</sup> DRAM is trademark of Rambus Inc. in the United States and other countries.

TOSHIBA Leading Innovation >>>

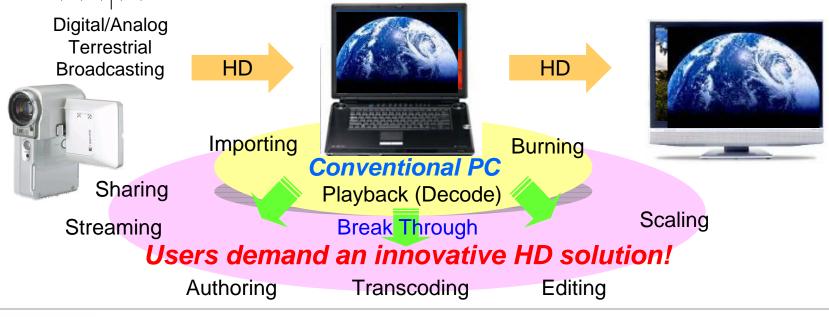

### What is the Next Target for PC? Answer is HD.

#### Emergence of HD Contents

- High Definition (HD) era has been quickly emerging. For instance, video content from digital terrestrial broadcasting, digital video cameras, and optical disks are all HD ready.

- HD contents require much more processing power than SD contents.

- HD needs 6 times higher bandwidth than Standard Definition (SD). Conventional PC architecture of CPU and GPU can only decode HD video in real-time.

- CPU, even though it keeps getting faster, will not be capable of real-time encoding HD, video, in the near future.

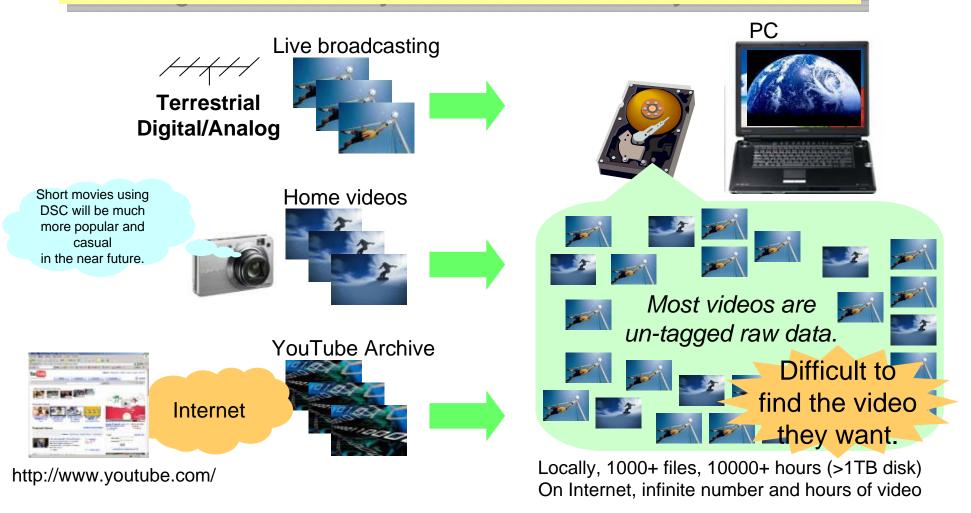

### **Demand: Video Indexing and Searching**

# Future demands: not only transcoding, but also *indexing and* searching features to easily find the video which they want to watch.

### Further Advantages: New applications by SpursEngine

- **Super realtime Transcoding:** Transcoding at faster than real-time

- Super Resolution: Picture resolution up-scaling for HDTV

- Indexing: Video categorizing during HDD storing, DVD burning

- Gesture I/F: Control various devices in the living room by hand gestures

- **Face Tracking:** Realtime 3D face tracking for communication tools

- Interactive Gaming: New type of realtime game with Gesture I/F and Face Tracking

- Editing: Video editing of consumer generated content

HDTV

### Toshiba PC: Qosmio with SpursEngine

#### Toshiba released Qosmio empowered by SpursEngine in July 2008.

TOSHIBA

### Waves to Standardization and Customization

Source : Makimoto' s Wave

TOSHIBA

### Starting ASIC, RISC Processor Era (From '87)

- Starting HDL Design by Semiconductor Company's Proprietary CAD

- AI Workstation (1985 to 1987)

- Last trial for designing processor using standard parts

- 3D Graphics Processor (from 1986)

- First chip using proprietary HDL CAD H<sup>2</sup>DL, and standard Cell

- Revolutionary design efficiency, small design team was arrowed

- Al Processor Chip(1987 to 1988)

- Designed by using Silicon Compiler "Genesil"

- Defeated by severe RISC competition with declining AI booming

- TRON Processor (1986 to 1989)

- Disappeared in the CISC/RISC debates

- GL Processor (1989 to 1991)

- Again relatively large team, and couldn't reach final stage

- Prologue to R8000

TOSHIBA Leading Innovation >>>

### Processor Development Became a Big Project Again

- Proprietary EDA was expelled by third party EDA vendors

- R8000 for Server(1991-1993)

- Successor of GL Processor Team

- Joint Development with Silicon Graphics Inc

- Verilog HDL and logic Synthesis tool was used

- Random verification and C reference model

- Start of Standard EDA Era

- R10000 for Server and Workstation (1994-1997)

- Very Early out of order processor

- One year project delay

- Big competition era

TOSHIBA

- TX39, 49 for Embedded Application(1993-1998)

- Embedded RISC Processor raised

- Good power performance

- Started to have revenue, though,,

## Standard Processor Era Since 1997

- For the leading edge development, proprietary EDA was necessary combining with standard flow

- X86 Architecture became standard (RISC was defeated)

- Less advantage by super scalar architecture

- Out of order made no advantage for RISC

- Emotion Engine(1996-1999)

- Multi-core Architecture was adopted

- STA, Formal Verification, Extraction

- Cell Broadband Engine(2000-2005)

- AI most IBM Proprietary EDA was used

- DFT, Assertion, DFM, Power Estimation

- Was good enough for the fastest processor

- Too early for replacing HW solution

#### **Processor Clock Rate per Year**

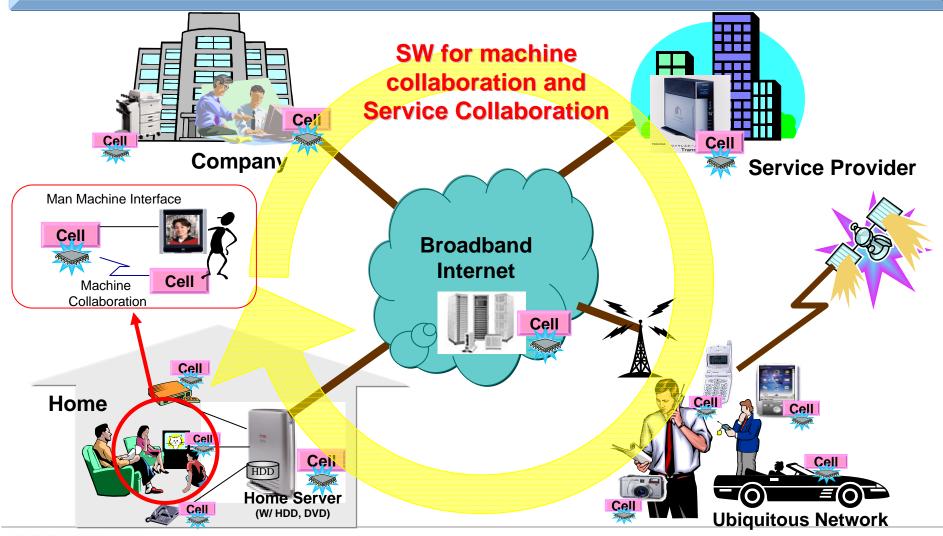

### What is going on to the MPU and SOC Now?

- Just Transition from Standard MPU Era to Custom SOC Era

- Change of technology direction : Big chance in ten years

- Out of order changed the direction ten years ago

- RISC→CISC

- From frequency competition to multi-core

- Player increase by matured technology

- What is SOC as a technology driver?

- Combination of processor and fixed function unit

- SpursEngine will be one of the early example

- Big change is necessary for EDA too

- Backend design will change too : no custom block

- Model based design with coverage based random verification

- High level design including software is the next key

- Manufacturing Technology is Also Changing

- DFM is needed

- A lot of new materials, for low power

- New transistor structure

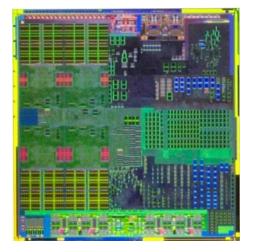

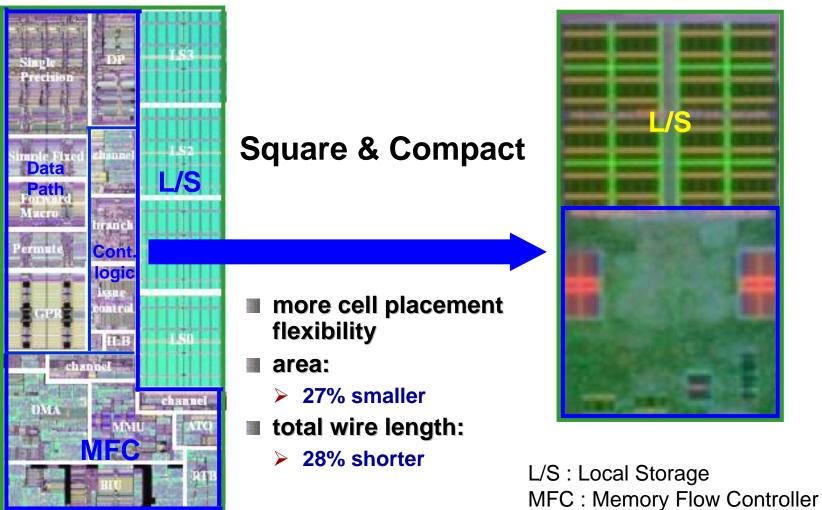

## SpursEngine<sup>™</sup> Physical Implementation

- Process:

- 65nm bulk CMOS with 7 levels of copper layers

- Die Size:

- 9.98mm x 10.31mm, 102.89mm<sup>2</sup>

- Fmax: 1.5GHz

- Transistor Counts:

- ▶ 239.1M

- Logic: 134.3M

- SRAM: 104.8M

- TDP

- < 20W (depending on application sets)</p>

- Package:

- FC BGA 624

\* XIO<sup>™</sup> is trademarks of Rambus Inc. in the United States and other countries.

### Key Design Feature: Synthesizable Over GHz SPE

### Synthesizable design

- shorter design TAT

- (estimation: 1/4 compared with custom migration)

- Technology Independent

- To Develop Different Target SoC

### Key Feature

TOSHIRA

- Floor plan optimization

- hybrid standard cell height

- RTL abstraction

- register retiming

- semi-custom clock tree

- wire width control

# **Floor Plan Optimization**

#### Original Floor Plan (Cell/B.E.<sup>™</sup>)

#### Cell/B.E.<sup>™</sup> (65nm) 2.09mm x 5.30mm

#### **New Floor Plan**

SpursEngine<sup>™</sup> (65nm) 2.07mm x 3.93mm

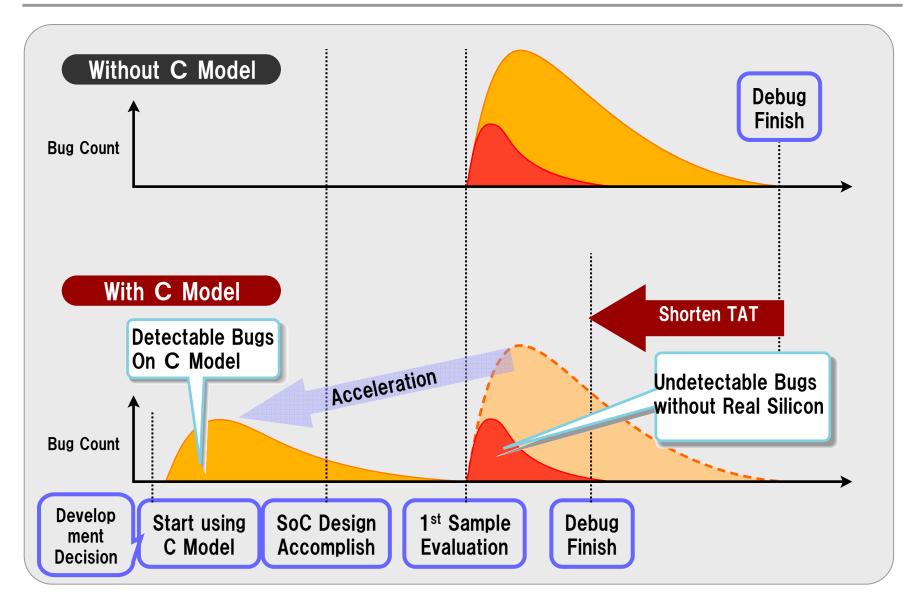

### Introduction of C Model for DTV-SoC

### **Effect of C Model : Shorten TAT**

Copyright © 2009 Toshiba Corporation, All rights reserved.

TOSHIBA

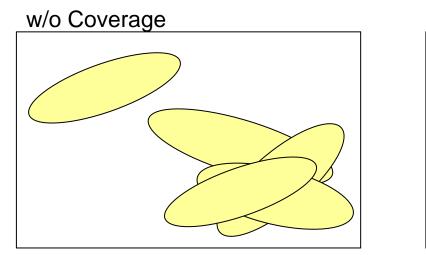

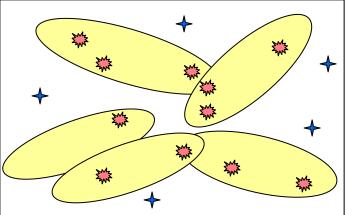

## **Coverage Base Random Verification**

- The limitation of Directed Test

- Many good engineers are necessary to write enough test cases

- Test cases must be rewritten by design changes

- Cannot write unknown test cases

- Random Test is Mandatory though,

- No hand written assembler level test cases

- No way to cover all the test case

- To randomize many parameters is most important thing

- ➤ Simulation cycle count doesn't mean verification quality →Coverage Base verification

### Random Simulator for SoC

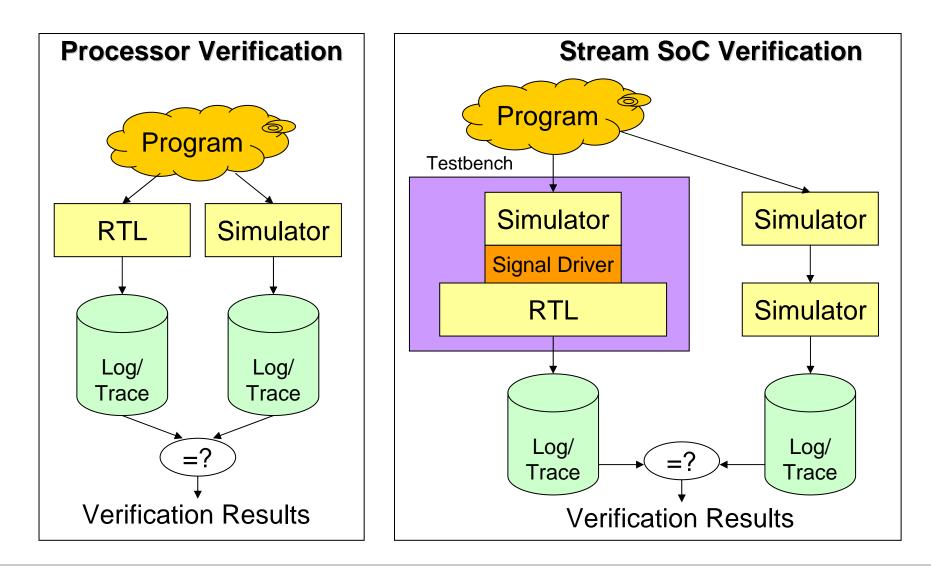

### **EDA for Technology Driver SoC**

#### **Fusion of Two Environments is the Key Point!**

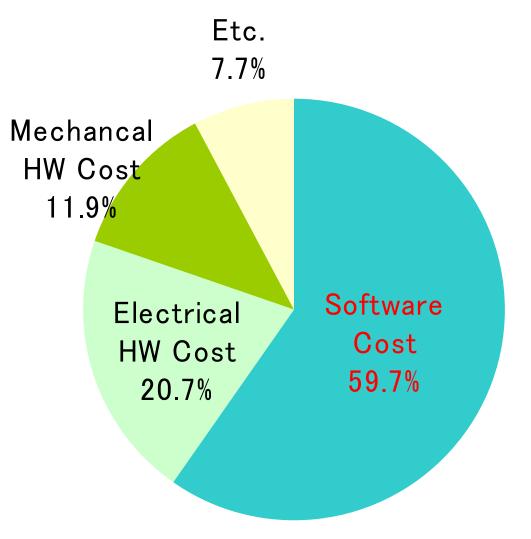

### Software Development Cost is Dominant Even Today

Source : Embedded Software Investigation by METI (2007)

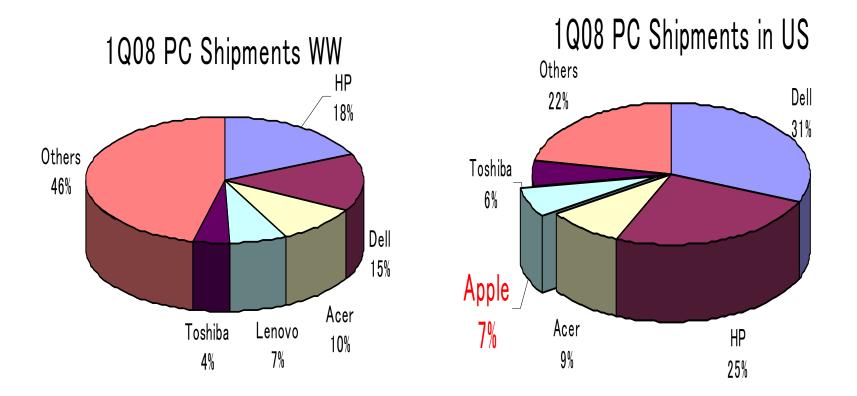

### HW Variation is Very Effective for Software Environment

Apple is supporting proprietary OS with only 7% US market share

Source: Gartner (April 2008)

TOSH

## Towards Software Centric Era (After 2017?)

- Software Development Cost will be much more than Today

- It will be impossible to support many platforms

- HW Design Cost will also Increase a Lot

- Design methodology won't meet design complexity increase

- Verification will be the critical issue

- Single purpose LSI will not pay off any more

- More expensive prototyping

- Complicated mask process

- Enough Performance with Software Solution

- Less cost and power for the same function

- It will be possible to replace dedicated HW such as software radio

- Protocols will be more complex and varies

- MPEG2 lasted for 10 years, but next is confusing such as H264, DIVX, VC1

- MPEG4 varies more than 20 derivatives

- Voice Codec are innumerable (AAC3,MP3,WMA,,,,)

- Softness will have bigger advantage

TOSHIBA

Leading Innovation >>>

New Revolution will be Necessary for After Software Centric Era

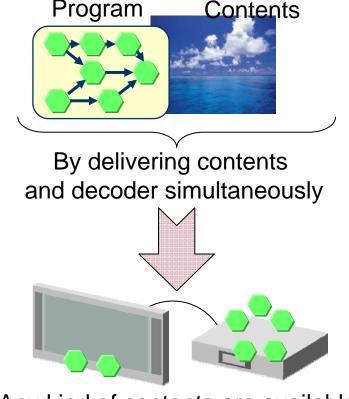

### Software solution of HW makes possible to....

- Freedom from standardization

- Quick service startup with new technology becomes possible

- Proprietary Contents delivery

- Better compression technology than standard

- Hi-level Contents protection

- Apply various charging system

- Efficient usage of Network Infrastructure

- Communication with proprietary protocol

- Proprietary cipher system

TOSHIBA

Leading Innovation >>>

Any kind of contents are available

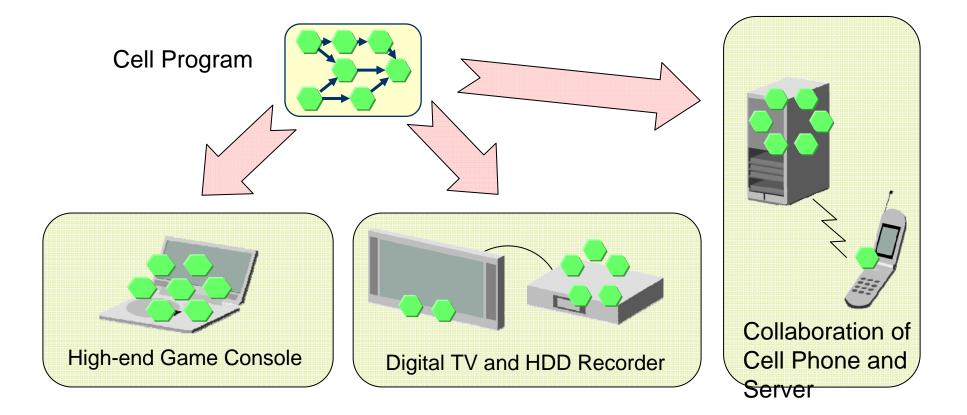

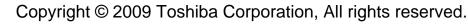

## Network Transparent Model Makes...

- Heavy function is achievable by collaborating multiple machines on the network

- Same Program is applicable to various performance machines with keeping real-time-ness from Cell phone to Server

TOSHIBA

## **Scalability of Cell BE**

TOSHIBA

# Towards Cell World

By taking advantage of overwhelming performance, Cell BE is aiming at the new software standard world

# Summary

Semiconductor Roadmap is Straight Forward, But application is not

- Moore's Law is forever!?

- Technology Driver is changing

- Makimoto's Wave is still surviving

- Our Microprocessor Development History was Also Following the Wave

- Design Methodology is Dramatically Effective for this Wave

- Requirement for EDA for Technology Driver was Changing

- Description, Timing, Backend, Verification

- Positioning of Emotion Engine and Cell was Standard Processors

- Today is Transition from Standard Processor to SoC

- No More Frequency Increase

- Need Purpose Oriented SoC's

- SpursEngine is One of the Typical Example

- Verification Methodology for Processor began to be applied for designing SoC's

- Needs High Level and Software Oriented Design Environment

- Next Wave will be Software Centric

TOSHIBA

- Will take some more time for new revolution after software era

- Take Advantage of Today's Transition

## Cell Everywhere!! Thank you

# **TOSHIBA** Leading Innovation >>>