## 1D-12 Design and Evaluation of Variable Stages Pipeline (VSP) Processor Chip

<u>Tomoyuki Nakabayashi</u>, Takahiro Sasaki, Kazuhiko Ohno and Toshio Kondo Graduate School of Mie University

### Battery life is a problem for mobile computers

Mobile computers are required to achieve both

Low energy and High performance.

#### We propose low energy processor architecture

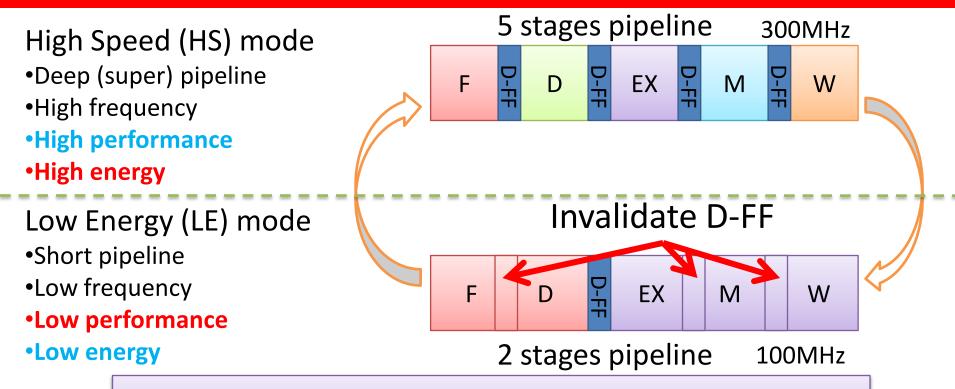

## VSP (Variable Stages Pipeline)

#### Vary the pipeline depth dynamically.

Glitch propagation becomes serious problem.

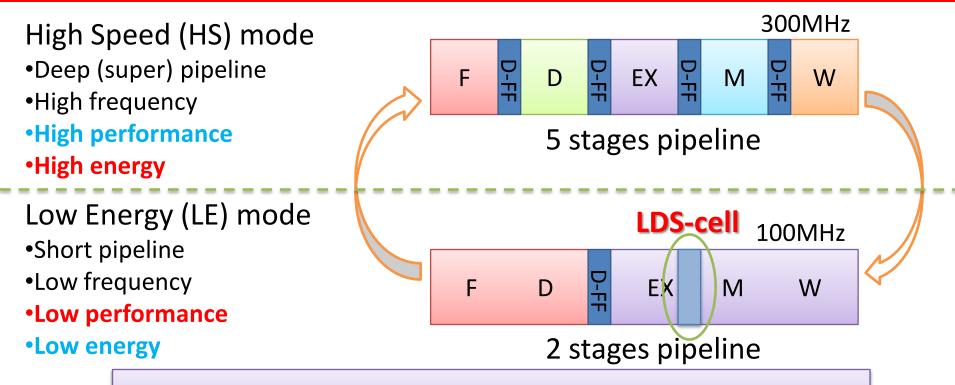

## VSP (Variable Stages Pipeline)

#### Vary the pipeline depth dynamically.

LDS-cell prevent glitch propagation.

## LSI Design

| Technology            | ROHM0.18µm CMOS process       |

|-----------------------|-------------------------------|

| Standard cell library | VDEC Kyoto University Library |

| Chip size             | $2.5 \times 5.0 \text{ mm}^2$ |

| Measure energy        | HP83000 LSI tester            |

|                              | HS mode    | LE mode  |

|------------------------------|------------|----------|

| Instruction set architecture | MIPS R3000 |          |

| Pipeline depth               | 9 stages   | 3 stages |

| Target frequency             | 100 MHz    | 25 MHz   |

|                      | VSP     |

|----------------------|---------|

| Number of transistor | 521,971 |

# VSP can reduce 13% energy than conventional approach.