# ASP-DAC 2011 Advance Program

16th Asia and South Pacific Design Automation Conference Date: January, 25-28, 2011

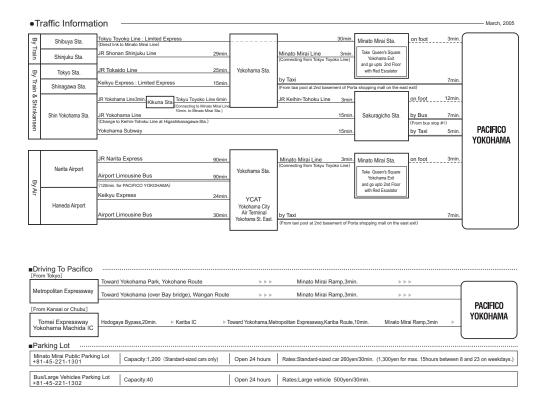

Place: Pacifico Yokohama, Yokohama, Japan

http://www.aspdac.com/

## **Highlights**

#### Opening and Keynote I

Wednesday, January 26, 8:30-10:00

Takayuki Kawahara (Hitachi, Japan) "Non-Volatile Memory and Normally-Off Computing"

#### Keynote II

Thursday, January 27, 9:00-10:00

**Ajoy Bose** (Atrenta Inc., U.S.A.) "Managing Increasing Complexity through Higher-Level of Abstraction: What the Past Has Taught Us about the Future"

### Keynote III

Friday, January 28, 9:00-10:00

Subhasish Mitra (Stanford Univ., U.S.A.) "Robust Systems: From Clouds to Nanotubes"

#### **Special Sessions**

## 1D: University LSI Design Contest (Presentation + Poster Discussion)

Wednesday, January 26, 10:20-12:20

## 2D: Emerging Memory Technologies and Its Implication on Circuit Design and Architectures

Wednesday, January 26, 13:40-15:40

**2D-1:** Meng-Fan Chang (National Tsing Hua Univ., Taiwan), Pi-Feng Chiu, Shyh-Shyuan Sheu (ITRI, Taiwan) "Circuit Design Challenges in Embedded Memory and Resistive RAM (RRAM) for Mobile SoC and 3D-IC"

## 3C: Post-Silicon Techniques to Counter Process and Electrical Parameter Variability

Wednesday, January 26, 16:00-18:00

**3C-1:** Ming Gao, Peter Lisherness, Kwang-Ting (Tim) Cheng (Univ. of California, Santa Barbara, U.S.A.) "Post-silicon Bug Detection for Variation Induced Electrical Bugs"

#### 3D: Recent Advances in Verification and Debug

Wednesday, January 26, 16:00-18:00

**3D-1:** Miroslav N. Velev, Ping Gao (Aries Design Automation, U.S.A.) "Automatic Formal Verification of Reconfigurable DSPs"

## 4D: Advanced Patterning and DFM for Nanolithography beyond 22nm

Thursday, January 27, 10:20-12:20

**4D-1:** Soichi Inoue, Sachiko Kobayashi (Toshiba, Japan) "Allout Fight against Yield Losses by Design-manufacturing Collaboration in Nano-lithography Era"

#### 7D: Virtualization, Programming, and Energy-Efficiency Design Issues of Embedded Systems

Friday, January 28, 10:20-12:20

**7D-1:** Tatsuo Nakajima, Yuki Kinebuchi, Hiromasa Shimada, Alexandre Courbot, Tsung-Han Lin (Waseda Univ., Japan) "Temporal and Spatial Isolation in a Virtualization Layer for Multi-core Processor based Information Appliances"

### Designers' Forum

#### 5D: (Panel Discussion) C-P-B Co-design/Co-verification Technology for DDR3 1.6G in Consumer Products

Thursday, January 27, 13:40-15:40

Organizer: Koji Kato (Sony, Japan)

Moderator: Makoto Nagata (Kobe Univ., Japan)

Panelists:

Keisuke Matsunami (Sony, Japan) Yoshinori Fukuba (Toshiba, Japan) Ji Zheng (Apache Design Solutions, U.S.A.) Jen-Tai Hsu (Global Unichip Corp., U.S.A.) CP Hung (ASE, Taiwan)

## **6D:** (Invited Talks) Emerging Technologies for Wellness Applications

Thursday, January 27, 16:00-18:00

- **6D-1:** Masaharu Imai, Yoshinori Takeuchi, Keishi Sakanushi, Hirofumi Iwato (Osaka Univ., Japan) "Biological Information Sensing Technologies for Medical, Health Care, and Wellness Applications"

- **6D-2:** Srinivasa R. Sridhara (Texas Instruments, Inc., U.S.A.) "Ultra-Low Power Microcontrollers for Portable, Wearable, and Implantable Medical Electronics"

- **6D-3:** Valer Pop, Ruben de Francisco, Hans Pflug, Juan Santana, Huib Visser, Ruud Vullers, Harmke de Groot, Bert Gyselinckx (IMEC, Netherlands) "Human++: Wireless Autonomous Sensor Technology for Body Area Networks"

- **6D-4:** Koji Ara, Tomoaki Akitomi, Nobuo Sato, Satomi Tsuji, Miki Hayakawa, Yoshihiro Wakisaka, Norio Ohkubo, Rieko Otsuka, Fumiko Beniyama, Norihiko Moriwaki, Kazuo Yano (Hitachi, Ltd., Japan) "Healthcare of an Organization: Using Wearable Sensors and Feedback System for Energizing Workers"

## 8D: (Invited Talks) State-of-The-Art SoCs and Design Methodologies

Friday, January 28, 13:40-15:40

- **8D-1:** Takao Suzuki (Panasonic Corp., Japan) "Advanced System LSIs for Home 3D System"

- **8D-2:** Yoshiyuki Kitasho, Yu Kikuchi, Takayoshi Shimazawa, Yasuo Ohara, Masafumi Takahashi, Yoshio Masubuchi, Yukihito Oowaki (Toshiba Corp. Semiconductor Company, Japan) "Development of Low Power and High Performance Application Processor (T6G) for Multimedia Mobile Applications"

- 8D-3: Atsuki Inoue (Platform Technologies Laboratories, Japan) "Design Constraint of Fine Grain Supply Voltage Control LSI"

- 8D-4: Masaru Takahashi (Renesas Electronics Corp., Japan) "FPGA Prototyping using Behavioral Synthesis for Improving Video Processing Algorithm and FHD TV SoC Design"

- **8D-5:** Nobuyuki Nishiguchi (STARC, Japan) "An RTL-to-GDS2 Design Methodology for Advanced System LSI"

## **9D:** (Panel Discussion) Advanced Packaging and 3D Technologies

Friday, January 28, 16:00-18:00

Organizer: Yoshio Masubuchi (Toshiba, Japan) Moderator: Yaoko Nakagawa (Hitachi, Japan)

Panelists:

Geert Van der Plas (IMEC, Belgium)

Hirokazu Ezawa (Toshiba, Japan)

Yasumitsu Orii (IBM, Japan)

Yoichi Hiruta (J-Devices, Japan)

Chris Cheung (Cadence Design Systems, U.S.A.)

## Two Full-Day and Four Half-Day Tutorials

**FULL-DAY Tutorials:**

#### **Tutorial 5: Post Silicon Debug**

Tuesday, January 25, 9:30-12:30, 14:00-17:00

Organizer:

Subhasish Mitra (Stanford University, USA)

Speakers:

Rand Gray (Intel, USA) Nagib Hakim (Intel, USA) Sascha Junghans (IBM, Germany)

#### Tutorial 6: MPSoC: Multiprocessor System on Chip

Tuesday, January 25, 9:30-12:30, 14:00-17:00

Organizer:

Ahmed Amine Jerraya (CEA-LETI, France)

Speakers:

Takashi Miyamori (Toshiba, Japan) Rephael David (LIST, France) Sani Nassif (IBM, USA) Sungjoo Yoo (Postech, Korea)

#### **HALF-DAY Tutorials:**

#### **Tutorial 1: Advanced CMOS Device Technologies (1)**

Tuesday, January 25, 9:30-12:30

#### **Tutorial 2: Advanced CMOS Device Technologies (2)**

Tuesday, January 25, 14:00-17:00

Organizer:

Ken Uchida (Tokyo Institute of Technology, Japan)

Speakers:

Paul C. McIntyre (Stanford University, USA) Shinichi Takagi (The University of Tokyo, Japan) Toshiro Hiramoto (The University of Tokyo, Japan) Arvind Kumar (IBM, USA)

#### **Tutorial 3: 3D Integration (1)**

Tuesday, January 25, 9:30-12:30

#### **Tutorial 4: 3D Integration (2)**

Tuesday, January 25, 14:00-17:00

Organizer:

Hideki Asai (Shizuoka University, Japan) Speakers:

Joungho Kim (KAIST, Korea)

Hideki Asai (Shizuoka University, Japan) G. Van der Plas (IMEC, Belgium)

Erping Li (A-STAR IHPC, Singapore)

## Tuesday, January 25, 2011

|       | Registration (8:00 - )                                            |                                                                          |                                                    |                                                                           |  |

|-------|-------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------|--|

| 9:30  | Tutorial 1: Advanced CMOS Device Technolo-                        | Tutorial 3: 3D Integration (1) [Half day]                                | Tutorial 5: Post Silicon Debug [Full day]          | Tutorial 6: MPSoC: Multiprocessor System on                               |  |

|       | gies (1) [Half day]                                               | Organizer: Hideki Asai (Shizuoka Univ., Japan)                           | Organizer: Subhasish Mitra (Stanford Univ., USA)   | Chip [Full day]                                                           |  |

|       | Organizer: Ken Uchida (Tokyo Inst. of Tech., Japan)               |                                                                          |                                                    | Organizer: Ahmed Jerraya (CEA-LETI, France)                               |  |

|       | 1. "Gate Stack of Advanced CMOS Devices: High-                    | 1. "Signal Integrity of TSV Based 3D IC" Joungho                         | 1. "Introduction"                                  | 1. "Energy Efficient Multicore (MPSoC) Architec-                          |  |

|       | k/Metal-Gate Technologies" Paul C. McIntyre (Stanford Univ., USA) | Kim (KAIST, Korea)                                                       | 2. "Logical Errors" Sascha Junghans (IBM, Germany) | tures" Takashi Miyamori (Toshiba, Japan)                                  |  |

|       | 2. "Channel/Stress Engineering for Advanced                       | 2. "Advanced PI/SI/EMI Simulation Technology                             | Suscina Jungitaris (IBM, Octimality)               | 2. "Software Architecture for Energy Efficient Exe-                       |  |

|       | CMOS Devices: Performance Booster Technolo-                       | for 3D Co-Design" Hideki Asai (Shizuoka Univ., Japan)                    |                                                    | cution of Multicore Systems" Rephael David (LIST,                         |  |

| 12:30 | gies" Shinichi Takagi (Univ. of Tokyo, Japan)                     |                                                                          |                                                    | France)                                                                   |  |

|       |                                                                   | Lunch Break [coupon]                                                     | (12:30 - 14:00)                                    |                                                                           |  |

| 14:00 |                                                                   | Tutorial 4: 3D Integration (2) [Half day]                                |                                                    |                                                                           |  |

|       | gies (2) [Half day]                                               | Organizer: Hideki Asai (Shizuoka Univ., Japan)                           | 3. "Electrical Errors" 4. "Research Topics"        | 3. "Fabrication Technology Implications on MP-SoC" Sani Nassif (IBM, USA) |  |

|       | Organizer: Ken Uchida (Tokyo Inst. of Tech., Japan)               |                                                                          | Rand Gray (Intel, USA)                             | Soc Sain (Vassii (IBW, CSA)                                               |  |

|       | 1. "Variability and Device/Circuit Co-Design with                 | 1. "3D Cu TSV Technology" Geert Van der Plas                             | Nagib Hakim (Intel, USA)                           | 4. "Challenges and Trends for MPSoC Design"                               |  |

|       | Planar Bulk MOSFETs" Toshiro Hiramoto (Univ. of Tokyo, Japan)     | (IMEC, Belgium)                                                          |                                                    | Sungjoo Yoo (Postech, Korea)                                              |  |

|       | 2. "Three-Dimensional Devices for 22nm and Be-                    | 2. "Signal Integrity and Power Integrity Modeling                        |                                                    |                                                                           |  |

|       | yond" Arvind Kumar (IBM, USA)                                     | in High Speed Electronic Integration" Erping Li (A-STAR IHPC, Singapore) |                                                    |                                                                           |  |

| 17:00 |                                                                   | 517 IX III C, Singapore)                                                 |                                                    |                                                                           |  |

|       |                                                                                                                                                                                                                                                                                            | Registration (                                                                                                                                                                                                                                                                         | 7:00 - )                                                                                                                                                                                                                                                                                                         |                                                                                        |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 8:30  | 1K: Opening and Keynote Session I                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                  |                                                                                        |

|       | Chair: Kunihiro Asada (Univ. of Tokyo, Japan)                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                  |                                                                                        |

|       | Takayuki Kawahara (Hitachi, Japan) "Non-Volatile Mem                                                                                                                                                                                                                                       | nory and Normally-Off Computing"                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                  |                                                                                        |

| 10:00 |                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                  |                                                                                        |

|       |                                                                                                                                                                                                                                                                                            | Coffee break (10:                                                                                                                                                                                                                                                                      | 00 - 10:20)                                                                                                                                                                                                                                                                                                      |                                                                                        |

| 10:20 | 1A: Analog, Mixed-Signal & RF Verification,<br>Abstraction and Analysis                                                                                                                                                                                                                    | 1B: Emerging Memories and System Applications                                                                                                                                                                                                                                          | 1C: Advances in Model Order Reduction and Extraction Techniques                                                                                                                                                                                                                                                  | 1D: University LSI Design Contest Chairs: Masanori Hariyama (Tohoku Univ., Japan), Hi- |

|       | Chairs: Eric Keiter (Sandia National Labs, U.S.A.), Chin-<br>Fong Chiu (National Chip Implementation Center, Taiwan)                                                                                                                                                                       | Chairs: Mehdi Tahoori (Karlsruhe Inst. of Tech., Germany), Chun-Ming Huang (National Chip Implementation Center, Taiwan)                                                                                                                                                               | Chairs: Sheldon XD. Tan (Univ. of California, Riverside, U.S.A.), Genichi Tanaka (Renesas, Japan)                                                                                                                                                                                                                | roshi Kawaguchi (Kobe Univ., Japan)                                                    |

|       | 1A-1: Ying-Chih Wang, Anvesh Komuravelli, Paolo Zuliani, Edmund M. Clarke (Carnegie Mellon Univ., U.S.A.) "Analog Circuit Verification by Statistical Model Checking"                                                                                                                      | 1B-1: Miao Hu, Hai Li (Polytechnic Institute of New York Univ., U.S.A.), Yiran Chen (Univ. of Pittsburgh, U.S.A.), Xiaobin Wang (Seagate Technology, U.S.A.), Robinson Pino (AFRL/RITC, U.S.A.) "Geometry Variations Analysis of TiO <sub>2</sub> Thin-Film and Spintronic Memristors" | 1C-1: Zheng Zhang (Massachusetts Inst. of Tech., U.S.A.), Qing Wang, Ngai Wong (Univ. of Hong Kong, Hong Kong), Luca Daniel (Massachusetts Inst. of Tech., U.S.A.) "A Moment-Matching Scheme for the Passivity-Preserving Model Order Reduction of Indefinite Descriptor Systems with Possible Polynomial Parts" | (The titles of the presentations are listed in the next page)                          |

|       | 1A-2: Chenjie Gu, Jaijeet Roychowdhury (Univ. of California, Berkeley, U.S.A.) "FSM Model Abstraction for Analog/Mixed-Signal Circuits by Learning from I/O Trajectories"                                                                                                                  | 1B-2: Xiangyu Dong, Yuan Xie (Pennsylvania State Univ., U.S.A.) "AdaMS: Adaptive MLC/SLC Phase-Change Memory Design for File Storage"                                                                                                                                                  | 1C-2: Xiang Wang, Qing Wang, Zheng Zhang,<br>Quan Chen, Ngai Wong (Univ. of Hong Kong, Hong Kong)<br>"Balanced Truncation for Time-Delay Systems Via<br>Approximate Gramians"                                                                                                                                    |                                                                                        |

|       | 1A-3: Xue-Xin Liu (Univ. of California, Riverside, U.S.A.), Hao Yu (Nanyang Technological Univ., Singapore), Jacob Relles, Sheldon XD. Tan (Univ. of California, Riverside, U.S.A.) "A Structured Parallel Periodic Arnoldi Shooting Algorithm for RF-PSS Analysis based on GPU Platforms" | 1B-3: Joonsoo Kim, Joonsoo Lee, Jacob A. Abraham (Univ. of Texas, Austin, U.S.A.) "System Accuracy Estimation of SRAM-based Device Authentication"                                                                                                                                     | 1C-3: Yu Bi (Delft Univ. of Tech., Netherlands), Pieter Harpe (Holst Centre/IMEC, Netherlands), Nick van der Meijs (Delft Univ. of Tech., Netherlands) "Efficient Sensitivity-Based Capacitance Modeling for Systematic and Random Geometric Variations"                                                         |                                                                                        |

| 12:20 | <b>1A-4:</b> Hui Xu, Guoyong Shi, Xiaopeng Li (Shanghai Jiao Tong Univ., China) "Hierarchical Exact Symbolic Analysis of Large Analog Integrated Circuits By Symbolic Stamps"                                                                                                              | 1B-4: Wulong Liu, Yu Wang, Wei Liu, Yuchun Ma (Tsinghua Univ., China), Yuan Xie (Pennsylvania State Univ., U.S.A.), Huazhong Yang (Tsinghua Univ., China) "On-Chip Hybrid Power Supply System for Wireless Sensor Nodes"                                                               | 1C-4: Wenjian Yu, Chao Hu (Tsinghua Univ., China), Wangyang Zhang (Carnegie Mellon Univ., U.S.A.) "Parallel Statistical Capacitance Extraction of On-Chip Interconnects with an Improved Geometric Variation Model"                                                                                              |                                                                                        |

Lunch Break / University LSI Design Contest Discussion (12:20 - 13:40)

#### 10:20 1D: University LSI Design Contest

Chairs: Masanori Hariyama (Tohoku Univ., Japan), Hiroshi Kawaguchi (Kobe Univ., Japan)

- 1D-1: Cheng-An Chien, Yao-Chang Yang, Hsiu-Cheng Chang, Jia-Wei Chen, Cheng-Yen Chang, Jiun-In Guo, Jinn-Shyan Wang (National Chung Cheng Univ., Taiwan), Ching-Hwa Cheng (Feng Chia Univ., Taiwan) "A H.264/MPEG-2 Dual Mode Video Decoder Chip Supporting Temporal/Spatial Scalable Video"

- 1D-2: Benjamin Devlin, Makoto Ikeda, Kunihiro Asada (Univ. of Tokyo, Japan) "A Gate-level Pipelined 2.97GHz Self Synchronous FPGA in 65nm CMOS"

- 1D-3: Dan Bao, Chuan Wu, Yan Ying, Yun Chen, Xiao Yang Zeng (Fudan Univ., China) "A 4.32 mm2 170mW LDPC Decoder in 0.13 µm CMOS for WiMax/Wi-Fi Applications"

- 1D-4: Jaehyun Jeong, Tetsuya Iizuka, Toru Nakura, Makoto Ikeda, Kunihiro Asada (Univ. of Tokyo, Japan) "All-Digital PMOS and NMOS Process Variability Monitor Utilizing Buffer Ring with Pulse Counter"

- 1D-5: Takehiko Amaki, Masanori Hashimoto, Takao Onoye (Osaka Univ., Japan) "Jitter Amplifier for Oscillator-Based True Random Number Generator"

- 1D-6: Jun Furuta (Kyoto Univ., Japan), Chikara Hamanaka, Kazutoshi Kobayashi (Kyoto Inst. of Tech., Japan), Hidetoshi Onodera (Kyoto Univ., Japan) "A 65nm Flip-Flop Array to Measure Soft Error Resiliency against High-Energy Neutron and Alpha Particles"

- 1D-7: Yu-Tzu Tsai, Cheng-Chih Tsai (Feng Chia Univ., Taiwan), Cheng-An Chien (National Chung Cheng Univ., Taiwan), Ching-Hwa Cheng (Feng Chia Univ., Taiwan), Jiun-In Guo (National Chung Cheng Univ., Taiwan) "Dual-Phase Pipeline Circuit Design Automation with a Built-in Performance Adjusting Mechanism"

- **1D-8:** Lei Zhao, Daisuke Ikebuchi, Yoshiki Saito, Masahiro Kamata, Naomi Seki, Yu Kojima, Hideharu Amano (Keio Univ., Japan), Satoshi Koyama, Tatsunori Hashida, Yusuke Umahashi, Daiki Masuda, Kimiyoshi Usami (Shibaura Inst. of Tech., Japan), Kazuki Kimura, Mitaro Namiki (Tokyo Univ. of Agri. and Tech., Japan), Seidai Takeda, Hiroshi Nakamura (Univ. of Tokyo, Japan), Masaaki Kondo (Univ. of Electro-Communications, Japan) "Geyser-2: The Second Prototype CPU with Fine-grained Run-time Power Gating"

- 1D-9: Yoshiya Komatsu, Shota Ishihara, Masanori Hariyama, Michitaka Kameyama (Tohoku Univ., Japan) "An Implementation of an Asychronous FPGA Based on LEDR/Four-Phase-Dual-Rail Hybrid Architecture"

- 1D-10: Shuming Chen, Xiaowen Chen, Yi Xu, Jianghua Wan, Jianzhuang Lu, Xiangyuan Liu, Shenggang Chen (National Univ. of Defense Tech., China) "Design and Chip Implementation of a Heterogeneous Multi-core DSP"

- 1D-11: Yu-Tzu Tsai, Cheng-Chih Tsai (Feng Chia Univ., Taiwan), Cheng-An Chien (National Chung Cheng Univ., Taiwan), Ching-Hwa Cheng (Feng Chia Univ., Taiwan), Jiun-In Guo (National Chung Cheng Univ., Taiwan) "A Low-Power Management Technique for High-Performance Domino Circuits"

- 1D-12: Tomoyuki Nakabayashi, Takahiro Sasaki, Kazuhiko Ohno, Toshio Kondo (Mie Univ., Japan) "Design and Evaluation of Variable Stages Pipeline Processor Chip"

- 1D-13: Shuo-Hung Chen, Hsiao-Mei Lin, Ching-Chou Hsieh, Chih-Tsun Huang, Jing-Jia Liou, Yeh-Ching Chung (National Tsing Hua Univ., Taiwan) "TurboVG: A HW/SW Co-Designed Multi-Core OpenVG Accelerator for Vector Graphics Applications with Embedded Power Profiler"

- 1D-14: Yu-Han Yuan, Wei-Ming Chen, Hsi-Pin Ma (National Tsing Hua Univ., Taiwan) "Design and Implementation of a High Performance Closed-Loop MIMO Communications with Ultra Low Complexity Handset"

- 1D-15: Ahmed Musa, Rui Murakami, Takahiro Sato, Win Chiavipas, Kenichi Okada, Akira Matsuzawa (Tokyo Inst. of Tech., Japan) "A 58-63.6GHz Quadrature PLL Frequency Synthesizer Using Dual-Injection Technique"

- 1D-16: Wei Deng, Kenichi Okada, Akira Matsuzawa (Tokyo Inst. of Tech., Japan) "An Ultra-low-voltage LC-VCO with a Frequency Extension Circuit for Future 0.5-V Clock Generation"

- 1D-17: Yu-Hao Hsu, Yang-Syu Lin, Ching-Te Chiu, Jen-Ming Wu, Shuo-Hung Hsu, Fan-Ta Chen, Min-Sheng Kao, Wei-Chih Lai, YarSun Hsu (National Tsing Hua Univ., Taiwan) "A 32Gbps Low Propagation Delay 4x4 Switch IC for Feedback-Based System in 0.13µm CMOS Technology"

- 1D-18: Nguyen Ngoc Mai Khanh, Masahiro Sasaki, Kunihiro Asada (Univ. of Tokyo, Japan) "A Fully Integrated Shock Wave Transmitter with an On-Chip Dipole Antenna for Pulse Beam-Formability in 0.18-µm CMOS"

- 1D-19: Xin Zhang, Koichi Ishida, Makoto Takamiya, Takayasu Sakurai (Univ. of Tokyo, Japan) "An On-Chip Characterizing System for Within-Die Delay Variation Measurement of Individual Standard Cells in 65-nm CMOS"

- 1D-21: Wen Fan, Chiu-Sing Choy (Chinese Univ. of Hong Kong, Hong Kong) "Robust and Efficient Baseband Receiver Design for MB-OFDM UWB System"

- 1D-22: Yuji Osaki, Tetsuya Hirose, Nobutaka Kuroki, Masahiro Numa (Kobe Univ., Japan) "A 95-nA, 523ppm/° C, 0.6-μW CMOS Current Reference Circuit with Subthreshold MOS Resistor Ladder"

- 1D-23: Ting Gao, Wei Li, Ning Li, Junyan Ren (Fudan Univ., China) "A 80-400 MHz 74 dB-DR Gm-C Low-Pass Filter With a Unique Auto-Tuning System"

- 1D-24: Chenchang Zhan, Wing-Hung Ki (Hong Kong Univ. of Science and Tech., Hong Kong) "An Adaptively Biased Low-Dropout Regulator with Transient Enhancement"

- 1D-25: Dong Qiu, Ting Yi, Zhiliang Hong (Fudan Univ., China) "A Low-Power Triple-Mode Sigma-Delta DAC for Reconfigurable (WCDMA/TD-SCDMA/GSM) Transmitters"

- 1D-26: Mohiuddin Hafiz, Nobuo Sasaki, Kentaro Kimoto, Takamaro Kikkawa (Hiroshima Univ., Japan) "A Simple Non-coherent Solution to the UWB-IR Communication"

| 13:40 | 2A: Scheduling Techniques for Embedded Sy |

|-------|-------------------------------------------|

|       | tems                                      |

Chairs: Dip Goswami (Tech. Univ. of Munich, Germany), Naehyuck Chang (Seoul National Univ., Republic of Korea)

- **2A-1:** Pratyush Kumar, Lothar Thiele (ETH Zürich, Switzerland) "Thermally Optimal Stop-Go Scheduling of Task Graphs with Real-Time Constraints"

- **2A-2:** Yazhi Huang, Tiantian Liu, Jason Xue (City Univ. of Hong Kong, Hong Kong) "Register Allocation for Write Activity Minimization on Non-volatile Main Memory"

- **2A-3:** Vivek Chaturvedi, Gang Quan (Florida International Univ., U.S.A.) "Leakage Conscious DVS Scheduling for Peak Temperature Minimization"

- **2A-4:** Hessam Kooti, Deepak Mishra, Eli Bozorgzadeh (Univ. of California, Irvine, U.S.A.) "Reconfiguration-aware Real-Time Scheduling under QoS Constraint"

## 2B: Memory Architecture and Buffer Optimization

Chairs: Yu Wang (Tsinghua Univ., China), Yinhe Han (Chinese Academy of Sciences, China)

- **2B-1:** Bin Li, Zhen Fang, Ravi Iyer (Intel Corp., U.S.A.) "Template-based Memory Access Engine for Accelerators in SoCs"

- **2B-2:** Abdul Naeem, Xiaowen Chen, Zhonghai Lu, Axel Jantsch (Royal Inst. of Tech., Sweden) "Realization and Performance Comparison of Sequential and Weak Memory Consistency Models in Networkon-Chip based Multi-core Systems"

- **2B-3:** Wan-Ting Su, Jih-Sheng Shen, Pao-Ann Hsiung (National Chung Cheng Univ., Taiwan) "Network-on-Chip Router Design with Buffer-Stealing"

- **2B-4:** Tae-ho Shin (Seoul National Univ., Republic of Korea), Hyunok Oh (Hanyang Univ., Republic of Korea), Soonhoi Ha (Seoul National Univ., Republic of Korea) "Minimizing Buffer Requirements for Throughput Constrained Parallel Execution of Synchronous Dataflow Graph"

#### 2C: Modeling for Signal and Power Integrity

Chairs: Hideki Asai (Shizuoka Univ., Japan), Kimihiro Ogawa (STARC, Japan)

- **2C-1:** Mysore Sriram (Intel Corp., India) "A Fast Approximation Technique for Power Grid Analysis"

- **2C-2:** Khaled Salah Mohamed (Mentor Graphics, Egypt), Hani Ragai (Ain-Shams Univ., Egypt), Yehea Ismail (Nile Univ., Egypt), Alaa El Rouby (Mentor Graphics, Egypt) "Equivalent Lumped Element Models for Various n-Port Through Silicon Vias Networks"

- **2C-3:** Xuchu Hu, Matthew R. Guthaus (Univ. of California, Santa Cruz, U.S.A.) "Clock Tree Optimization for Electromagnetic Compatibility (EMC)"

- **2C-4:** Sangmin Kim, Inhak Han, Seungwhun Paik, Youngsoo Shin (KAIST, Republic of Korea) "Pulser Gating: A Clock Gating of Pulsed-Latch Circuits"

# 2D: Special Session: Emerging Memory Technologies and Its Implication on Circuit Design and Architectures

Chairs: Hideki Asai (Shizuoka Univ., Japan), Kimihiro Ogawa (STARC, Japan)

- **2D-1:** Meng-Fan Chang (National Tsing Hua Univ., Taiwan), Pi-Feng Chiu, Shyh-Shyuan Sheu (ITRI, Taiwan) "Circuit Design Challenges in Embedded Memory and Resistive RAM (RRAM) for Mobile SoC and 3D-IC"

- **2D-2:** Yiran Chen (Univ. of Pittsburgh, U.S.A.), Hai Li (Polytechnic Institute of New York Univ., U.S.A.) "Emerging Sensing Techniques for Emerging Memories"

- **2D-3:** Guangyu Sun, Dimin Liu, Jin Ouyang, Yuan Xie (Pennsylvania State Univ., U.S.A.) "A Frequent-Value Based PRAM Memory Architecture"

- **2D-4:** Wei Lu, Kuk-Hwan Kim, Ting Chang, Siddharth Gaba (Univ. of Michigan, U.S.A.) "Two-Terminal Resistive Switches (Memristors) for Memory and Logic Applications"

Coffee break (15:40 - 16:00)

## 16:00 3A: High-Level Embedded Systems Design Techniques

Chairs: Yuko Hara-Azumi (Ritsumeikan Univ., Japan), Yiran Chen (Univ. of Pittsburgh, U.S.A.)

- **3A-1:** Dip Goswami, Reinhard Schneider, Samarjit Chakraborty (Tech. Univ. of Munich, Germany) "Codesign of Cyber-Physical Systems via Controllers with Flexible Delay Constraints"

- **3A-2:** Ang-Chih Hsieh, Chun-Cheng Liu, TingTing Hwang (National Tsing Hua Univ., Taiwan) "Enhanced Heterogeneous Code Cache Management Scheme for Dynamic Binary Translation"

- **3A-3:** Deepak Gangadharan (National Univ. of Singapore, Singapore), Samarjit Chakraborty (Tech. Univ. of Munich, Germany), Roger Zimmermann (National Univ. of Singapore, Singapore) "Fast Hybrid Simulation for Accurate Decoded Video Quality Assessment on MP-SoC Platforms with Resource Constraints"

- **3A-4:** Marisha Rawlins, Ann Gordon-Ross (Univ. of Florida, U.S.A.) "On the Interplay of Loop Caching, Code Compression, and Cache Configuration"

#### 3B: Timing, Power, and Thermal Issues

Chair: Deming Chen (Univ. of Illinois, Urbana-Champaign, U.S.A.)

- **3B-1:** Jaeyong Chung (Univ. of Texas, Austin, U.S.A.), Jinjun Xiong, Vladimir Zolotov (IBM, U.S.A.), Jacob A. Abraham (Univ. of Texas, Austin, U.S.A.) "Path Criticality Computation in Parameterized Statistical Timing Analysis"

- **3B-2:** Pratyush Kumar, David Atienza (EPFL, Switzerland) "Run-Time Adaptable On-Chip Thermal Triggers"

- **3B-3:** Kan Wang, Yuchun Ma, Sheqin Dong, Yu Wang, Xianlong Hong (Tsinghua Univ., China), Jason Cong (Univ. of California, Los Angeles, U.S.A.) "Rethinking Thermal Via Planning with Timing-Power-Temperature Dependence for 3D ICs"

- **3B-4:** Jun Zhou, Senthil Jayapal, Jan Stuyt, Jos Huisken, Harmke de Groot (Holst Centre/IMEC, Netherlands) "The Impact of Inverse Narrow Width Effect on Sub-threshold Device Sizing"

#### 3C: Special Session: Post-Silicon Techniques to Counter Process and Electrical Parameter Variability

Chair: Jing-Jia Liou (National Tsing Hua Univ., Taiwan)

- **3C-1:** Ming Gao, Peter Lisherness, Kwang-Ting (Tim) Cheng (Univ. of California, Santa Barbara, U.S.A.) "Post-silicon Bug Detection for Variation Induced Electrical Bugs"

- **3C-2:** Jing-Jia Liou, Ying-Yen Chen, Chun-Chia Chen, Chung-Yen Chien, Kuo-Li Wu (National Tsing Hua Univ., Taiwan) "Diagnosis-assisted Supply Voltage Configuration to Increase Performance Yield of Cell-Based Designs"

- **3C-3:** Masanori Hashimoto (Osaka Univ. & JST, CREST, Japan) "Run-Time Adaptive Performance Compensation using On-chip Sensors"

- **3C-4:** David Brooks (Harvard Univ., U.S.A.) "The Alarms Project: A Hardware/Software Approach to Addressing Parameter Variations"

## **3D:** Special Session: Recent Advances in Verification and Debug

Chair: Chung-Yang (Ric) Huang (National Taiwan Univ., Taiwan)

- **3D-1:** Miroslav N. Velev, Ping Gao (Aries Design Automation, U.S.A.) "Automatic Formal Verification of Reconfigurable DSPs"

- **3D-2:** Chung-Yang Huang, Yu-Fan Yin, Chih-Jen Hsu (National Taiwan Univ., Taiwan), Thomas B. Huang, Ting-Mao Chang (InPA Systems, Inc., U.S.A.) "SoC HW/SW Verification and Validation"

- **3D-3:** Masahiro Fujita (Univ. of Tokyo and CREST, Japan) "Utilizing High Level Design Information to Speed up Post-silicon Debugging"

- **3D-4:** Andreas Veneris, Brian Keng (Univ. of Toronto, Canada), Sean Safarpour (Vennsa Technologies, Inc., Canada) "From RTL to Silicon: The Case for Automated Debug"

- **3D-5:** Rainer Dömer, Weiwei Chen, Xu Han (Univ. of California, Irvine, U.S.A.), Andreas Gerstlauer (Univ. of Texas, Austin, U.S.A.) "Multi-Core Parallel Simulation of System-Level Description Languages"

18:00

15:40

|       | Registration (7:30 - )                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                            |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 9:00  | 2K: Keynote Session II                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                            |  |

|       | Chair: Kunihiro Asada (Univ. of Tokyo, Japan)                                                                                                                                                                                                                                                                                                                                                                                                                | Chair: Kunihiro Asada (Univ. of Tokyo, Japan)                                                                                                                                                                                                |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                            |  |

| 10:00 | Ajoy Bose (Atrenta Inc., U.S.A.) "Managing Increasing Complexity through Higher-Level of Abstraction: What the Past Has Taught Us about the Future"                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                            |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Coffee break (10:                                                                                                                                                                                                                            | 00 - 10:20)                                                                                                                                                                                                                     |                                                                                                                                                                                                                            |  |

| 10:20 |                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4B: Novel Network-on-Chip Architecture Design                                                                                                                                                                                                | 4C: Architecture Design and Reliability                                                                                                                                                                                         | 4D: Special Session: Advanced Patterning and                                                                                                                                                                               |  |

|       | gies Chairs: Hai Li (Polytechnic Institute of New York Univ., U.S.A.), Yu Wang (Tsinghua Univ., China)                                                                                                                                                                                                                                                                                                                                                       | Chairs: Yoshinori Takeuchi (Osaka Univ., Japan), Hao<br>Yu (Nanyang Technological Univ., Singapore)                                                                                                                                          | Chairs: Shigeru Yamashita (Ritsumeikan Univ., Japan),<br>Rolf Drechsler (Univ. of Bremen, Germany)                                                                                                                              | <b>DFM for Nanolithography beyond 22nm</b> Organizer: David Z. Pan (Univ. of Texas, Austin, U.S.A.)                                                                                                                        |  |

|       | <b>4A-1:</b> Masoud Zamani (Northeastern Univ., U.S.A.), Mehdi B. Tahoori (Karlsruhe Inst. of Tech., Germany) "Variation-aware Logic Mapping for Crossbar Nano-architectures"                                                                                                                                                                                                                                                                                | <b>4B-1:</b> Sudeep Pasricha, Shirish Bahirat (Colorado State Univ., U.S.A.) "OPAL: A Multi-Layer Hybrid Photonic NoC for 3D ICs"                                                                                                            | <b>4C-1:</b> Jason Anderson (Univ. of Toronto, Canada), Qiang Wang (Xilinx, Inc., U.S.A.) "Area-Efficient FPGA Logic Elements: Architecture and Synthesis"                                                                      | <b>4D-1:</b> Soichi Inoue, Sachiko Kobayashi (Toshiba, Japan) "All-out Fight against Yield Losses by Designmanufacturing Collaboration in Nano-lithography Era"                                                            |  |

|       | <b>4A-2:</b> Tan Yan, Qiang Ma, Scott Chilstedt, Martin Wong, Deming Chen (Univ. of Illinois, Urbana-Champaign, U.S.A.) "Routing with Graphene Nanoribbons"                                                                                                                                                                                                                                                                                                  | <b>4B-2:</b> Jin Ouyang, Yuan Xie (Pennsylvania State Univ., U.S.A.) "Enabling Quality-of-Service in Nanophotonic Network-on-Chip"                                                                                                           | 4C-2: Donkyu Baek, Insup Shin, Seungwhun Paik, Youngsoo Shin (KAIST, Republic of Korea) "Selectively Patterned Masks: Structured ASIC with Asymptotically ASIC Performance"                                                     | <b>4D-2:</b> Sam Sivakumar (Intel Corp., U.S.A.) "EUV Lithography: Prospects and Challenges"                                                                                                                               |  |

|       | <b>4A-3:</b> Chia-Jen Chang, Pao-Jen Huang, Tai-Chen Chen, Chien-Nan Jimmy Liu (National Central Univ., Taiwan) "ILP-Based Inter-Die Routing for 3D ICs"                                                                                                                                                                                                                                                                                                     | <b>4B-3:</b> Cheng Liu, Lei Zhang, Yinhe Han, Xi-aowei Li (Chinese Academy of Sciences, China) "Vertical Interconnects Squeezing in Symmetric 3D Mesh Network-on-Chip"                                                                       | 4C-3: Shao-Lun Huang, Chi-An Wu, Kai-Fu Tang, Chang-Hong Hsu, Chung-Yang (Ric) Huang (National Taiwan Univ., Taiwan) "A Robust ECO Engine by Resource-Constraint-Aware Technology Mapping and Incremental Routing Optimization" | <b>4D-3:</b> Jack J.H. Chen, Faruk Krecinic, Jen-Hom Chen, Raymond P.S. Chen, Burn J. Lin (Taiwan Semiconductor Manufacturing Company, Taiwan) "Future Electron-Beam Lithography and Implications on Design and CAD Tools" |  |

| 12:20 | 4A-4: Shashikanth Bobba (Swiss Inst. of Tech. Lausanne (EPFL), Switzerland), Ashutosh Chakraborty (Univ. of Texas, Austin, U.S.A.), Olivier Thomas, Perrine Batude, Thomas Ernst, Olivier Faynot (LETI, France), David Z. Pan (Univ. of Texas, Austin, U.S.A.), Giovanni De Micheli (Swiss Inst. of Tech. Lausanne (EPFL), Switzerland) "CELONCEL: Effective Design Technique for 3-D Monolithic Integration targeting High Performance Integrated Circuits" | 4B-4: Wenmin Hu (National Univ. of Defense Tech., China), Zhonghai Lu, Axel Jantsch (Royal Inst. of Tech., Sweden), Hengzhu Liu (National Univ. of Defense Tech., China) "Power-efficient Tree-based Multicast Support for Networks-on-Chip" | 4C-4: Chi-Chen Peng, Chen Dong, Deming Chen (Univ. of Illinois, Urbana-Champaign, U.S.A.) "SETmap: A Soft Error Tolerant Mapping Algorithm for FPGA Designs with Low Power"                                                     | <b>4D-4:</b> Chul-Hong Park (Samsung Electronics, Republic of Korea), David Z. Pan (Univ. of Texas, Austin, U.S.A.), Kevin Lucas (Synopsys, U.S.A.) "Exploration of VLSI CAD Researches for Early Design Rule Evaluation"  |  |

|       | Lunch Break / Student Forum (12:20 - 13:40)                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                            |  |

#### 13:40 5A: System-Level Simulation

Chairs: Nagisa Ishiura (Kwansei Gakuin Univ., Japan), Bo-Cheng Charles Lai (National Chiao Tung Univ., Taiwan)

- 5A-1: Marius Gligor, Frédéric Pétrot (TIMA Laboratory, CNRS/INP Grenoble/UJF, France) "Handling Dynamic Frequency Changes in Statically Scheduled Cycle-Accurate Simulation"

- 5A-2: Ryo Kawahara, Kenta Nakamura, Kouichi Ono, Takeo Nakada (IBM Research, Japan), Yoshifumi Sakamoto (Global Business Services, IBM Japan, Japan) "Coarse-grained Simulation Method for Performance Evaluation a of Shared Memory System"

- 5A-3: Wei Zang, Ann Gordon-Ross (Univ. of Florida, U.S.A.) "T-SPaCS – A Two-Level Single-Pass Cache Simulation Methodology"

- 5A-4: Héctor Posadas, Luis Diaz, Eugenio Villar (Univ. of Cantabria, Spain) "Fast Data-Cache Modeling for Native Co-Simulation"

#### 5B: Resilient and Thermal-Aware NoC Design

Chairs: Michihiro Koibuchi (NII, Japan), Pao-Ann Hsiung (National Chung Cheng Univ., Taiwan)

- 5B-1: Yung-Chang Chang (ITRI, Taiwan), Ching-Te Chiu (National Tsing Hua Univ., Taiwan), Shih-Yin Lin, Chung-Kai Liu (ITRI, Taiwan) "On the Design and Analysis of Fault Tolerant NoC Architecture Using Spare Routers"

- 5B-2: Cheng Liu, Lei Zhang, Yinhe Han, Xiaowei Li (Chinese Academy of Sciences, China) "A Resilient Onchip Router Design Through Data Path Salvaging"

- 5B-3: Sudeep Pasricha, Yong Zou (Colorado State Univ., U.S.A.) "NS-FTR: A Fault Tolerant Routing Scheme for Networks on Chip with Permanent and Runtime Intermittent Faults"

- 5B-4: Zhiliang Qian, Chi-Ying Tsui (Hong Kong Univ. of Science and Tech., Hong Kong) "A Thermal-aware Application Specific Routing Algorithm for Networkon-Chip Design"

#### 5C: High-Level and Logic Synthesis

Chair: Kiyoung Choi (Seoul National Univ., Republic of

- 5C-1: Yu Pang (Chongqing Univ. of Posts and Telecommunications, China), Katarzyna Radecka, Zeljko Zilic (McGill Univ., Canada) "An Efficient Hybrid Engine to Perform Range Analysis and Allocate Integer Bitwidths for Arithmetic Circuits"

- 5C-2: Rami Beidas, Wai Sum Mong, Jianwen Zhu (Univ. of Toronto, Canada) "Register Pressure Aware Scheduling for High Level Synthesis"

- 5C-3: James Williamson (Univ. of Colorado, Boulder, U.S.A.), Yinghai Lu (Northwestern Univ., U.S.A.), Li Shang (Univ. of Colorado, Boulder, U.S.A.), Hai Zhou (Northwestern Univ., U.S.A.), Xuan Zeng (Fudan Univ., China) "Parallel Cross-Layer Optimization of High-Level Synthesis and Physical Design"

- 5C-4: Bei Yu, Sheqin Dong, Yuchun Ma, Tao Lin, Yu Wang (Tsinghua Univ., China), Song Chen, Satoshi GOTO (Waseda Univ., Japan) "Network Flow-based Simultaneous Retiming and Slack Budgeting for Low Power Design"

#### 5D: Designers' Forum: (Panel Discussion) C-P-B Co-design/Co-verification Technology for **DDR3 1.6G in Consumer Products**

Organizer: Koji Kato (Sony, Japan)

Moderator:

Makoto Nagata (Kobe Univ., Japan)

Panelists:

Keisuke Matsunami (Sony, Japan) Yoshinori Fukuba (Toshiba, Japan)

Ji Zheng (Apache Design Solutions, U.S.A.)

Jen-Tai Hsu (Global Unichip Corp., U.S.A.)

CP Hung (ASE, Taiwan)

Coffee break (15:40 - 16:00)

# 15:40

#### 16:00 6A: Design Validation Techniques

Chairs: Miroslav Velev (Aries Design Automation, U.S.A.), Kiyoharu Hamaguchi (Osaka Univ., Japan)

- **6A-1:** Brian Keng, Andreas Veneris (Univ. of Toronto, Canada) "Managing Complexity in Design Debugging with Sequential Abstraction and Refinement"

- **6A-2:** Hong-Zu Chou (National Taiwan Univ., Taiwan), Kai-Hui Chang (Avery Design Systems, Inc., U.S.A.), Sy-Yen Kuo (National Taiwan Univ., Taiwan) "Facilitating Unreachable Code Diagnosis and Debugging"

- 6A-3: Hongxia Fang (Duke Univ., U.S.A.), Zhiyuan Wang, Xinli Gu (Cisco Systems Inc., U.S.A.), Krishnendu Chakrabarty (Duke Univ., U.S.A.) "Deterministic Test for the Reproduction and Detection of Board-Level Functional Failures"

- 6A-4: Chi-Hui Lee, Che-Hua Shih, Juinn-Dar Huang, Jing-Yang Jou (National Chiao Tung Univ., Taiwan) "Equivalence Checking of Scheduling with Speculative Code Transformations in High-Level Synthesis"

#### **6B: Clock Network Design**

Chairs: Yuchun Ma (Tsinghua Univ., China), Youngsoo Shin (KAIST, Republic of Korea)

- 6B-1: Kyoung-Hwan Lim, Taewhan Kim (Seoul National Univ., Republic of Korea) "An Optimal Algorithm for Allocation, Placement, and Delay Assignment of Adjustable Delay Buffers for Clock Skew Minimization in Multi-Voltage Mode Designs"

- **6B-2:** Tak-Kei Lam, Xiaoqing Yang, Wai-Chung Tang, Yu-Liang Wu (Chinese Univ. of Hong Kong, Hong Kong) "On Applying Erroneous Clock Gating Conditions to Further Cut Down Power"

- 6B-3: Li Li (Northwestern Univ., U.S.A.), Jian Sun (Fudan Univ., China), Yinghai Lu, Hai Zhou (Northwestern Univ., U.S.A.), Xuan Zeng (Fudan Univ., China) "Low Power Discrete Voltage Assignment Under Clock Skew Scheduling"

- 6B-4: Yanling Zhi (Fudan Univ., China), Hai Zhou (Northwestern Univ., U.S.A.), Xuan Zeng (Fudan Univ., China) "A Practical Method for Multi-domain Clock Skew Optimization"

#### **6C: Advances in Routing**

Chair: David Z. Pan (Univ. of Texas, Austin, U.S.A.)

- 6C-1: Jia-Ru Chuang, Jai-Ming Lin (National Cheng Kung Univ., Taiwan) "Efficient Multi-Layer Obstacle-Avoiding Preferred Direction Rectilinear Steiner Tree Construction"

- 6C-2: Fong-Yuan Chang (National Tsing Hua Univ., Taiwan), Sheng-Hsiung Chen (SpringSoft, Taiwan), Ren-Song Tsay, Wai-Kei Mak (National Tsing Hua Univ., Taiwan) "Cut-Demand Based Routing Resource Allocation and Consolidation for Routability Enhancement"

- 6C-3: Wen-Hao Liu, Yih-Lang Li (National Chiao Tung Univ., Taiwan) "Negotiation-Based Layer Assignment for Via Count and Via Overflow Minimization"

- 6C-4: Michael Moffitt (IBM Corp., U.S.A.), C. N. Sze (IBM Research, U.S.A.) "Wire Synthesizable Global Routing for Timing Closure"

#### 6D: Designers' Forum: Emerging Technologies for Wellness Applications

Chair: Hideki Yoshizawa (Fujitsu Labs., Japan)

- **6D-1:** Masaharu Imai, Yoshinori Takeuchi, Keishi Sakanushi, Hirofumi Iwato (Osaka Univ., Japan) "Biological Information Sensing Technologies for Medical, Health Care, and Wellness Applications"

- 6D-2: Srinivasa R. Sridhara (Texas Instruments, Inc., U.S.A.) "Ultra-Low Power Microcontrollers for Portable, Wearable, and Implantable Medical Electronics"

- **6D-3:** Valer Pop, Ruben de Francisco, Hans Pflug, Juan Santana, Huib Visser, Ruud Vullers, Harmke de Groot, Bert Gyselinckx (IMEC, Netherlands) "Human++: Wireless Autonomous Sensor Technology for Body Area Networks"

- 6D-4: Koji Ara, Tomoaki Akitomi, Nobuo Sato, Satomi Tsuji, Miki Hayakawa, Yoshihiro Wakisaka, Norio Ohkubo, Rieko Otsuka, Fumiko Beniyama, Norihiko Moriwaki, Kazuo Yano (Hitachi, Ltd., Japan) "Healthcare of an Organization: Using Wearable Sensors and Feedback System for Energizing Work-

#### 18:00

|       |                                                                                                                                                                                           | Registration (                                                                                                                                                                                                             | 7:30 - )                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                    |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9:00  | 3K: Keynote Session III                                                                                                                                                                   |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                    |

|       | Chair: Kunihiro Asada (Univ. of Tokyo, Japan)                                                                                                                                             |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                    |

| 10.00 | Subhasish Mitra (Stanford Univ., U.S.A.) "Robust Systems                                                                                                                                  | s: From Clouds to Nanotubes"                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                    |

| 10:00 |                                                                                                                                                                                           | C-ff 11- (10u                                                                                                                                                                                                              | 00 10:20)                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                    |

| 10.20 | 7A. Santana I and Analysis and Ontimization                                                                                                                                               | Coffee break (10:                                                                                                                                                                                                          | <u>'</u>                                                                                                                                                                                                                                                                                                                                      | 7D. Caradal Cardan. Vintualization December                                                                                                                                                                                                                                                        |

| 10.20 | 7A: System Level Analysis and Optimization Chairs: Hiroshi Saito (Aizu Univ., Japan), Lovic Ganchier (Kyushu Univ., Japan)                                                                | 7B: NBTI and Power Gating Chairs: Kimiyoshi Usami (Shibaura Inst. of Tech., Japan), Toshio Sudo (Shibaura Inst. of Tech., Japan)                                                                                           | 7C: Physical Design for Yield Chair: Cliff Sze (IBM, U.S.A.)                                                                                                                                                                                                                                                                                  | 7D: Special Session: Virtualization, Programming, and Energy-Efficiency Design Issues of Embedded Systems  Organizer & Moderator: Tei-Wei Kuo (National Taiwan Univ., Taiwan)                                                                                                                      |

|       | <b>7A-1:</b> Junwhan Ahn, Imyong Lee, Kiyoung Choi (Seoul National Univ., Republic of Korea) "A Polynomial-Time Custom Instruction Identification Algorithm Based on Dynamic Programming" | <b>7B-1:</b> Ashutosh Chakraborty, David Z. Pan (Univ. of Texas, Austin, U.S.A.) "Controlling NBTI Degradation during Static Burn-in Testing"                                                                              | <b>7C-1:</b> Jae-Seok Yang, Jiwoo Pak (Univ. of Texas, Austin, U.S.A.), Xin Zhao, Sung Kyu Lim (Georgia Tech, U.S.A.), David Z. Pan (Univ. of Texas, Austin, U.S.A.) "Robust Clock Tree Synthesis with Timing Yield Optimization for 3D-ICs"                                                                                                  | <b>7D-1:</b> Tatsuo Nakajima, Yuki Kinebuchi, Hiromasa Shimada, Alexandre Courbot, Tsung-Han Lin (Waseda Univ., Japan) "Temporal and Spatial Isolation in a Virtualization Layer for Multi-core Processor based Information Appliances"                                                            |

|       | <b>7A-2:</b> Jiawei Huang, John Lach (Univ. of Virginia, U.S.A.) "Exploring the Fidelity-Efficiency Design Space using Imprecise Arithmetic"                                              | 7B-2: Yongho Lee (Samsung Electronics, Republic of Korea), Taewhan Kim (Seoul National Univ., Republic of Korea) "A Fine-Grained Technique of NBTI-Aware Voltage Scaling and Body Biasing for Standard Cell Based Designs" | 7C-2: Xin Gao, Luca Macchiarulo (Univ. of Hawaii, Manoa, U.S.A.) "Track Routing Optimizing Timing and Yield"                                                                                                                                                                                                                                  | <b>7D-2:</b> Jason Loew, Jesse Elwell, Dmitry Ponomarev, Patrick H. Madden (SUNY Binghamton Computer Science Department, U.S.A.) "Mathematical Limits of Parallel Computation for Embedded Systems"                                                                                                |

|       | <b>7A-3:</b> Juinn-Dar Huang, Yi-Hang Chen, Ya-Chien Ho (National Chiao Tung Univ., Taiwan) "Throughput Optimization for Latency-Insensitive System with Minimal Queue Insertion"         | <b>7B-3:</b> Ming-Chao Lee, Yu-Guang Chen, Ding-Kai Huang, Shih-Chieh Chang (National Tsing Hua Univ., Taiwan) "NBTI-Aware Power Gating Design"                                                                            | 7C-3: Shing-Tung Lin (National Tsing Hua Univ., Taiwan), Kuang-Yao Lee (Taiwan Semiconductor Manufacturing Company, Taiwan), Ting-Chi Wang (National Tsing Hua Univ., Taiwan), Cheng-Kok Koh (Purdue Univ., U.S.A.), Kai-Yuan Chao (Intel Corp., U.S.A.) "Simultaneous Redundant Via Insertion and Line End Extension for Yield Optimization" | <b>7D-3:</b> Jen-Wei Hsieh (National Taiwan Univ. of Science and Tech., Taiwan), <b>Yuan-Hao Chang</b> (National Taipei Univ. of Tech., Taiwan), <b>Wei-Li Lee</b> (National Taiwan Univ. of Science and Tech., Taiwan) "An Enhanced Leakage-Aware Scheduler for Dynamically Reconfigurable FPGAs" |

| 12:20 | <b>7A-4:</b> Yi-Siou Chen, Lih-Yih Chiou, Hsun-Hsiang Chang (National Cheng Kung Univ., Taiwan) "A Fast and Effective Dynamic Trace-based Method for Analyzing Architectural Performance" | <b>7B-4:</b> Tung-Yeh Wu, Shih-Hsin Hu, Jacob A. Abraham (Univ. of Texas, Austin, U.S.A.) "Robust Power Gating Reactivation By Dynamic Wakeup Sequence Throttling"                                                         | 7C-4: Kang Zhao, Jinian Bian (Tsinghua Univ., China) "Pruning-based Trace Signal Selection Algorithm"                                                                                                                                                                                                                                         | <b>7D-4:</b> Tiefei Zhang (Zhejiang Univ., China), Ying-Jheng Chen, Che-Wei Chang, Chuan-Yue Yang, Tei-Wei Kuo (National Taiwan Univ., Taiwan), Tianzhou Chen (Zhejiang Univ., China) "Power Management Strategies in Data Transmission"                                                           |

Lunch Break (12:20 - 13:40)

#### 13:40 8A: Modeling and Design for Variability

Chairs: Fedor G. Pikus (Mentor Graphics, U.S.A.), Hidetoshi Matsuoka (Fujitsu Laboratories, Japan)

- 8A-1: Mingzhi Gao, Zuochang Ye, Dajie Zeng, Yan Wang, Zhiping Yu (Tsinghua Univ., China) "Robust Spatial Correlation Extraction with Limited Sample via L1-Norm Penalty"

- 8A-2: Ken-ichi Shinkai, Masanori Hashimoto (Osaka Univ., Japan) "Device-Parameter Estimation with On-chip Variation Sensors Considering Random Variability"

- 8A-3: Jianxin Fang, Sachin S. Sapatnekar (Univ. of Minnesota, U.S.A.) "Accounting for Inherent Circuit Resilience and Process Variations in Analyzing Gate Oxide Reliability"

- 8A-4: Chih-Hsiang Ho, Chao Lu, Debabrata Mohapatra, Kaushik Roy (Purdue Univ., U.S.A.) "Variation-Tolerant and Self-Repair Design Methodology for Low Temperature Polycrystalline Silicon Liquid Crystal and Organic Light Emitting Diode Dis-15:40 plays"

#### 8B: Test for Reliability and Yield

Chairs: Yu Huang (Mentor Graphics, U.S.A.), Yoshinobu Higami (Ehime Univ., Japan)

- 8B-1: Fu-Wei Chen, Shih-Liang Chen, Yung-Sheng Lin, TingTing Hwang (National Tsing Hua Univ., Taiwan) "A Physical-Location-Aware Fault Redistribution for Maximum IR-Drop Reduction"

- 8B-2: Vikas Chandra, Robert Aitken (ARM, U.S.A.) "On the Impact of Gate Oxide Degradation on SRAM Dynamic and Static Write-ability"

- 8B-3: Xuan-Lun Huang, Ping-Ying Kang (National Taiwan Univ., Taiwan), Hsiu-Ming Chang (Univ. of California, Santa Barbara, U.S.A.), Jiun-Lang Huang (National Taiwan Univ., Taiwan), Yung-Fa Chou, Yung-Pin Lee, Ding-Ming Kwai, Cheng-Wen Wu (ITRI, Taiwan) "A Self-Testing and Calibration Method for Embedded Successive Approximation Register ADC"

- 8B-4: Yeonbok Lee, Takeshi Matsumoto, Masahiro Fujita (Univ. of Tokyo, Japan) "On-chip Dynamic Signal Sequence Slicing for Efficient Post-Silicon Debugging"

#### **8C: System-Level Power Optimization**

Chairs: Masanori Muroyama (Tohoku Univ., Japan), Lih-Yih Chiou (National Cheng Kung Univ., Taiwan)

- 8C-1: Abhishek Sinkar, Nam Sung Kim (Univ. of Wisconsin-Madison, U.S.A.) "AVS-Aware Power-Gate Sizing for Maximum Performance and Power Efficiency of Power-Constrained Processors"

- 8C-2: Junhe Gan (Tech. Univ. of Denmark, Denmark), Flavius Gruian (Lund Univ., Sweden), Paul Pop, Jan Madsen (Tech. Univ. of Denmark, Denmark) "Energy/Reliability Trade-offs in Fault-Tolerant Event-Triggered Distributed Embedded Systems"

- 8C-3: Jingging Mu, Roman Lysecky (Univ. of Arizona, U.S.A.) "Profile Assisted Online System-Level Performance and Power Estimation for Dynamic Reconfigurable Embedded Systems"

- 8C-4: Jiavin Li, Meikang Oiu (Univ. of Kentucky, U.S.A.), Jian-wei Niu (Beihang Univ., China), Tianzhou Chen (Zhejiang Univ., China) "Battery-Aware Task Scheduling in Distributed Mobile Systems with Lifetime Constraint"

#### 8D: Designers' Forum: State-of-The-Art SoCs and Design Methodologies

Chair: Masaitsu Nakajima (Panasonic, Japan)

- **8D-1:** Takao Suzuki (Panasonic Corp., Japan) "Advanced System LSIs for Home 3D System"

- 8D-2: Yoshiyuki Kitasho, Yu Kikuchi, Takayoshi Shimazawa, Yasuo Ohara, Masafumi Takahashi, Yoshio Masubuchi, Yukihito Oowaki (Toshiba Corp. Semiconductor Company, Japan) "Development of Low Power and High Performance Application Processor (T6G) for Multimedia Mobile Applications"

- 8D-3: Atsuki Inoue (Platform Technologies Laboratories. Japan) "Design Constraint of Fine Grain Supply Voltage Control LSI"

- **8D-4:** Masaru Takahashi (Renesas Electronics Corp., Japan) "FPGA Prototyping using Behavioral Synthesis for Improving Video Processing Álgorithm and FHD TV SoC Design"

- **8D-5:** Nobuyuki Nishiguchi (STARC, Japan) "An RTL-to-GDS2 Design Methodology for Advanced System LSI"

Coffee break (15:40 - 16:00)

#### 16:00 9A: Printability and Mask Optimization

Chairs: Murakata Masami (STARC, Japan), Zheng Shi (Zhejiang Univ., China)

- 9A-1: Duo Ding (Univ. of Texas, Austin, U.S.A.), Andres Torres, Fedor Pikus (Mentor Graphics Corp., U.S.A.), David Pan (Univ. of Texas, Austin, U.S.A.) "High Performance Lithographic Hotspot Detection using Hierarchically Refined Machine Learning"

- 9A-2: Jen-Yi Wuu (Univ. of California, Santa Barbara, U.S.A.), Fedor G. Pikus, Andres Torres (Mentor Graphics Corp., U.S.A.), Malgorzata Marek-Sadowska (Univ. of California, Santa Barbara, U.S.A.) "Rapid Layout Pattern Classification"

- 9A-3: Hongbo Zhang, Yuelin Du, Martin D. F. Wong (Univ. of Illinois, Urbana-Champaign, U.S.A.), Kai-Yuan Chao (Intel Corp., U.S.A.) "Mask Cost Reduction with Circuit Performance Consideration for Self-Aligned Double Patterning"

- 9A-4: Jian Sun (Fudan Univ., China), Yinghai Lu, Hai Zhou (Northwestern Univ., U.S.A.), Xuan Zeng (Fudan Univ., China) "Post-Routing Layer Assignment for Double Patterning"

#### 9B: Emerging Solutions in Scan Testing

Chairs: Seiji Kajihara (Kyusyu Inst. of Tech., Japan), Ting Ting Hwang (National Tsing Hua Univ., Taiwan)

- 9B-1: Yoshinobu Higami, Hiroshi Takahashi, Shinya Kobayashi (Ehime Univ., Japan), Kewal K. Saluja (Univ. of Wisconsin-Madison, U.S.A.) "Fault Simulation and Test Generation for Clock Delay Faults"

- 9B-2: Jia Li (Tsinghua Univ., China), Qiang Xu (Chinese Univ. of Hong Kong, Hong Kong), Dong Xiang (Tsinghua Univ., China) "Compression-Aware Capture Power Reduction for At-Speed Testing"

- **9B-3:** Joseph Howard, Sudhakar M Reddy (Univ. of Iowa, U.S.A.), Irith Pomeranz (Purdue Univ., U.S.A.), Bernd Becker (Univ. of Freiburg, Germany) "Fault Diagnosis Aware ATE Assisted Test Response Compaction"

- 9B-4: Hideo Fujiwara (NAIST, Japan), Katsuva Fujiwara, Hideo Tamamoto (Akita Univ., Japan) "Secure Scan Design Using Shift Register Equivalents against Differential Behavior Attack"

#### 9C: Clock and Package

Chair: Yasuhiro Takashima (Univ. of Kitakyushu, Japan)

- 9C-1: Kuan-Yu Lin, Hong-Ting Lin, Tsung-Yi Ho (National Cheng Kung Univ., Taiwan) "An Efficient Algorithm of Adjustable Delay Buffer Insertion for Clock Skew Minimization in Multiple Dynamic Supply Voltage Designs"

- 9C-2: Alireza Rakhshanfar, Jason Anderson (Univ. of Toronto, Canada) "An Integer Programming Placement Approach to FPGA Clock Power Reduction"

- 9C-3: Ren-Jie Lee, Hung-Ming Chen (National Chiao Tung Univ., Taiwan) "Row-Based Area-Array I/O Design Planning in Concurrent Chip-Package Design Flow"

- 9C-4: Qiang Ma, Hui Kong, Martin D. F. Wong (Univ. of Illinois, Urbana-Champaign, U.S.A.), Evangeline F. Y. Young (Chinese Univ. of Hong Kong, Hong Kong) "A Provably Good Approximation Algorithm for Rectangle Escape Problem with Application to PCB Routing"

#### 9D: Designers' Forum: (Panel Discussion) Advanced Packaging and 3D Technologies

Organizer: Yoshio Masubuchi (Toshiba, Japan)

Moderator:

Yaoko Nakagawa (Hitachi, Japan)

Panelists: