## 1D-18: A 25-Gb/s LD Driver with Area-Effective Inductor in a 0.18µm CMOS

<u>Takeshi Kuboki</u>, Yusuke Ohtomo, Akira Tsuchiya, Keiji Kishine and Hidetoshi Onodera

Kyoto University, NTT Electronics and University of Shiga Prefecture, Japan

# This work

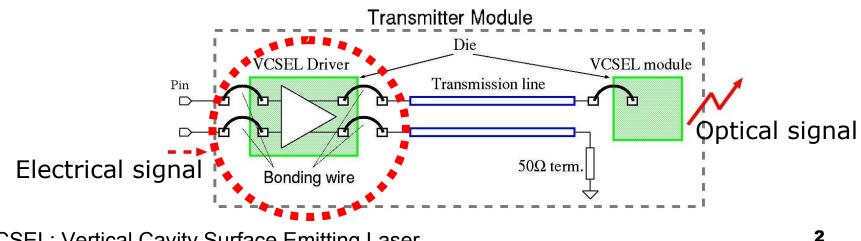

CMOS LD driver for VCSEL in Optical communication system

**Smallest and Fastest data rate in 0.18μm CMOS**

## Feature

- Small area

- Interweave 10 inductors into 2 → 80% area reduction

- High-speed operation

- Achieved 25 Gb/s operation

VCSEL: Vertical Cavity Surface Emitting Laser

# **Design summary**

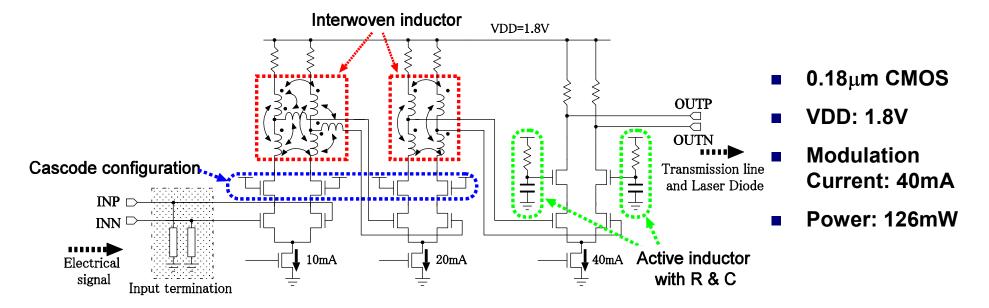

- Cascode configuration

- Reduce Miller-effect

- Interwoven inductor

- Reduce inductor's area and routing wires

- Active inductor

- □ Enhance bandwidth of output stage and keep output impedance

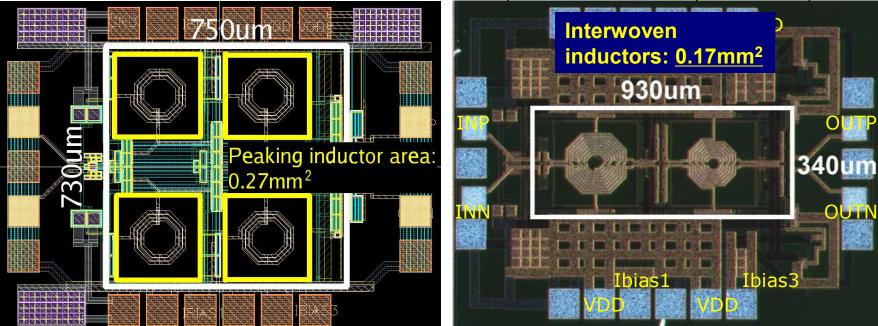

# **Area Reduction**

Widely used shunt peaking Single inductor per area

Double shunt-series peaking with mutual L Interwoven Inductor (fabricated in 0.18µm CMOS)

Inductor area0.27mm²Area / inductor0.0675mm²Circuit area0.55mm²

$\begin{array}{rcrcrcr} & -37\% & \implies & \underline{0.17 \text{ mm}^2} \\ \hline & -75\% & \implies & \underline{0.017 \text{ mm}^2} \\ \hline & -42\% & \implies & \underline{0.32 \text{ mm}^2} \end{array}$

Also interwoven inductor shorten routing wire to inductor.

➔ Parasitics can be minimized.

# Measured results and conclusion

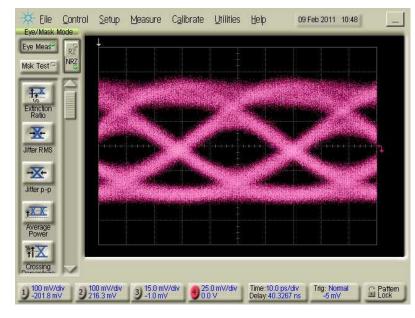

#### •Measured eye-diagram at 25Gb/s

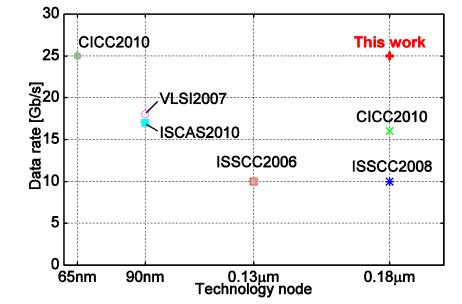

### •Comparison to other optical drivers

- Proposed LD driver exhibits <u>30% smaller chip area and operation at</u> <u>25Gb/s data rate</u>.

- $\rightarrow$  Achieves the smallest and fastest LD driver in 0.18µm CMOS processes.

### **Detailed discussion on poster 1D-18**