High-throughput Electron Beam Direct Writing of VIA Layers by Character Projection using Character Sets Based on One-dimensional VIA Arrays with Area-efficient Stencil Design

<u>Rimon IKENO<sup>†</sup></u>, Takashi MARUYAMA<sup>††</sup>, Tetsuya IIZUKA<sup>†††</sup>, Satoshi KOMATSU<sup>†</sup>, Makoto IKEDA<sup>†</sup>, and Kunihiro ASADA<sup>†</sup>

<sup>+</sup>VLSI Design and Education Center (VDEC), The University of Tokyo, <sup>++</sup>e-Shuttle, Inc.,

<sup>+++</sup>Department of Electrical Engineering and Information Systems, Graduate School of Engineering, The University of Tokyo

#### □ Introduction

- □ Character Projection (CP) overview

- Efforts for CP throughput improvement

#### Problems in applying CP to VIA layer exposure

- □ VIA number, density, and arrangement in actual designs

- Approach to improve VIA CP throughput

- One-dimensional VIA array characters

- Area-efficient stencil design & character set planning

- Layout constraints for further throughput improvement

#### **Experimental results**

- CP throughput evaluation

- CP throughput improvement

#### Summary

#### □ Introduction

- Character Projection (CP) overview

Efforts for CP throughput improvement

- Problems in applying CP to VIA layer exposure

- □ VIA number, density, and arrangement in actual designs

- Approach to improve VIA CP throughput

- One-dimensional VIA array characters

- Area-efficient stencil design & character set planning

- Layout constraints for further throughput improvement

- **Experimental results**

- **CP** throughput evaluation

- **D** CP throughput improvement

- Summary

#### **Bisectron-Beam Direct Writing (EBDW)**

Low-cost 'maskless' exposure solution

Mask cost explosion in high-resolution lithography

Low exposure throughput

1 rectangle / 1 EB shot (Variable Shaped Beam; VSB)

Limited applications: low-volume products, test chips, ...

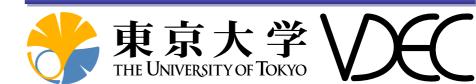

#### □ Character Projection (CP) method in EBDW

- Promising approach for high-throughput EBDW

- □ Shooting multiple figures at once as a character

- □ Characters = "Frequently-appeared layout patterns"

→ Prepared on character stencil

- □ For higher CP throughput  $\rightarrow$  more figures in 1 EB shot  $\rightarrow$  More character varieties required!

## **Overview of Character Projection (CP) EBDW**

## **Earlier Efforts for Higher CP Throughput**

## □ Cell layer (transistors & local wires)

□ 1 cell/shot (major cells only) → E<sub>CP</sub> >10

□ >1 cells/shot (cell cluster → character) cluster extraction / rearrangement

## Metal layers (interconnect routing) Tile routing: normalized wire segments Matching to predefined characters

□ VIA layers (interconnect routing) "High degree of freedom"

"High degree of freedom"

"Area-efficient stencil design (Du et al./ASP-DAC2012)

→ Just 3 VIAs in 1 character

→ Further improvement?

- Introduction

- □ Character Projection (CP) overview

- Efforts for CP throughput improvement

- Problems in applying CP to VIA layer exposure

- VIA number, density, and arrangement in actual designs

- Approach to improve VIA CP throughput

- One-dimensional VIA array characters

- Area-efficient stencil design & character set planning

- Layout constraints for further throughput improvement

- **Experimental results**

- **CP** throughput evaluation

- **D** CP throughput improvement

- Summary

## **VIA Placement Study in Actual Logic Designs**

#### P&R results of example designs(65nm)

| Design   | Area [um <sup>2</sup> ] | Cell#   | Cell pin#     | VIA1#     | VIA1 dens<br>[um <sup>-2</sup> ] |

|----------|-------------------------|---------|---------------|-----------|----------------------------------|

| 8080 CPU | 11,837                  | 4,293   | 14,623        | 14,520    | 1.23                             |

| USB 2.0  | 29,309                  | 7,725   | 28,414        | 28,301    | 0.97                             |

| AES Core | 60,270                  | 17,328  | 56,513        | 56,744    | 0.94                             |

| DCT Core | 63,907                  | 13,800  | <b>50,938</b> | 50,786    | 0.79                             |

| SPARC V8 | 1,191,590               | 229,580 | 929,474       | 927,562   | 0.78                             |

| SPARC T1 | 5,933,609               | 810,278 | 3,464,043     | 3,457,402 | 0.58                             |

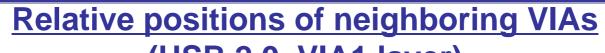

□ Observations: VIA# and density in actual designs

□ VIA1# ~ cell pin# > cell# → requiring more  $E_{CP}$  than cells

□ VIA1 density ~ 1um<sup>-2</sup> → ~1 VIA in 25 grids (1 grid=0.2um)

## **Problems in Applying CP to VIA Layers**

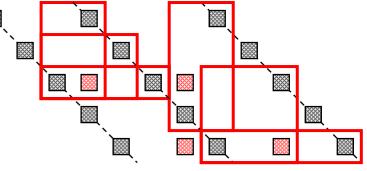

# Requirements for a VIA CP character set All possible combinations of multiple VIA arrangement More VIAs in a character for higher CP throughput Integrated within a limited stencil area

#### □ Reality of the VIA character set planning

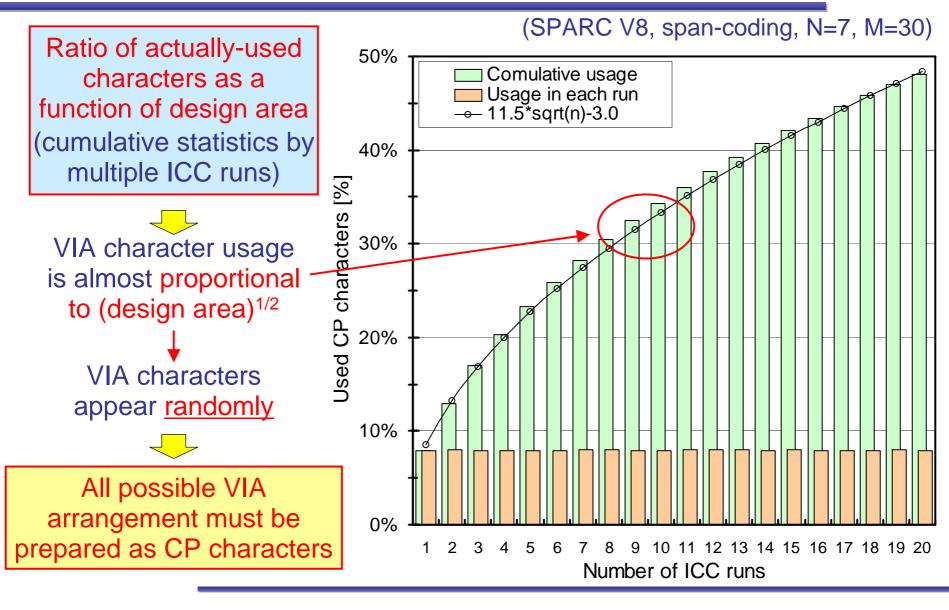

All possible VIA placement: <u>character number explosion</u>

**To achieve higher** *E<sub>CP</sub>* within stencil area limitation...

Reduce character variations even with more VIAs

Detailed VIA placement study (*next page*)

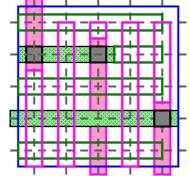

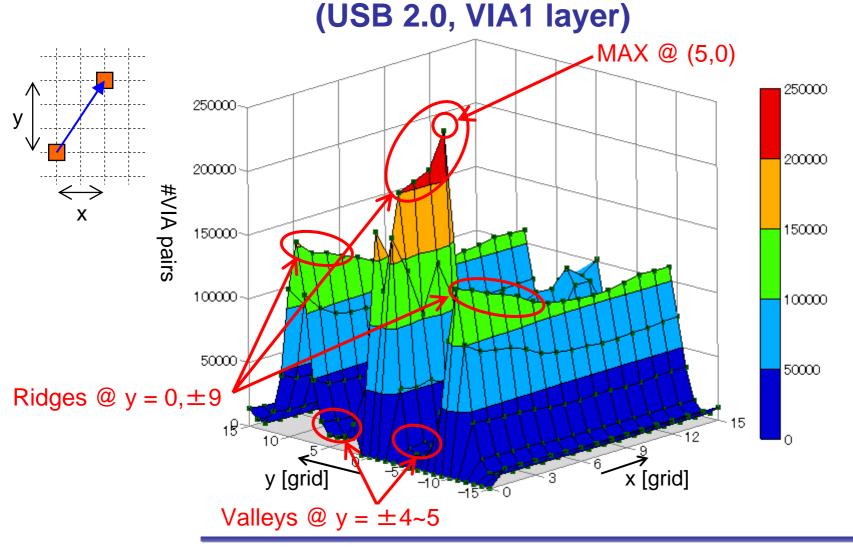

## **Detailed Study on VIA Arrangement (VIA1)**

ASP-DAC 2013

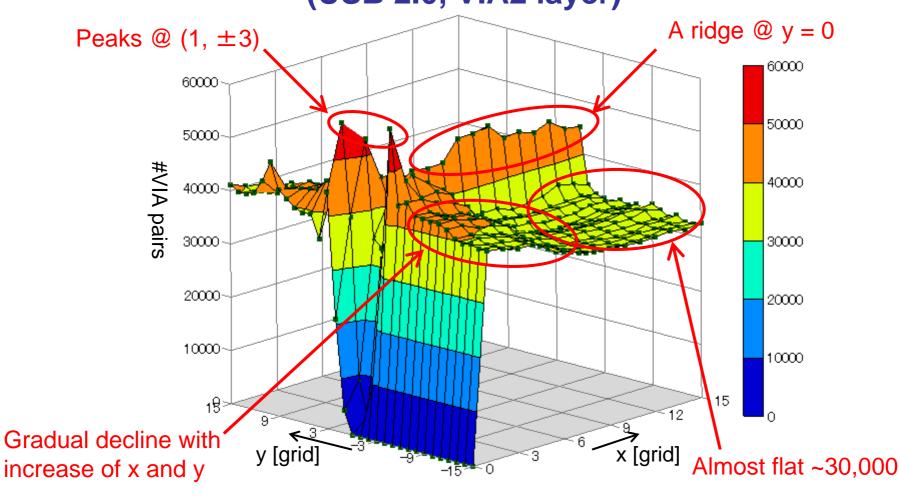

## **Detailed Study on VIA Arrangement (VIA2)**

## Relative positions of neighboring VIAs (USB 2.0, VIA2 layer)

## **Considerations on VIA Arrangement**

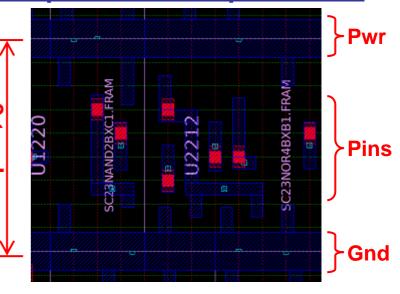

#### □ VIA1 layer (cell pin to interconnect): ridges at y=0, $\pm$ 9, valleys at y= $\pm$ 4~5

- The library cell architecture (0.2um x 9 tracks) allows cell pin access (connection) to only 4 tracks in the center

- VIAs are arranged as stripes to avoid power/ground lines

- → <u>VIA placement has strong</u> <u>correlations in the X direction</u>

#### □ VIA2 layer:

- a ridge at y=0, peaks at  $(1,\pm3)$

- Many cases of the <u>right figures</u>, but also <u>other random cases</u>

Library cell architecture & VIA1 placement for pin access

#### Introduction

- □ Character Projection (CP) overview

- **B** Efforts for CP throughput improvement

- Problems in applying CP to VIA layer exposure

- □ VIA number, density, and arrangement in actual designs

- □ Approach to improve VIA CP throughput

- One-dimensional VIA array characters

- Area-efficient stencil design & character set planning

- Layout constraints for further throughput improvement

- **Experimental results**

- CP throughput evaluation

- CP throughput improvement

- Summary

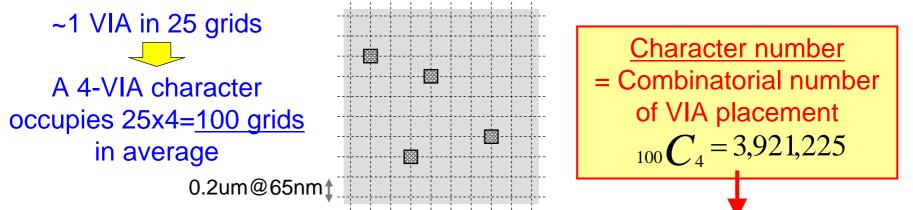

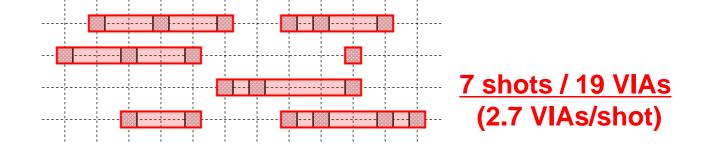

## **One Dimensional VIA Array Characters**

- Only allow <u>one-dimensional VIA arrays</u> as characters

- VIA position candidates are reduced

- $\rightarrow$  CP character variation decreases

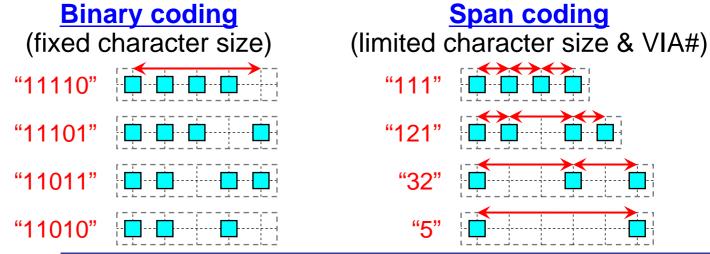

**<u>Two options</u>** in VIA array character coding schemes

ASP-DAC 2013

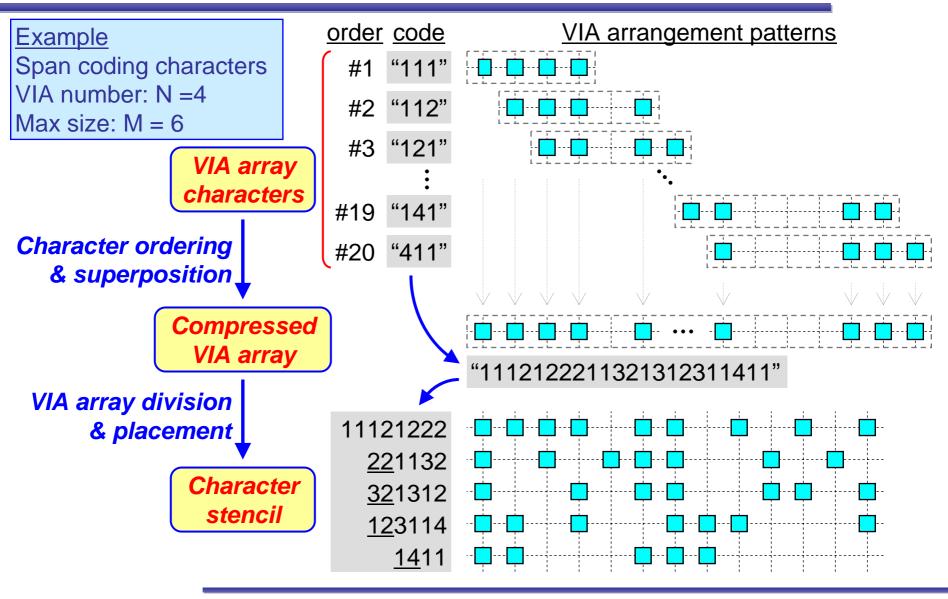

## **Area-efficient Character Stencil Design**

## **Stencil Design under Area & Size Constraints**

Character set planning for stencil design to be adopted to 14nm CP-EBDW equipment specifications

Stencil area: <u>3.6 x 10<sup>6</sup> grids</u> / Shot size: <u>30 grid x 30 grid</u>

#### **Binary coding character**

- average character size = 1 grid (after compression)

- □ character number =  $2^{M+1}$  (M: character size)

- $\square \quad \underline{3.6 \times 10^6} < 2^{M+1} \rightarrow \boxed{M=20}$

#### **Span coding character**

Some options of max VIA number (N) & max character size (M) combination

| Max<br>VIA# (N) | Max char<br>size (M) |           | Stencil<br>area [grid] | Comp.<br>ratio |

|-----------------|----------------------|-----------|------------------------|----------------|

| 7               | 30                   | 621,616   | 2,894,892              | 5.80           |

| 8               | 26                   | 726,206   | 2,625,930              | 6.65           |

| 9               | 24                   | 880,970   | 2,689,536              | 7.43           |

| 10              | 23                   | 1,097,790 | 2,989,405              | 8.13           |

| 12              | 22                   | 1,401,292 | 3,319,648              | 9.19           |

| 21              | 21                   | 1,048,576 | 2,330,190              | 9.62           |

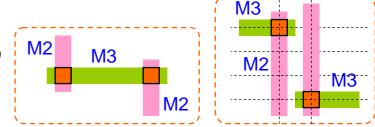

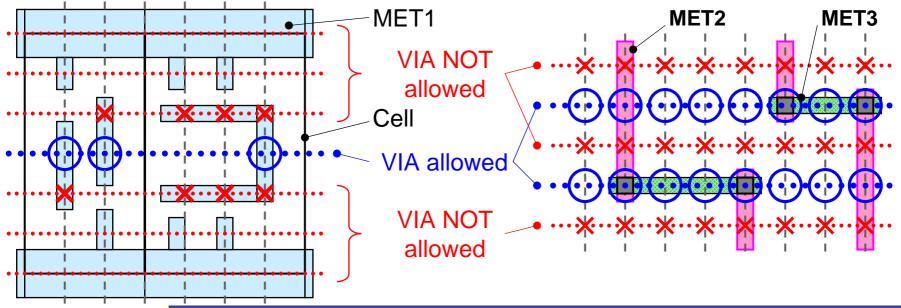

### **Layout Constraints for More CP Improvement**

Re-consideration on VIA arrangement:

More VIAs on specific tracks

$\rightarrow$  More VIAs in each shot & less shots for vacant rows

Layout constraints for VIA placement (in detail routing)

VIA2 Layer constraint

ASP-DAC 2013

How?

#### Introduction

- □ Character Projection (CP) overview

- **B** Efforts for CP throughput improvement

- Problems in applying CP to VIA layer exposure

- □ VIA number, density, and arrangement in actual designs

- Approach to improve VIA CP throughput

- One-dimensional VIA array characters

- Area-efficient stencil design & character set planning

- Layout constraints for further throughput improvement

#### **Experimental results**

- CP throughput evaluation

- CP throughput improvement

- Summary

## **Experiments and CP Throughput Evaluation**

#### **Experiments:**

- Automated place & route of 6 example circuits

- with and without the layout constraints to evaluate impact of introducing the layout constraints

#### **CP performance estimation:**

#### □ Shot count estimation

$(\text{Gshot/wafer}) = \frac{10.0 \times 100}{(\text{layout area})} \times (\text{shot}\#)$

average shot area (100Gs/w) × target shot count = <u>total shot area</u>

#### Evaluation criteria

□ Shot count target for practical use of CP-EBDW @14nm →100~173 Giga shot/wafer

□ 173 Gs/w: the minimum throughput requirement

□ 100 Gs/w: the target to allow margins of other factors

## **Results (1): CP Shot Count Estimation**

#### VIA1 shot# with/wo layout constraint (OpenSPARC T1 Core)

|                  |    |    | w/o layou           | it const | raints           | With layout constraints |               |                  |  |  |  |  |  |

|------------------|----|----|---------------------|----------|------------------|-------------------------|---------------|------------------|--|--|--|--|--|

| Character<br>set | Ν  | Μ  | Shot# VIA#<br>/shot |          | G shot<br>/wafer | Shot#                   | VIA#<br>/shot | G shot<br>/wafer |  |  |  |  |  |

| Binary coding    |    | 20 | 1,677,663           | 2.06     | 282.7            | 1,032,441               | 3.32          | 174.0            |  |  |  |  |  |

| Span<br>coding   | 7  | 30 | 1,301,248           | 2.66     | 219.3            | 858,330                 | 3.99          | (144.7           |  |  |  |  |  |

|                  | 8  | 26 | 1,437,692           | 2.40     | 242.3            | 916,924                 | 3.74          | 154.5            |  |  |  |  |  |

|                  | 9  | 24 | 1,570,835           | 2.20     | 264.7            | 986,128                 | 3.48          | 166.2            |  |  |  |  |  |

|                  | 10 | 23 | 1,597,913           | 2.16     | 269.3            | 994,780                 | 3.44          | 167.7            |  |  |  |  |  |

|                  | 12 | 22 | 1,627,868           | 2.12     | 274.3            | 1,005,818               | 3.41          | 169.5            |  |  |  |  |  |

|                  | 21 | 21 | 1,651,097           | 2.09     | 278.3            | 1,017,748               | 3.37          | 171.5            |  |  |  |  |  |

The layout constraints improved <u>VIA#/shot</u> (=CP efficiency) from <u>200~300 Gs/w range to 140~175 Gs/w</u> range

□ Span-coding (N=7, M=30) achieved the best performance

## **Results (2): CP Shot Count Summary**

#### VIA1/2 shot# of 6 example circuits with layout constraints

|          | VI            | A1              | VI            | A2              | Span adding:                                       |

|----------|---------------|-----------------|---------------|-----------------|----------------------------------------------------|

| Design   | VIA#<br>/shot | #shot<br>/wafer | VIA#<br>/shot | #shot<br>/wafer | Span-coding:<br>max VIA#: N= 7<br>max size: M = 30 |

| 8080 CPU | 5.94          | 205.7           | 3.11          | 311.9           |                                                    |

| USB 2.0  | 6.09          | 156.2           | 2.77          | 272.8           |                                                    |

| AES Core | 5.64          | 161.6           | 2.76          | 266.7           |                                                    |

| DCT Core | 4.92          | 159.2           | 2.52          | 248.3           |                                                    |

| SPARC V8 | 4.71          | 162.9           | 2.64          | 269.2           |                                                    |

| SPARC T1 | 3.99          | 144.7           | 2.31          | 236.1           |                                                    |

| Average  | 4.21          | 148.1           | 2.38          | 242.1           |                                                    |

VIA#/shot: <u>4~6</u> (VIA1), <u>2.3~3.1</u> (VIA2)

Shot#/wafer <u>148.1 Gs/w</u> (VIA1) → Target achieved 242.1 Gs/w (VIA2) → Not achieved

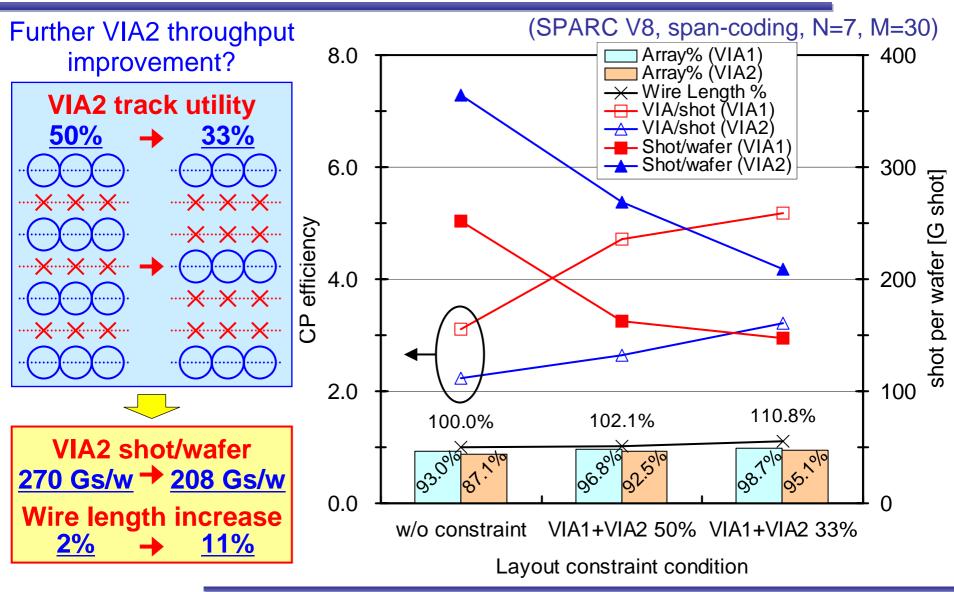

## **Results (3): Improvement by Tighter Constraints**

ASP-DAC 2013

#### Introduction

- □ Character Projection (CP) overview

- Efforts for CP throughput improvement

- Problems in applying CP to VIA layer exposure

- □ VIA number, density, and arrangement in actual designs

- Approach to improve VIA CP throughput

- One-dimensional VIA array characters

- Area-efficient stencil design & character set planning

- Layout constraints for further throughput improvement

- **Experimental results**

- **CP** throughput evaluation

- CP throughput improvement

#### **Summary**

## Summary

#### □ Difficulty in applying CP-EBDW to VIA layers

- Character explosion when increasing VIA number

- □ VIA # / density / arrangement studies in actual designs

#### One-dimensional VIA array characters

- □ <u>Character number suppression</u> by limited arrangement

- Area-efficient stencil design & character set planning

- Layout constraints for further throughput improvement

- **Experimental results and conclusions**

- □ Good CP throughput by <u>span coding</u> character set

- Improved CP throughput with little interconnect impact by tighter layout constraints

- $\Box \text{ <u>VIA1: <150 Gs/w} \rightarrow \text{target achieved (100~173 Gs/w)}$ </u>

- □ VIA2: ~200 Gs/w  $\rightarrow$  slightly missed / tuning constraints?

## Thank you!

## **Appendices**

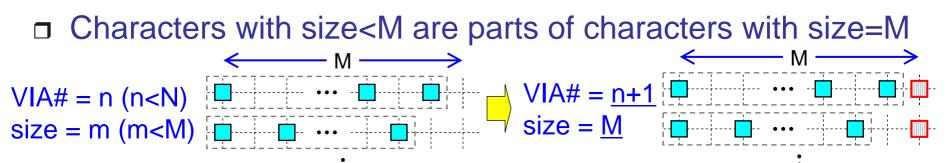

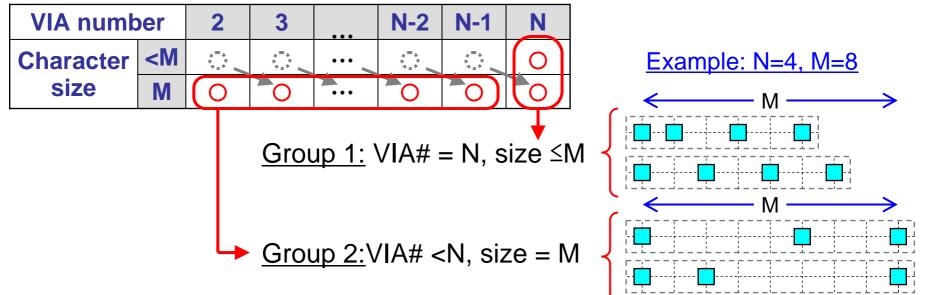

## **Required Character Sets for Span Coding**

Extended to fit to a longer char.

Required character sets are only following two groups

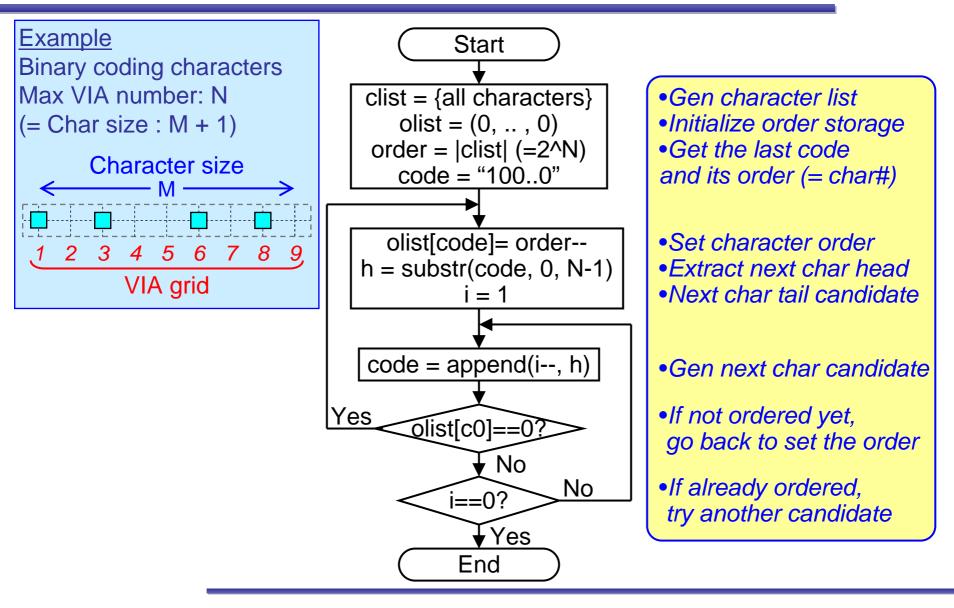

## **Example of Character Ordering Algorithm**

## **Details of Character Ordering in Page 15**

|     | S    | par  | ר כמ | oding   | cha | ara | acte | er | set | t (\ | /IA | n | um | be | er: | N = | =4, | M | lax | si | ze | : N | 1 = | 6) |   |   |

|-----|------|------|------|---------|-----|-----|------|----|-----|------|-----|---|----|----|-----|-----|-----|---|-----|----|----|-----|-----|----|---|---|

| No. |      |      |      | Order   |     |     |      |    |     |      |     |   |    |    |     |     | -   |   |     |    |    |     |     |    |   |   |

| 1   | 1    | 1    | 1    | 1       | 1   | 1   | 1    |    |     |      |     |   |    |    |     |     |     |   |     |    |    |     |     |    |   |   |

| 2   | 1    | 1    | 2    | 2       |     | 1   | 1    | 2  |     |      |     |   |    |    |     |     |     |   |     |    |    |     |     |    |   |   |

| 3   | 1    | 1    | 3    | 9       |     |     |      |    |     |      |     |   | 1  | 1  | 3   |     |     |   |     |    |    |     |     |    |   |   |

| 4   | 1    | 1    | 4    | 18      |     |     |      |    |     |      |     |   |    |    |     |     |     |   |     |    |    | 1   | 1   | 4  |   |   |

| 5   | 1    | 2    | 1    | 3       |     |     | 1    | 2  | 1   |      |     |   |    |    |     |     |     |   |     |    |    |     |     |    |   |   |

| 6   | 1    | 2    | 2    | 5       |     |     |      |    | 1   | 2    | 2   |   |    |    |     |     |     |   |     |    |    |     |     |    |   |   |

| 7   | 1    | 2    | 3    | 15      |     |     |      |    |     |      |     |   |    |    |     |     |     |   | 1   | 2  | 3  |     |     |    |   |   |

| 8   | 1    | 3    | 1    | 13      |     |     |      |    |     |      |     |   |    |    |     |     | 1   | 3 | 1   |    |    |     |     |    |   |   |

| 9   | 1    | 3    | 2    | 10      |     |     |      |    |     |      |     |   |    | 1  | 3   | 2   |     |   |     |    |    |     |     |    |   |   |

| 10  | 1    | 4    | 1    | 19      |     |     |      |    |     |      |     |   |    |    |     |     |     |   |     |    |    |     | 1   | 4  | 1 |   |

| 11  | 2    | 1    | 1    | 8       |     |     |      |    |     |      |     | 2 | 1  | 1  |     |     |     |   |     |    |    |     |     |    |   |   |

| 12  | 2    | 1    | 2    | 4       |     |     |      | 2  | 1   | 2    |     |   |    |    |     |     |     |   |     |    |    |     |     |    |   |   |

| 13  | 2    | 1    | 3    | 12      |     |     |      |    |     |      |     |   |    |    |     | 2   | 1   | 3 |     |    |    |     |     |    |   |   |

| 14  | 2    | 2    | 1    | 7       |     |     |      |    |     |      | 2   | 2 | 1  |    |     |     |     |   |     |    |    |     |     |    |   |   |

| 15  | 2    | 2    | 2    | 6       |     |     |      |    |     | 2    | 2   | 2 |    |    |     |     |     |   |     |    |    |     |     |    |   |   |

| 16  | 2    | 3    | 1    | 16      |     |     |      |    |     |      |     |   |    |    |     |     |     |   |     | 2  | 3  | 1   |     |    |   |   |

| 17  | 3    | 1    | 1    | 17      |     |     |      |    |     |      |     |   |    |    |     |     |     |   |     |    | 3  | 1   | 1   |    |   |   |

| 18  | 3    | 1    | 2    | 14      |     |     |      |    |     |      |     |   |    |    |     |     |     | 3 | 1   | 2  |    |     |     |    |   |   |

| 19  | 3    | 2    | 1    | 11      |     |     |      |    |     |      |     |   |    |    | 3   | 2   | 1   |   |     |    |    |     |     |    |   |   |

| 20  | 4    | 1    | 1    | 20      |     |     |      |    |     |      |     |   |    |    |     |     |     |   |     |    |    |     |     | 4  | 1 | 1 |

| Com | pres | ssec | d VI | A array | 1   | 1   | 1    | 2  | 1   | 2    | 2   | 2 | 1  | 1  | 3   | 2   | 1   | 3 | 1   | 2  | 3  | 1   | 1   | 4  | 1 | 1 |

ASP-DAC 2013

## **Results (4): VIA Character Usage Trend vs. Area**