A 950µW 5.5-GHz Low Voltage PLL with Digitally-Calibrated ILFD and Linearized Varactor

Sho Ikeda, Tatsuya Kamimura, Sang\_yeop Lee, Hiroyuki Ito, Noboru Ishihara, and Kazuya Masu

Solutions Research Laboratory, Tokyo Institute of Technology

ASP-DAC Jan. 21th 2014 @Suntec, Singapore

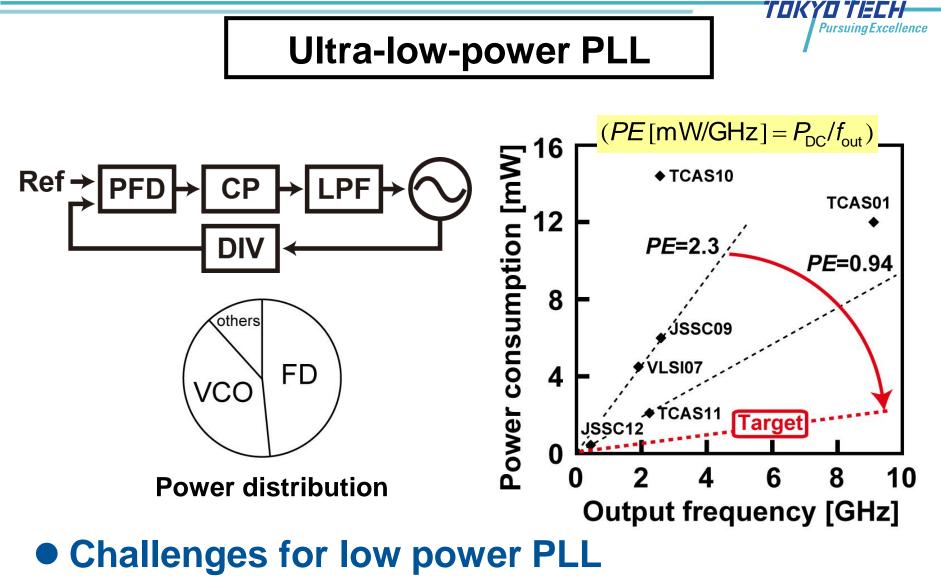

# Background

#### • Wireless Sensor Network (WSN)

req. :longer lifetimes and smaller volumes

- High power consumption in high freq. RF circuits

- Small size antenna in high freq.

- Low gain in small size antenna [1]

[1] S. Oshima, et al., VLSI 2013

ΓΠΚ

### **Research purpose**

Frequency divider, VCO

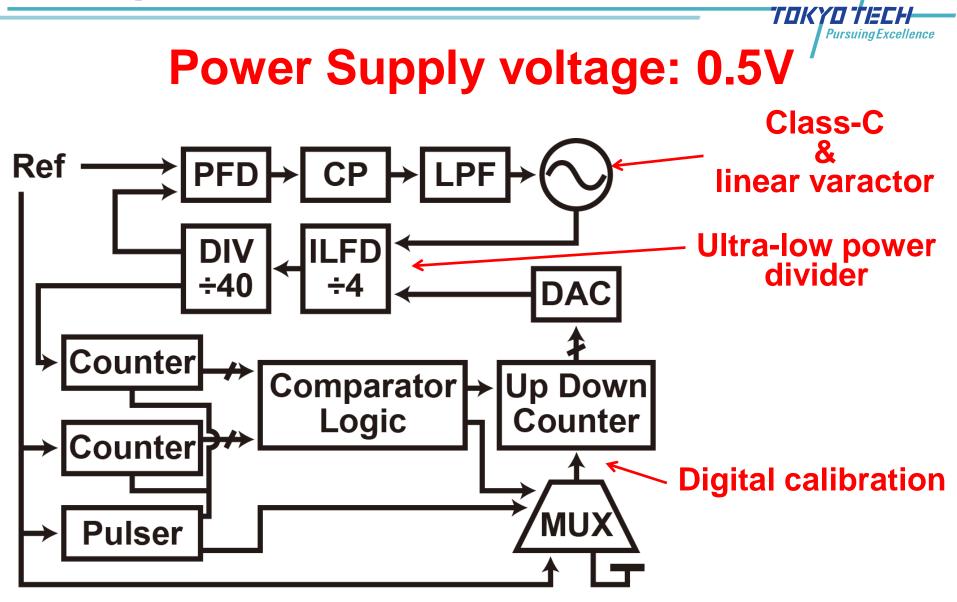

### **Proposed PLL**

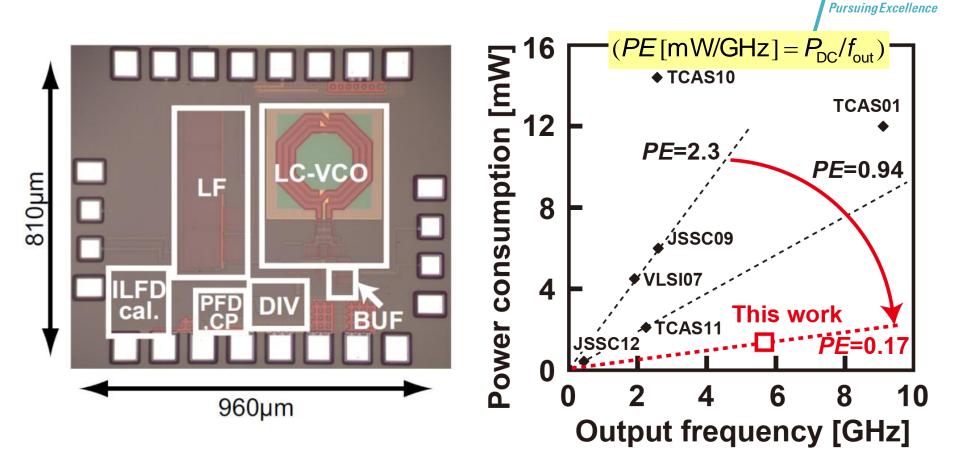

## **Results**

Superior power efficiency have been achieved!

Poster number : 1A-2

ΤΟΚ

Π