#### Time-domain Bound Analysis for Analog Circuits and Interconnect Circuits

Tan Yu<sup>1</sup>, Sheldon X.-D. Tan<sup>1</sup>, Yici Cai<sup>2</sup>, Putying Tang<sup>3</sup>

<sup>1</sup>Dept. EE, University of California, Riverside <sup>2</sup>Tsinghua University, Beijing, China <sup>3</sup>University of Electronic Science and Technology of China

#### Outline

- Background and motivation

- Review of graph based symbolic analysis

- Proposed performance bound analysis method

- Experimental results

- Summary

### Introduction

Background

Vnn

- In nanometer regime, such as 45 nm technology, process variations have huge impacts on circuit performance, yield, and reliability.

- Analog and mixed signal circuits are not only sensitive to process variations, but also suffer severely from mismatch influences, due to the inverse square root law.

- Mismatch of CMOS devices doubles for

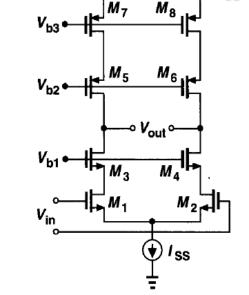

ach process generation below 90 nm. 300mm wafer Wafer A, Wafer B, Wafer C... Vb2 Vb1 Vb1 vin (a) Site-to-site variation

### **Existing approaches**

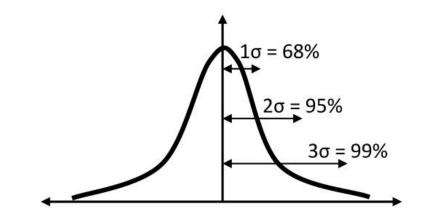

- At the nanometer scale, circuit parameters are no longer truly deterministic and present themselves as probability distributions.

- Designers must consider these effects to ensure robustness.

- Traditional corner based verification:

- not accurate enough or too expensive to cover all the corners.

- Monte-Carlo based simulation and yield estimation: general and accurate; but expensive and slow.

- Especially not efficient for high sigma and rare event analysis problems.

- 3 sigma leads to 370 samples, but 5 sigma requires 1.75million samples.

- Fast Monte Carlo methods are proposed (by reducing variations or sampling discrepancy).

- important sampling --- circuit specific (variation reduction).

- Latin hypercube sampling --- doesn't work for all circuits (sampling discrepancy reduction).

- Quasi Monte Carlo --- suffers the high-dim problems (sampling discrepancy reduction).

# Review of existing non-MC performance bound analysis

- Performance bound analysis methods emerged as attractive techniques for statistical analysis and yield estimation.

- Has potential to more effectively deal with high dimensional and sigma problems.

- Recently some non-MC performance bound methods were proposed

- [Qian, ICSICT'10] applies a control-based method to compute the bounds of the transfer function in frequency domain.

- [Hao, DAC'11] applies graph-based symbolic analysis, control-method and affine interval methods to compute the bounds in frequency domain.

- However, it uses affine interval method to compute variational transfer functions, which leads to over-conservative results.

- [Saibua, ICVSOC'11] directly uses an optimization based method to get time domain performance bound.

- Use whole circuits equations as constrains. Very expensive to enforce constrains.

# Review of existing non-MC performance bound analysis (cont'd)

- Recently some non-MC performance bound methods were proposed

- [Liu, ASPDAC'12] compute the time-domain performance bound by first getting the bound in frequency domain and then convert it into time domain.

- But the relaxation in signal can lead to issues in DC and steady state responses (TIDBA).

- [Liu, ASPDAC'13] proposed optimization based method with symbolic analysis method to compute the performance bounds in frequency domain.

- More accurate and can deal with device correlation issues.

- But only work for frequency domain

We may have divergent steady state response for TIDBA

#### Contribution

- We present a new non MC yield estimation method based on performance bound analysis in time domain.

- The exact transfer functions of linearized analog circuits are derived via a graph-based symbolic analysis.

- The time domain responses at every time step are obtained by nonlinear constrained optimization.

- It ensures accurate bounds and also resolve the device correlation issues seen in the previous methods.

- Detailed studies for the high sigma analysis using the proposed bound analysis against MC method.

- Experimental results show that the proposed method can achieve one to two orders of magnitudes speedup over HSPICE's MC on benchmark analog circuits.

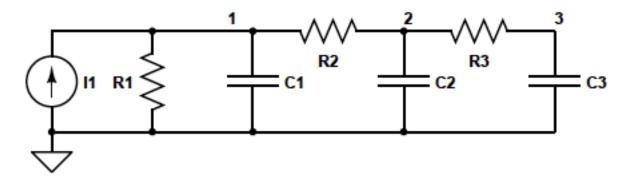

#### **Illustration by an example**

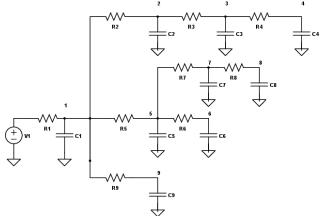

Fig. 1: RC ladder circuit

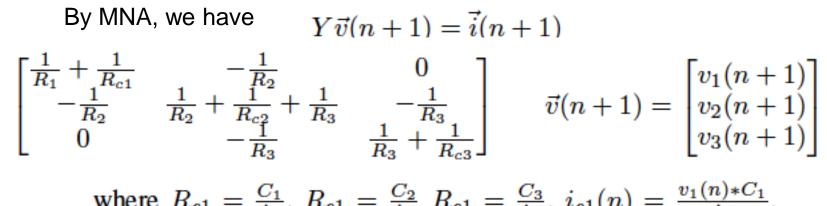

where  $R_{c1} = \frac{C_1}{\Delta t}$ ,  $R_{c1} = \frac{C_2}{\Delta t}$ ,  $R_{c1} = \frac{C_3}{\Delta t}$ ,  $i_{c1}(n) = \frac{v_1(n)*C_1}{\Delta t}$ ,  $i_{c2}(n) = \frac{v_2(n)*C_2}{\Delta t}$ ,  $i_{c3}(n) = \frac{v_3(n)*C_3}{\Delta t}$  and  $\Delta t$  is the time step size.

#### **Illustration by an example**

By the Cramer's rule, we have

$$v_i(n+1) = \frac{\det(Y_i(n+1))}{\det(Y)}$$

Where  $Y_i(n+1)$  is formed by replacing its *i*th column by i(n+1), As a result, we have

$$v_i(n+1) = \frac{f_{n,i}(C1, C2, C3, R1, R2, R3, v_1(n), v_2(n), v_3(n))}{f_{d,i}(C1, C2, C3, R1, R2, R3, v_1(n), v_2(n), v_3(n))}$$

In general, we have the following general performance expressions in terms of circuit parameters

$$v_i(n+1) = f_i(p_1, \dots, p_m, v_1(n), \dots, v_k(n)) = \frac{f_{n,i}(p_1, \dots, p_m, v_1(n), \dots, v_k(n))}{f_{d,i}(p_1, \dots, p_m)}$$

### Finding the performance bound

The we find the bound by the non-linear constrained optimization at each time step n

$\begin{array}{ll} \text{minimize} & v_i(n+1)(\mathbf{x}) = f_i(\mathbf{x}) \\ \text{subject to} & \mathbf{x}_{\text{lower}} \leq \mathbf{x} \leq \mathbf{x}_{\text{upper}}, \end{array}$

Where x = [p,v] and  $p = [p_1,p_2,...,p_m]$ ,  $v [v_1(n), v_2(n), ...,n_k(n))$

#### **Determinant Decision Diagram** $\begin{vmatrix} A & B & 0 \\ C & D & E \\ 0 & F & G \end{vmatrix} \begin{vmatrix} H \\ I \\ J \end{vmatrix} = \begin{vmatrix} k \\ 0 \\ c \end{vmatrix}$ R2 **R3** 3 2 1 **MNA** C3 \_\_\_\_ Ι **R**1 C1 <sup>-</sup> C2 🗆 DDD Creation Symbolic transfer function DDD **Expansion** $H(s) = \frac{N(s)}{D(s)} = \frac{\sum_{i=0}^{m} \hat{a}_i s^i}{\sum_{i=0}^{n} \hat{b}_i s^i}$ 1 edge 0 edge D B G F Parametric frequency response Е Good for interactive design aid DDD is efficient dealing with exponential 1 0 symbol complexity

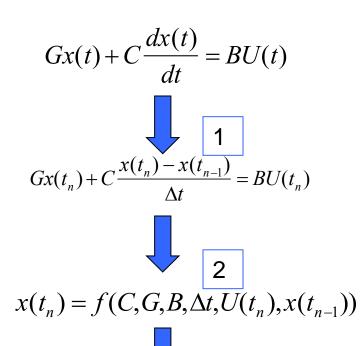

# Proposed performance bound analysis method in a nutshell

•Time-domain symbolic modified nodal analysis equations of the circuit at a time step are formed.

- •Closed-form expressions of interested performance with respective to varying parameters are derived via a graph-based symbolic analysis.

- •The lower bound and upper bound of interested performance of circuits with respect to variational parameters are obtained by nonlinear constrained optimization at each time step.

- Much more accurate and less conservative than the previous methods.

- But still finding the bounds by optimization at each step is a still relaxation to the state reachability reaching analysis.

• Detailed study for the proposed method for high-sigma analysis

- For MC method, the time complexity increases rapidly (almost exponentially) as sigma increases.

- For proposed method, run time to compute high-sigma bounds remains the same as it just uses different parameter bounds.

# Proposed performance bound analysis method

**Input:** Circuit netlist, bounds of selected parameters. **Output:** Conservative performance bound of interests

- 1: Convert the circuit C and L elements into companion models

- 2: Generate symbolic expression of closed form expressions for interesting nodes

- 3: for each time step do // Perform transient analysis

- 4: Set bounds on process variational parameters.

- 5: Set bounds on the voltage or current states from results of optimization of last time step.

- 6: Run nonlinear constrained optimization (9) which uses closed form function as the objective. to find upper bound and lower bound.

- 7: Save bound information for the optimization of next time step.

- 8: end for

- 9: Output the bound of voltage or current on every time step.

# Active-set based optimization for computing freq domain bounds

- Solutions to constrained nonlinear optimization problems

- Active-set method, Interior point method, trust region method

- Iterative approaches starting with initial guess

- Active set method:

- Two-phase iterative method

- First phase, the objective function is ignored while a feasible point is found.

- Second phase, objective is minimized while feasibility is maintained by method like quadratic programming.

- But still a localized search method.

Active set is the set of constraints that are satisfied with equality

#### **Numerical Result**

#### Experiment Setup

- DDD symbolic tool (C++ language) generates the exact transfer function expressions first.

- All the follow-up optimization based bound analysis is done in MATLAB.

- The nonlinear constrained optimization is solved by fmincon function in Matlab.

- All running time are sampled from a Linux server with a 2.4 GHz Intel Xeon Quad-Core CPU and 36GB memory.

- We compare proposed method with Monte-Carlo method.

## **RC tree circuit**

• An RC tree circuit

$R_i = 0.1\Omega$

- Interested performance is the voltage of node 8

- Variational Parameters are:

- Ri, i=1,2,3 Ci, i=1,2,3  $C_i = 0.1 pf$

- All variational parameters are in Gaussian Distribution.

- 3-sigma bound is used for parameters first

- For proposed method, variational bound for a specific variational parameter is  $[\mu 3\sigma, \mu + 3\sigma]$

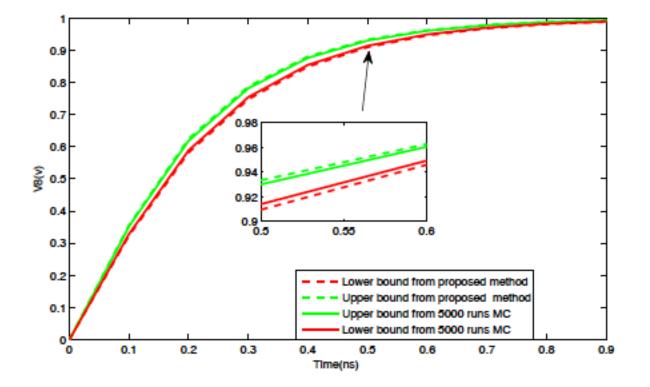

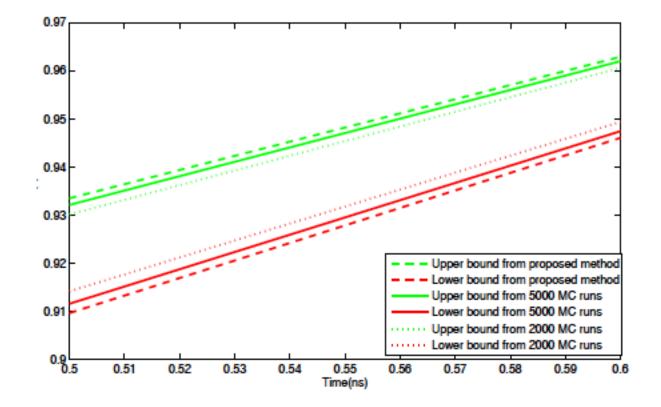

#### **Results against 5000 MC runs**

The bounds of V8 node obtained from 5000 MC run and the proposed method On the RC tree circuit. The proposed bound the MC runs.

#### The comparison between different MC runs

The comparison of bounds of V8 node from 2000 MC runs, 5000 MC runs and the proposed method. As with more MC runs, the difference becomes smaller

#### **Error and speedup studies**

| Method      | Sampling # | CPU (sec) | Voltage (v) | %Difference |

|-------------|------------|-----------|-------------|-------------|

| Monte Carlo | 2000       | 573.38    | 0.915       | 0.55        |

| Monte Carlo | 5000       | 1490.79   | 0.912       | 0.22        |

| Proposed    | 1          | 180.43    | 0.910       | N/A         |

The comparison for low bounds of V8 at t = 0.5ns for the RC tree circuit

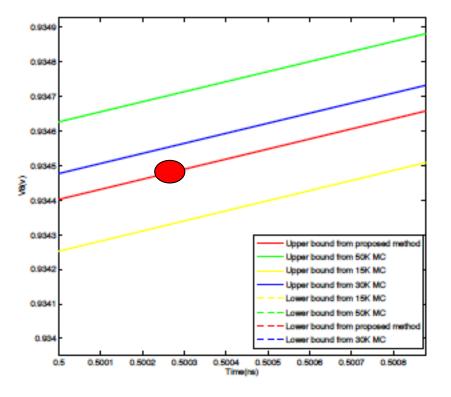

### More study for MC runs

Comparison of 3 sigma bound of V8 from proposed method and that from 15K, 30K and 50K MC runs.

**Upper Bound**

The performance bound is not monotonic functions of some parameters.

#### 0.909 0.9080 0.908 0.908 0.908 No. 0.9088 0.9084 oper bound from proposed method loper bound from 50K MC 0.908 Joper bound from 15K MC near bound from 30K MC 0.9082 r bound from 50K MC ower bound from proposed method 0.908 ower bound from 30K MC 0.5 0.5001 0.5002 0.5003 0.5004 0.5005 0.5006 0.500 Time(ns)

#### Lower Bound

Minimum is achieved when most of variational parameters are at edge of Gaussian distribution

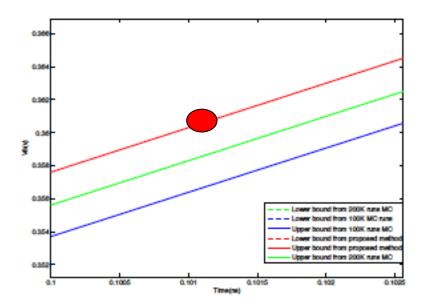

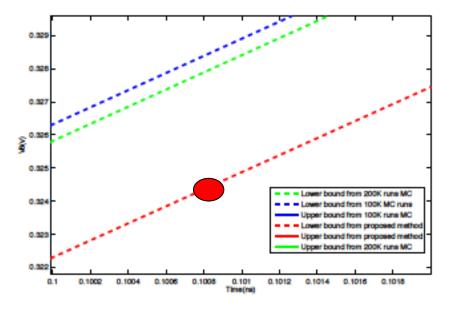

### High sigma bound results

- 4-sigma bound: The constrained range for variational parameters used in proposed method is  $[\mu 4\sigma, \mu + 4\sigma]$

- Comparison of 4 sigma bound of V8 from proposed method and that of from 100K, 200K Monte-Carlo runs.

(a) Upper bounds

(b) Low bounds

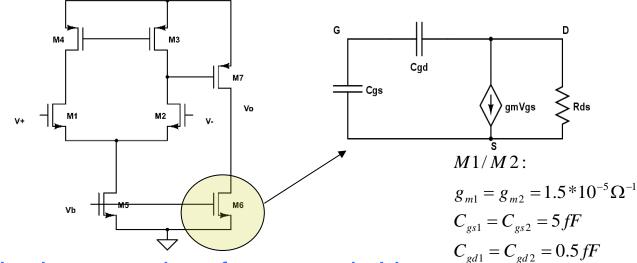

## An amplifier circuit example

• Amplifier Circuit

- The interested performance is Vo.

- The variational parameters are:

- $r_{ds5}=r_{ds6}=5*10^7\Omega$

M5/M6:

- M1: gm,Cgd,Cgs M2: gm,Cgd,Cgs M5:rds M6:rds

- All variational parameters have Gaussian Distribution.

- For proposed method, variational bound for a specific variational parameter we choose is

$$[\mu - 3\sigma, \mu + 3\sigma]$$

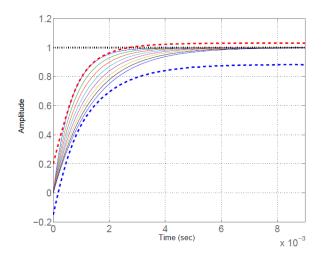

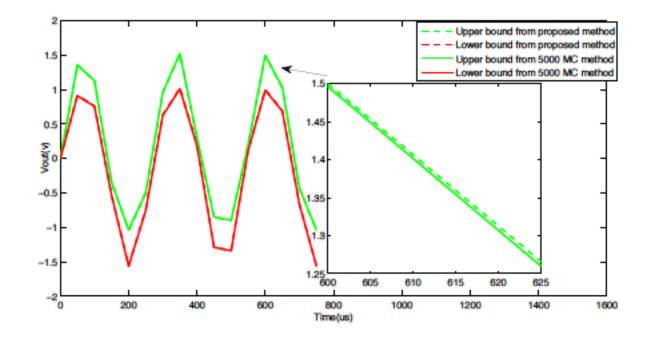

#### **Results for 5000 MC runs**

The bounds from 5000 MC runs and the proposed method for the amplifier circuit. The two funds are almost same.

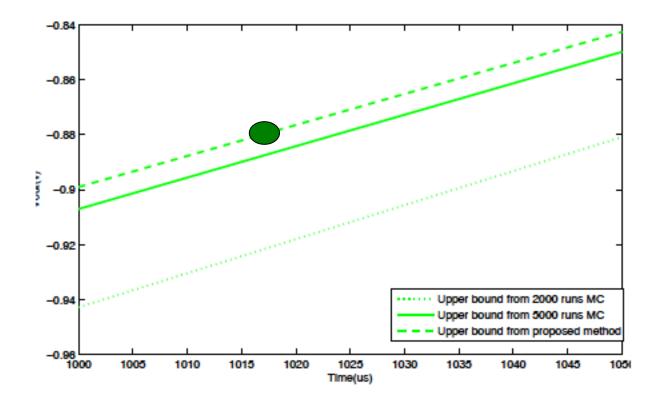

#### More detailed analysis

The comparison of upper bounds of Vout from 2000 MC, 5000 MC runs Between the MC and proposed method on the amplifier circuit. The proposed method contains all the MC runs.

#### **Error and speedup studies**

| Method      | Sampling# | CPU (sec) | Voltage (v) | %Difference |

|-------------|-----------|-----------|-------------|-------------|

| Monte Carlo | 2000      | 412.07    | -0.942      | 3.7         |

| Monte Carlo | 5000      | 1112.59   | -0.906      | 0.79        |

| Proposed    | 1         | 105.46    | -0.899      | N/A         |

### **Summary and future works**

#### Summery

- Proposed a new non-Monte-Carlo based performance bound analysis method.

- New method is based on symbolic analysis and nonlinear optimization techniques.

- More amenable for statistical analysis for high dimensional and computing high sigma bounds.

#### • Future Work

- Need to extend the method to nonlinear analog circuits.

- Need to try hierarchical DDD analysis methods to deal with large analog circuits.

- Need to further study the high sigma bound properties of the proposed method

#### Some references

- L. Qian, D. Zhou, *et al.* "Worst case analysis of linear analog circuit performance based on Kharitonov's rectangle," *Proc ICSICT'10*, pp. 181—186.

- S. Saibua, L. Qian, and D. Zhou. Worst case analysis for evaluating VLSI circuit performance bounds using an optimization method. 19th Int' I Conf on VLSI and System-on-Chip, pages 102–105, 2011.

- Z. Hao, S. X.-D. Tan, R. Shen, G. Shi, "<u>Performance bound analysis of analog circuits considering</u> <u>process variations</u>", *Proc. IEEE/ACM Design Automation Conference* (DAC'11), pp.310-315, San Diego, CA, June 2011.

- X. Liu, S. X.-D. Tan, Z. Hao, G. Shi, "<u>Time-domain performance bound analysis of analog circuits</u> <u>considering process variations</u>", ", *Proc. Asia South Pacific Design Automation Conference* (ASP-DAC'12), Sydney, Australia, pp.535-540, Jan. 2012.

- X. Liu, A. Palma-Rodriguez, S. Rodriguez-Chavez, S. X.-D. Tan, E. Tlelo-Cuautle, Y. Cai, "<u>Performance bound and yield analysis for analog\_circuits under process variations</u>", *Proc. Asia South Pacific Design Automation Conference* (ASP-DAC'13), pp.761-766, Yokohama, Japan, Jan. 2013.