#### Reliability-Configurable Mixed-Grained Reconfigurable Array Compatible with High-Level Synthesis

<u>Masanori Hashimoto</u><sup>1\*</sup>, Dawood Alnajjar<sup>1\*</sup>, Hiroaki Konoura<sup>1\*</sup>, Yukio Mitsuyama<sup>2\*</sup>, Hajime Shimada<sup>3\*</sup>, Kazutoshi Kobayashi<sup>4\*</sup>, Hiroyuki Kanbara<sup>5\*</sup>, Hiroyuki Ochi<sup>6\*</sup>, Takashi Imagawa<sup>7\*</sup>, Kazutoshi Wakabayashi<sup>8\*</sup>, Takao Onoye<sup>1\*</sup>, Hidetoshi Onodera<sup>7\*</sup>

<sup>1</sup>Osaka Univ., <sup>2</sup>Kochi Univ. of Tech., <sup>3</sup>NAIST, <sup>4</sup>Kyoto Institute of Tech., <sup>5</sup>ASTEM, <sup>6</sup>Ritsumeikan Univ., <sup>7</sup>Kyoto Univ., <sup>8</sup>NEC Corp., \*JST CREST

hasimoto@ist.osaka-u.ac.jp

## 1S-7 Background

#### NRE cost is elevating as VLSI technology advances.

• Reconfigurable VLSIs are widely used to save cost.

Guaranteeing reliability of information systems becomes a societal requirement.

Reliability of reconfigurable VLSIs is drawing much attention

especially from mission critical applications such as space and medical ones.

## 1S-7 Objective

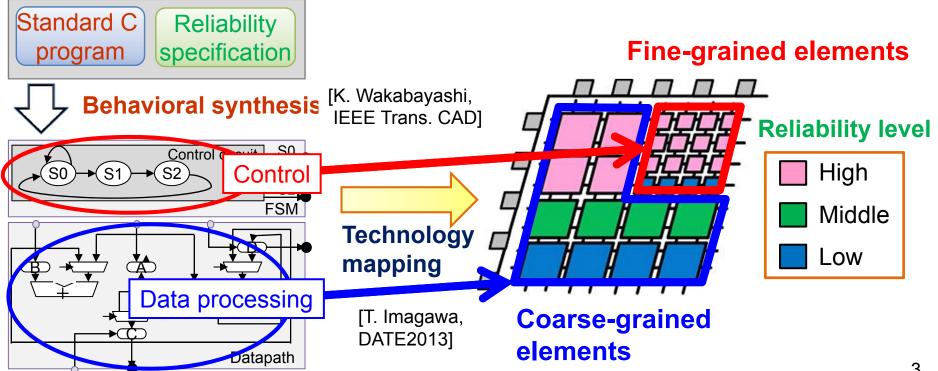

Develop a mixed-grained reliability-variable reconfigurable array enabling C-based design

- Fine-grained elements for state machine

- **Coarse-grained** elements for data processing

- Element-wise configuration to cover various apps.

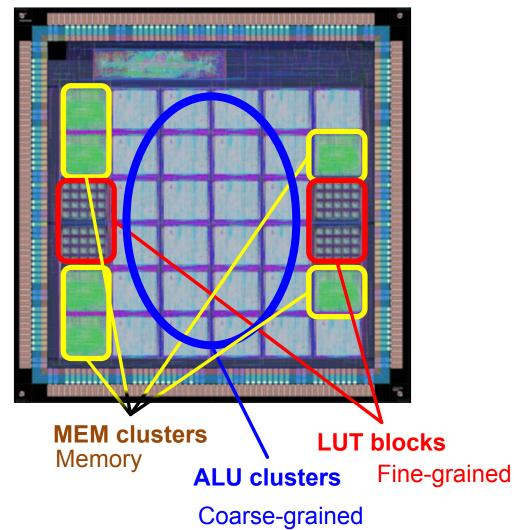

| Process      | 65nm 12ML CMOS                  |

|--------------|---------------------------------|

| Die size     | 4.2 x 4.2 mm <sup>2</sup>       |

| Config. bits | 165,312                         |

| #gates       | ALU: 120k, LUT: 4k,<br>MEM: 99k |

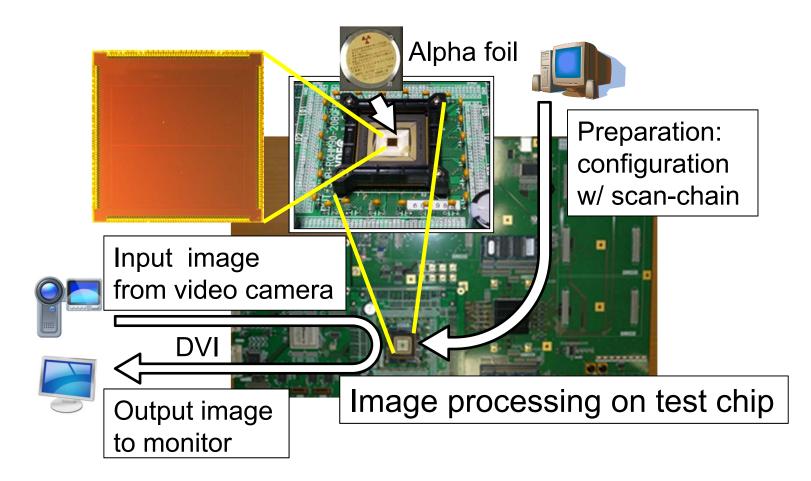

# 1S-7 Demonstration setup

To validate the functionality and reliability, a demonstration using two mappings with different reliability levels was performed.

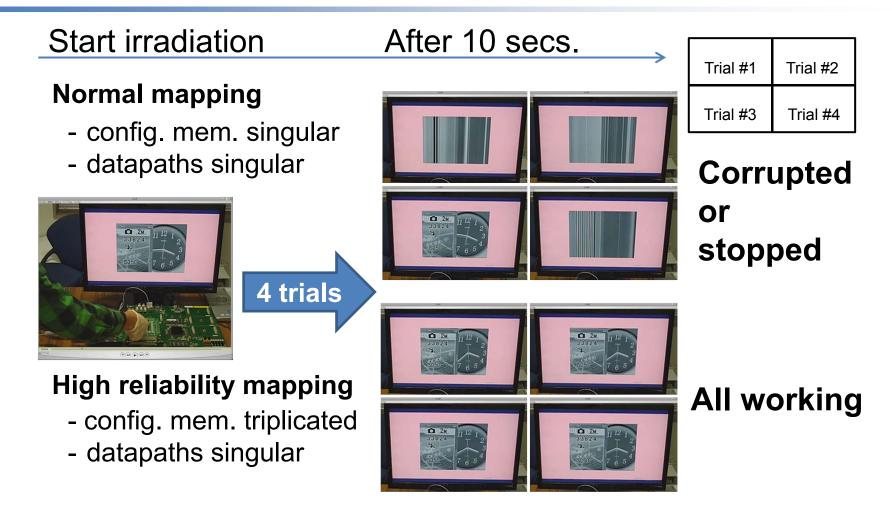

#### 1S-7 Demo: Alpha irradiation test

Single chip can cover wide reliability specifications with different mappings.