### A Racetrack Memory Based In-memory Booth Multiplier for Cryptography Application

Tao Luo<sup>1</sup>, Wei Zhang<sup>2</sup>, Bingsheng He<sup>1</sup>, Douglas Maskell<sup>1</sup>

<sup>1</sup>School of Computer Engineering, Nanyang Technological University

<sup>2</sup>Department of Electronic & Computer Engineering, Hong Kong University of Science and Technology

26<sup>th</sup> Jan 2016

- Motivations

- Background and Related Work

- Proposed Racetrack Memory Based Adder

- Proposed Booth Multiplier

- Experimental Results

- Conclusions

- Motivations

- Background and Related Work

- Proposed Racetrack Memory Based Adder

- Proposed Booth Multiplier

- Experimental Results

- Conclusions

#### **Motivation**

- Big-data scaled data center for cloud computing

- Data density

- Data security

- Asymmetric encryption schemes

- Internet-based applications

- Time and resource consuming

- Racetrack memory

- High data density, non-volatility, low static power and high speed

- Data storage medium in data center

- In-memory encryption for racetrack memory

- Avoid racetrack memory access time

- Reduce the I/O requirement

- Motivations

- Background and Related Work

- Proposed Racetrack Memory Based Adder

- Proposed Booth Multiplier

- Experimental Results

- Conclusions

#### **Background: Racetrack Memory**

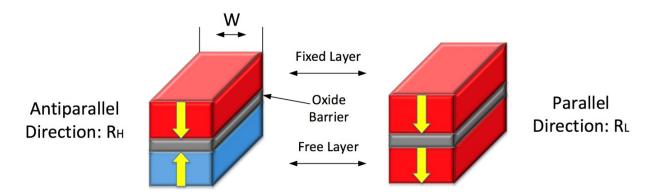

Basic structure of vertical magnetic tunnel junction

- Magnetic tunnel junction (MTJ)

- One ferromagnetic (FM) layer with fixed magnetization direction

- One FM layer with free magnetization direction

- An oxide barrier between the two FM layers

- Resistance of the MTJ

- High resistance RH: The two FM layers have antiparallel direction

- Low resistance RL: The two FM layers have parallel direction

- Two different states: "0" and "1"

#### **Background: Racetrack Memory**

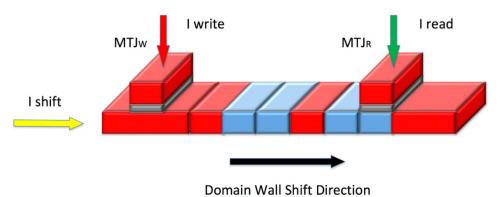

Basic structure of stripe of the racetrack memory

- Storage format

- Each unit stores one bit

- 50-100 nm wide for each unit

- The stripe can be as long as 256 bits

- Read, write, shift

- Advantage: High data density

- Disadvantage: Long access time

### **Background: Racetrack Memory**

Racetrack memory has very small characteristic parameters:

- 1 F = 45nm

- Write and shift

- Write latency is 10X as shift latency

- Write energy is 20X as shift energy

#### Main Parameters in the racetrack memory model

| Parameter | Description                            | Default value       |  |

|-----------|----------------------------------------|---------------------|--|

| $W_{RT}$  | Width of racetrack                     | $1\mathrm{F}$       |  |

| $L_D$     | Length of the domain<br>in a racetrack | $2\mathrm{F}$       |  |

| $L_{RT}$  | Length of racetrack                    | 128F                |  |

| $T_{RT}$  | Thickness of racetrack                 | $6 \mathrm{nm}$     |  |

| $W_{EN}$  | Write energy                           | 1pJ                 |  |

| $W_{DE}$  | Write latency                          | $5\mathrm{ns}$      |  |

| $S_{EN}$  | Shift energy                           | $0.051 \mathrm{pJ}$ |  |

| $S_{DE}$  | $S_{DE}$ Shift latency                 |                     |  |

### **Related Work: Magnetic Full Adder**

- Magnetic full adder

- A spintronic full adder [Meng et al., EDL'05]

- A non-volatile full adder [Matsunaga et al., APE'08]

- Racetrack memory based adder [Trinh et al., TCAS-I'13]

Magnetic full adder

### **Related Work: Magnetic Full Adder**

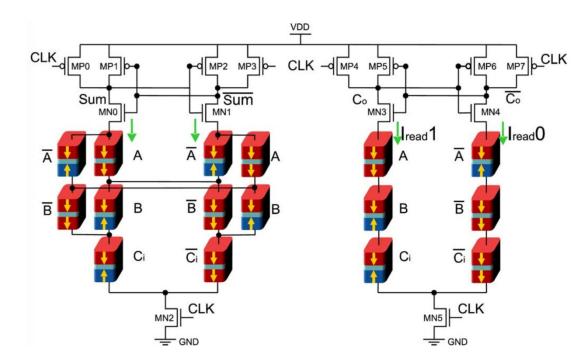

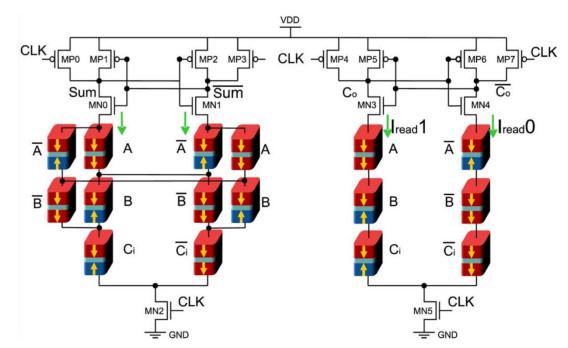

- The previous MFA [Trinh et al., TCAS-I'13]

- MTJ logic tree

- "Sum" signal and "Co" signal are realized separately

- Drawbacks

- Too many MTJs

- Too many write operations lead to high power consumption

Magnetic full adder

- Motivations

- Background and Related Work

- Proposed Racetrack Memory Based Adder

- Proposed Booth Multiplier

- Experimental Results

- Conclusions

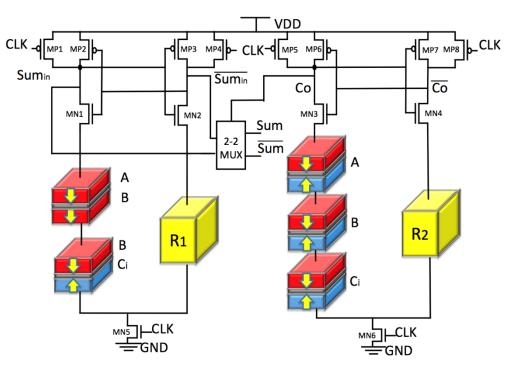

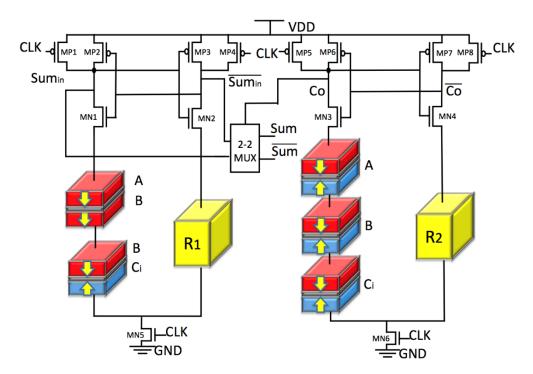

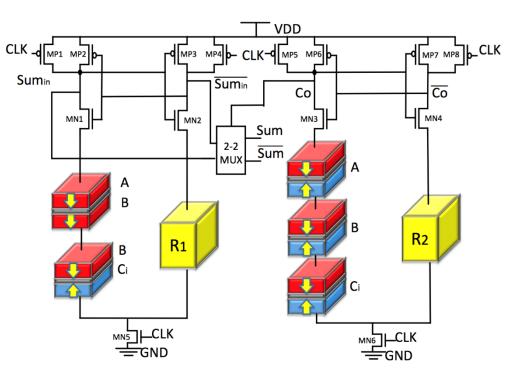

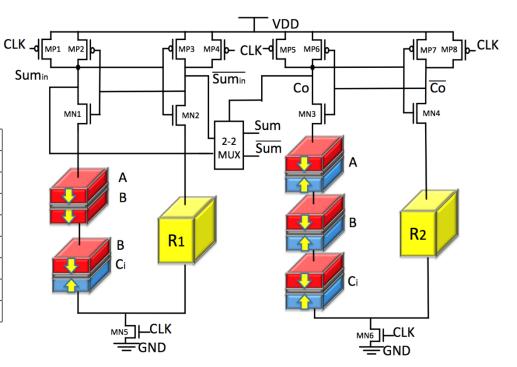

### Proposed Racetrack Memory Based Adder: Generation of Carry Out Signal

- Pre-charge sense amplifier (PCSA) is used to read the data out

- Best sensing reliability

- High power efficiency

- High speed performance

- Generation of carry out signal

- $Co = A \cdot B + A \cdot Ci + B \cdot Ci$

- A majority function

#### **Proposed Racetrack Memory Based Adder: Generation of Carry Out Signal**

#### Truth table of carry out signal

| $\frown A$ | B | $C_i$ | $R_{left}$   | $R_{right}$ | $C_o$ |

|------------|---|-------|--------------|-------------|-------|

| 0          | 0 | 0     | $3R_L$       | $2R_H$      | 0     |

| 0          | 0 | 1     | $2R_L + R_H$ | $2R_H$      | 0     |

| 0          | 1 | 0     | $2R_L + R_H$ | $2R_H$      | 0     |

| 0          | 1 | 1     | $R_L + 2R_H$ | $2R_H$      | 1     |

| 1          | 0 | 0     | $2R_L + R_H$ | $2R_H$      | 0     |

| 1          | 0 | 1     | $R_L + 2R_H$ | $2R_H$      | 1     |

| 1          | 1 | 0     | $R_L + 2R_H$ | $2R_H$      | 1     |

| 1          | 1 | 1     | $3R_H$       | $2R_H$      | 1     |

### Proposed Racetrack Memory Based Adder: Generation of "Sum" Signal

- Generation of "Sum" signal

- Sum =  $A \oplus B \oplus Ci$

- A complicated logic function

- Combination with signal "Co"

- The logic function of "Co" is a majority function

- A/B and B/Ci to form the left branch

- A MUX is added in the adder

- "Co" is used as a select signal

#### Proposed Racetrack Memory Based Adder: Generation of "Sum" Signal

Truth table of "Sum" signal

| A | B | $C_i$ | $R_{left}$  | $R_{right}$ | $C_o$ | $Sum_{in}$ | Sum |

|---|---|-------|-------------|-------------|-------|------------|-----|

| 0 | 0 | 0     | $2R_L$      | $R_H$       | 0     | 0          | 0   |

| 0 | 0 | 1     | $R_L + R_H$ | $R_H$       | 0     | 1          | 1   |

| 0 | 1 | 0     | $2R_H$      | $R_H$       | 0     | 1          | 1   |

| 0 | 1 | 1     | $R_L + R_H$ | $R_H$       | 1     | 1          | 0   |

| 1 | 0 | 0     | $R_L + R_H$ | $R_H$       | 0     | 1          | 1   |

| 1 | 0 | 1     | $2R_H$      | $R_H$       | 1     | 1          | 0   |

| 1 | 1 | 0     | $R_L + R_H$ | $R_H$       | 1     | 1          | 0   |

| 1 | 1 | 1     | $2R_L$      | $R_H$       | 1     | 0          | 1   |

- Motivations

- Background and Related Work

- Proposed Racetrack Memory Based Adder

- Proposed Booth Multiplier

- Experimental Results

- Conclusions

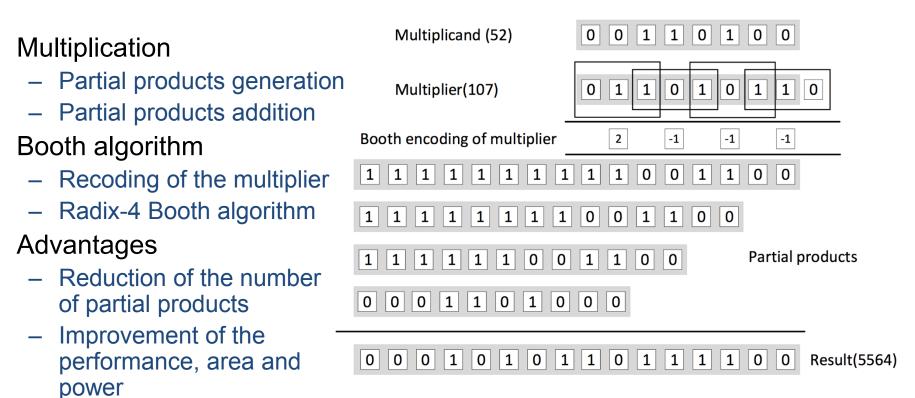

### Proposed Booth Multiplier: The Operation of The Booth Multiplication

#### The operation of the Booth multiplication

#### Proposed Booth Multiplier: Partial Products Generation

- Encoding and decoding

- Y<sub>2i-1</sub>, Y<sub>2i</sub> and Y<sub>2i+1</sub> are digits of the input blocks of the multiplier

- "0" means the partial product equals to zero multiplying the multiplicand.

- It is the same for "1\*", "2\*",

"-1\*" and "-2\*".

### Encoding and decoding regarding to block inputs

| $Y_{2i-1}$ | $Y_{2i}$ | $Y_{2i+1}$ | Partial Product  |

|------------|----------|------------|------------------|

| 0          | 0        | 0          | 0* Multiplicand  |

| 0          | 0        | 1          | 1* Multiplicand  |

| 0          | 1        | 0          | 1* Multiplicand  |

| 0          | 1        | 1          | 2* Multiplicand  |

| 1          | 0        | 0          | -2* Multiplicand |

| 1          | 0        | 1          | -1* Multiplicand |

| 1          | 1        | 0          | -1* Multiplicand |

| 1          | 1        | 1          | 0* Multiplicand  |

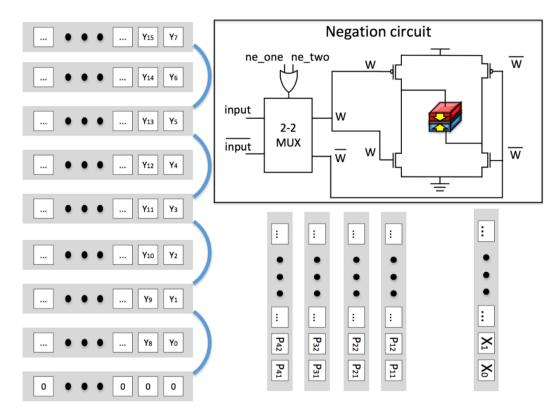

#### Proposed Booth Multiplier: Partial Products Generation

### Control signals for the partial products generation

- Control signals

- "zero" corresponds to "0\*"

- "one" corresponds to "1\*"

- "two" corresponds to "2\*"

- "ne\_two" corresponds to "-2\*"

- "ne\_one" corresponds to "-1\*"

$$\begin{aligned} zero &= Y_{2i-1} \cdot Y_{2i} \cdot Y_{2i+1} + Y_{2i-1} \cdot Y_{2i} \cdot Y_{2i+1} \\ one &= \overline{Y_{2i-1}} \cdot \overline{Y_{2i}} \cdot Y_{2i+1} + \overline{Y_{2i-1}} \cdot Y_{2i} \cdot \overline{Y_{2i+1}} \\ two &= \overline{Y_{2i-1}} \cdot Y_{2i} \cdot Y_{2i+1} \\ ne\_two &= Y_{2i-1} \cdot \overline{Y_{2i}} \cdot \overline{Y_{2i+1}} \\ ne\_one &= Y_{2i-1} \cdot \overline{Y_{2i}} \cdot Y_{2i+1} + Y_{2i-1} \cdot Y_{2i} \cdot \overline{Y_{2i+1}} \end{aligned}$$

#### Proposed Booth Multiplier: Partial Products Generation

- Partial products are generated in parallel

- Five kinds of transformations

- "remain"

- "left-shifting"

- "plusing-one"

- "setting-to-zero"

- "negation"

- Realization of the five transformations

### Data organization for generation of partial products

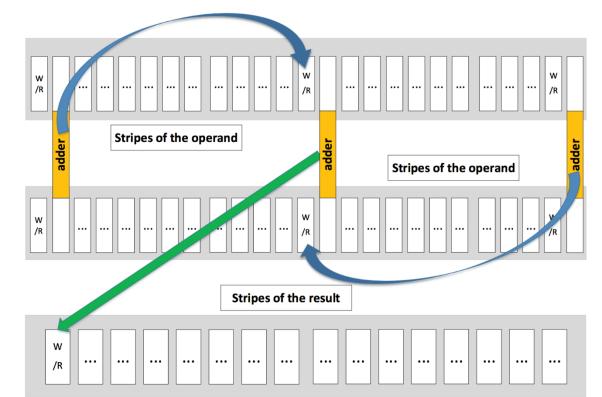

### Proposed Booth Multiplier: Addition of Partial Products

- Pipelined structure

- Racetrack memory is used as the stage register

- Pipeline can be very deep

- Advantages

- Easy to realize

- Efficient in terms of racetrack memory resource

- High scalability

#### The pipelined addition based on racetrack memory

- Motivations

- Background and Related Work

- Proposed Racetrack Memory Based Adder

- Proposed Booth Multiplier

- Experimental Results

- Conclusions

#### **Experimental Result:** 1-bit magnetic full adder

- CMOS 45*nm* design kit

- A model of perpendicular magnetic anisotropy (PMA) racetrack memory based on CoFeB/MgO structure

|                 | CMOS        | Previous    | Proposed     |

|-----------------|-------------|-------------|--------------|

|                 | FA          | MFA         | MFA          |

| Delay           | 100 ps      | 180 ps      | $240 \ ps$   |

| Energy          | 15 fJ       | 7.6 fJ      | 19 f J       |

| Write operation | NA          | 16          | 7            |

| Area            | $11.04um^2$ | $3.36 um^2$ | $1.142 um^2$ |

#### **Comparison of the three adders**

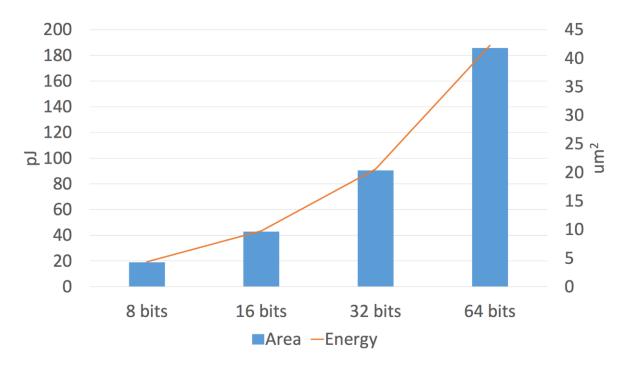

### **Experimental Result:**

#### **Racetrack memory based Booth multiplier**

### Energy per bit and area of our proposed multipliers with different input length

### Conclusions

- Propose a compact racetrack memory based adder to reduce the number of write operation

- Design Booth encoder and decoder of the inmemory Booth multiplier for generating the partial products in parallel

- Implement a pipelined in-memory Booth multiplier for the encryption application in racetrack memory based data center

# Thank you!

## **Questions?**