### Extending Trace History Through Tapered Summaries in Post-silicon Validation

<u>Sandeep Chandran</u><sup>†</sup>, Preeti Ranjan Panda<sup>†</sup>, Smruti R. Sarangi<sup>†</sup>, Deepak Chauhan<sup>‡</sup>, Sharad Kumar<sup>‡</sup>

<sup>+</sup> Department of Computer Science and Engineering, IIT Delhi, New Delhi, India

<sup>‡</sup> Freescale Semiconductors Pvt Ltd, Noida, India

# **Motivation**

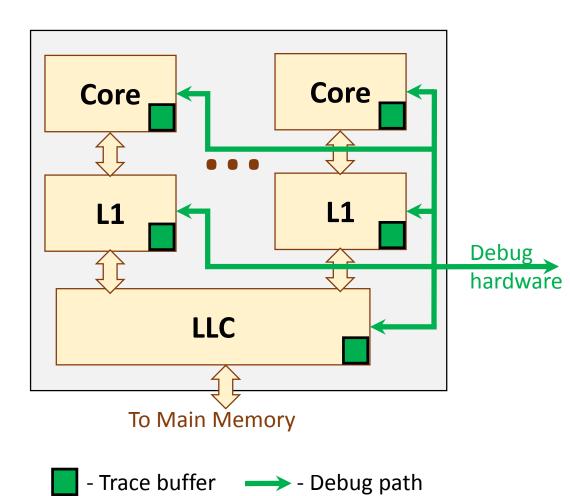

### **Traditional Chips**

- Increasing complexity

- Pre-silicon verification does not scale

- Higher likelihood of <u>design bugs</u> in first-silicon

### Solution

• Add hardware hooks into silicon that help debugging

### **Associated Problem**

- Which hooks are most helpful?

- Balance visibility and area overhead

# **Motivation**

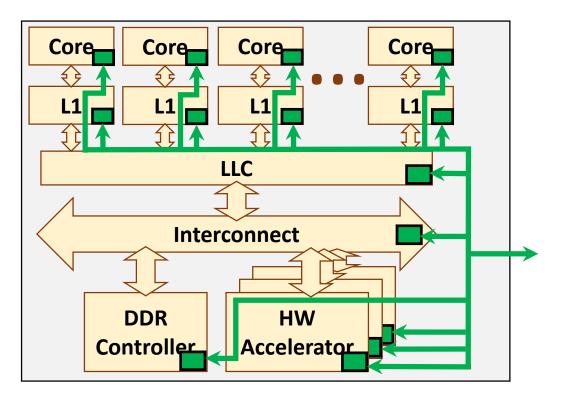

**Modern Chips**

• Further increase in complexity due to tighter integration of modules

#### **Even More Problems!**

- increased inter-module interactions

- increased amount of traces to capture, transfer off-chip, and analyze

### Traditional debug hardware does not scale!

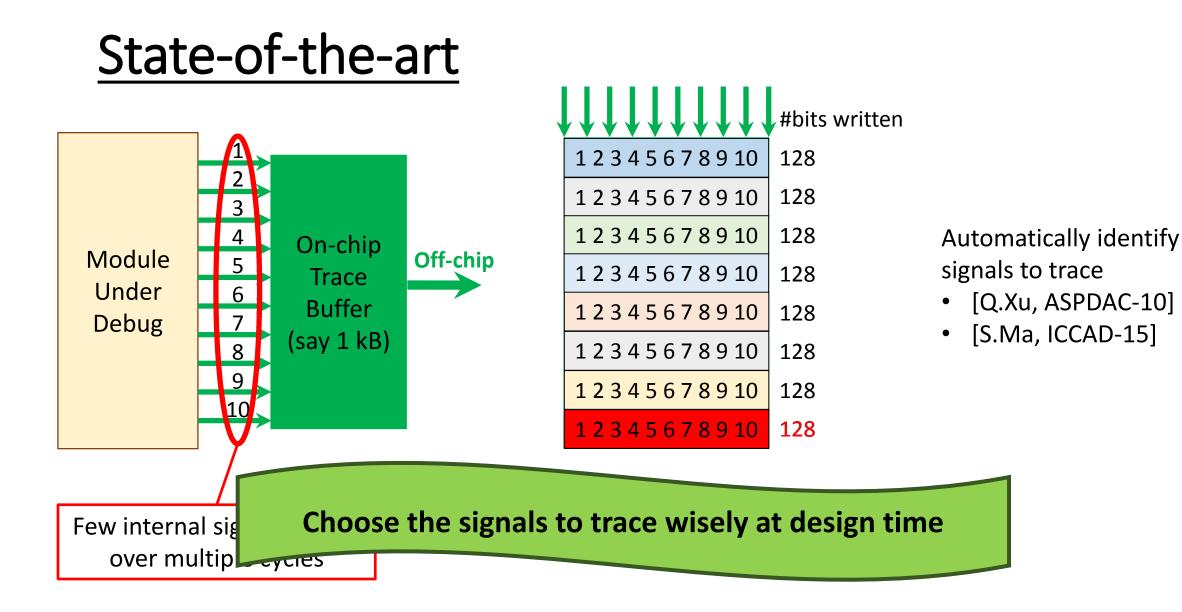

## **Observations**

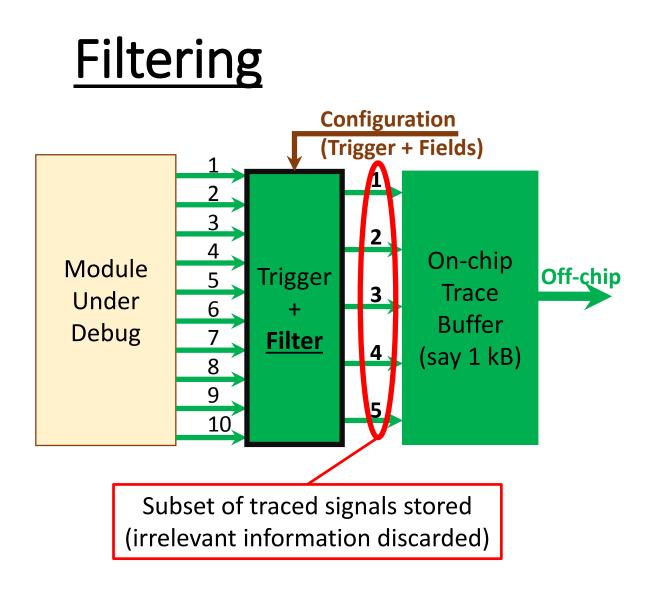

- <u>Sometimes</u>, a <u>subset</u> of signals is more important than others

- Depends on:

- Debug scenario

- Example: Signals within interconnect irrelevant when debugging pipeline

- Time of occurrence

- Just prior to the observed error All information is important

- Further in the past Sequence leading to the error is important

# **Observations**

### <u>Opportunity:</u>

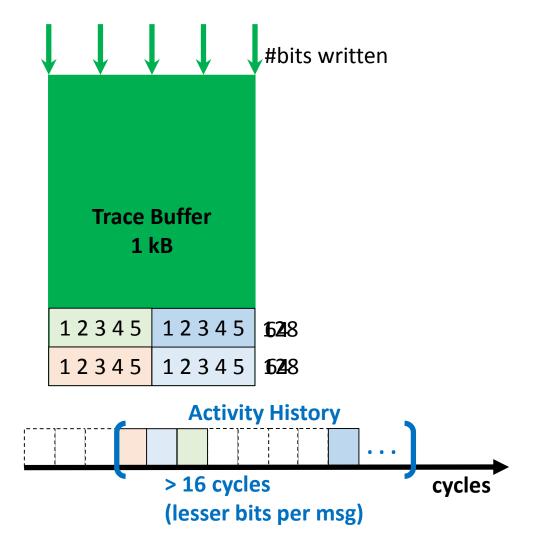

- Tapered Storage

- All signals for few cycles prior to observed erroneous behavior

- Only identifying information further into the past (rest discarded)

- Extend activity history using tapered storage

- Space saved by discarding irrelevant information

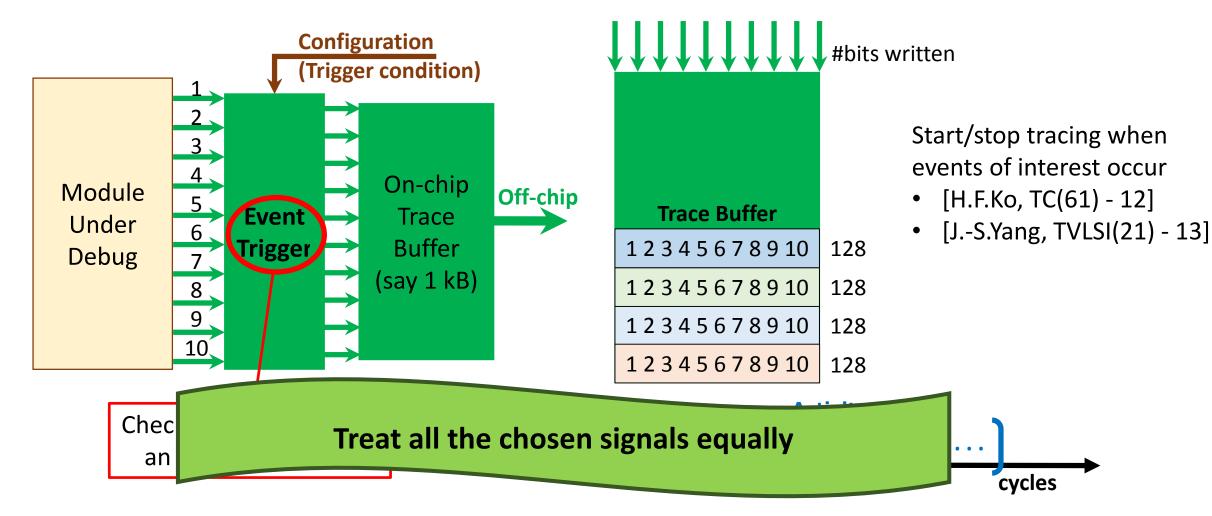

- <u>Challenges:</u>

- Select a subset of traced signals based on debug scenario

- Efficiently store detailed traces and summaries simultaneously

- Decide when to generate summaries of detailed traces

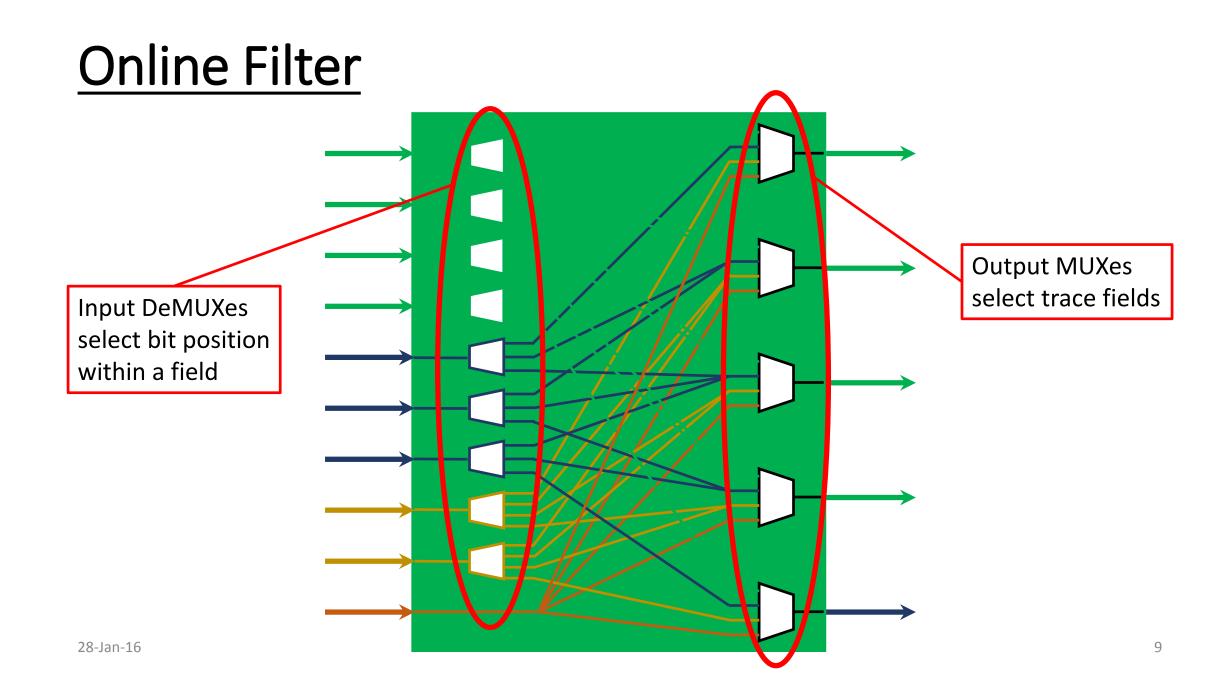

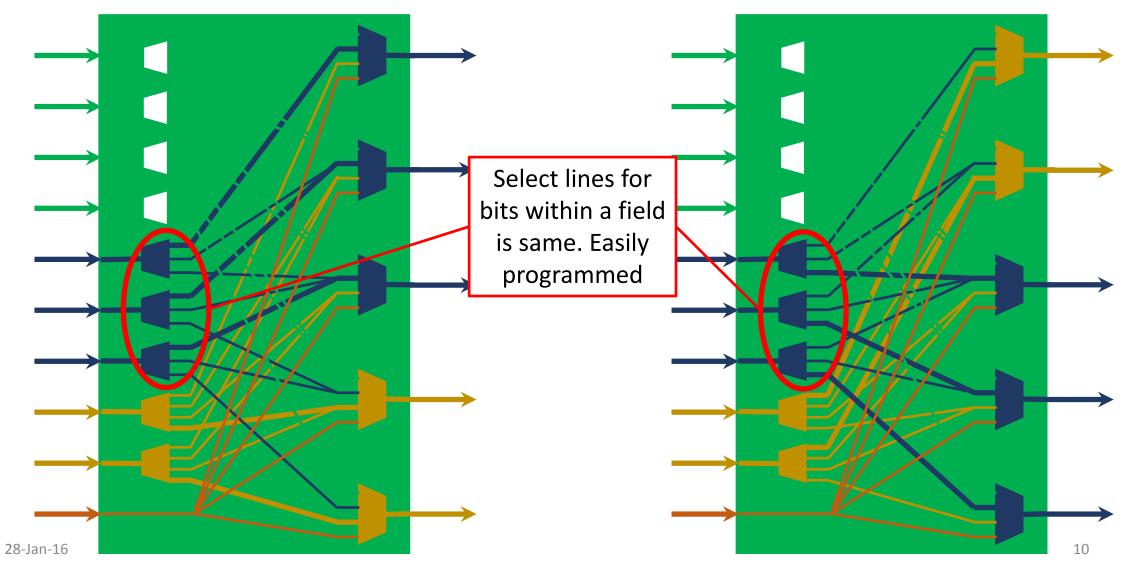

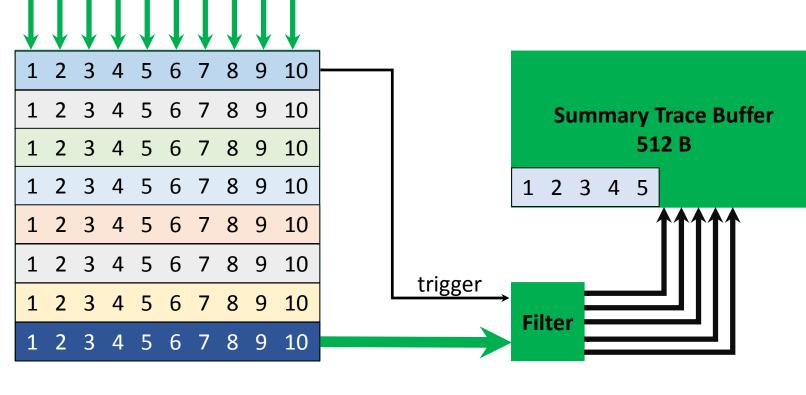

# **Online Filter**

# Storage Architecture (Split)

- Trace buffer sizes frozen at design time

- Fixed across debug scenarios

cycles

#### Storage Architecture (Unified) **Unified Trace Buffer** 1\_kB 1 2 3 4 5 3 4 5 6 7 8 9 10 2 3 4 5 6 7 8 9 1 2 10 trigger 3 5 6 7 8 9 4 10 Filter 5 6 7 8 9 10 3 4

- Flexible design

- Higher area overhead due to increase in the number of ports

- 2 write ports

- 1 read port

cycles

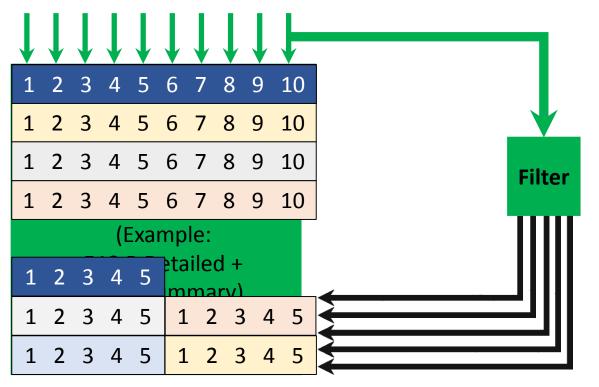

### **Storage Architecture (Overlapped)**

Flexible design

- Reduced number of ports

- 1 write port

- 1 r/w port

- Duplication of recent information

- Present in detailed and summary trace buffers

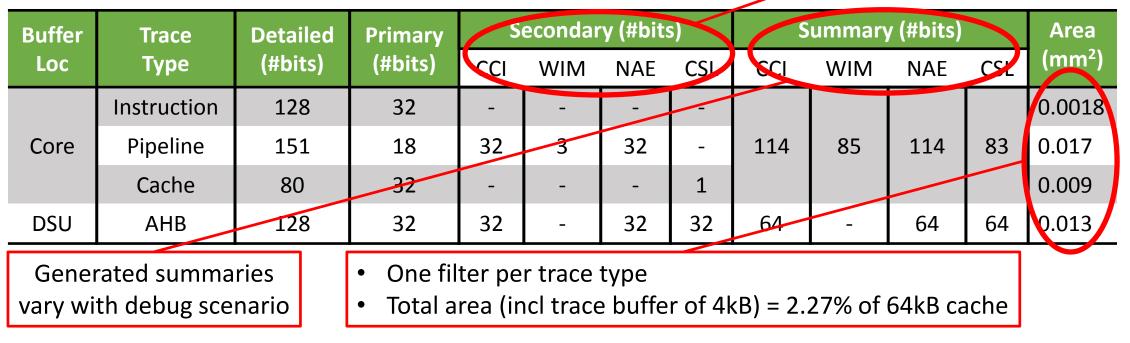

# <u>Results</u>

### <u>Setup</u>

- Commercial LEON3 SoC (available under GPL)

- Insert existing state-of-the-art debug proposals

- Scenarios inspired by product erratas, industry

- CCI Bug at the core-cache interface

- WIM Bug deep inside the pipeline

- NAE, CSL Bugs that lead to race condition

## <u>Results</u>

|                                                                                          | # Stalls           |                   |                   | History (cycles)                  |                   |                   |

|------------------------------------------------------------------------------------------|--------------------|-------------------|-------------------|-----------------------------------|-------------------|-------------------|

| Bug                                                                                      | Detailed<br>(4 kB) | Summary<br>(3 kB) | Summary<br>(2 kB) | Detailed<br>(4 kB)                | Summary<br>(3 kB) | Summary<br>(2 kB) |

| CCI                                                                                      | 138                | 51                | 77                | 1332                              | 3491              | 2374              |

| WIM                                                                                      | 94                 | 36                | 54                | 1109                              | 2085              | 1916              |

| NAE                                                                                      | 138                | 51                | 77                | 1332                              | 3491              | 2374              |

| CSL                                                                                      | 138                | 52                | 78                | 1332                              | 3534              | 2307              |

| <ul> <li>Number of stalls reduced by 63%</li> <li>Transfer times reduced from</li> </ul> |                    |                   |                   | • 162% increase in activity histo |                   |                   |

\* Uses a serial link operating at 115200 bps

100.72s to 29.7s \*

## **Conclusions**

- Proposed new debug methodology that uses combination of detailed trace messages and their summaries

- Extends trace history by upto <u>162%</u>

- Minimal additional area <u>2.27% of a 64kB cache (including 4kB trace buffer)</u>

- <u>No assumptions</u> about the type of error

- <u>Supports</u> at-speed <u>debugging of different classes of bugs</u> like non-repeatable errors, bugs that have long suspect windows

# Thank You!