Timing Window Wiper : A New Scheme for Reducing Refresh Power of DRAM ASP-DAC 2017

**Ho Hyun Shin**, Hyeokjun Seo, Byunghoon Lee, Jeongbin Kim and *Eui-Young Chung*

Yonsei University, Republic of Korea

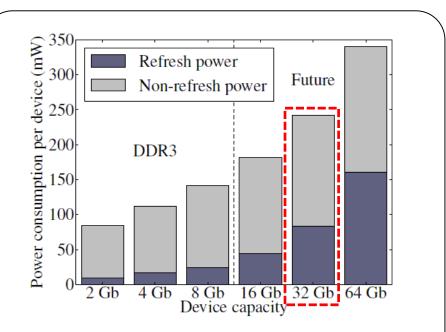

## **Power Breakdown for DRAMs**

| Table 1. Power consumption breakdown for an IBM p670. |            |        |                     |                                    |                          |                |

|-------------------------------------------------------|------------|--------|---------------------|------------------------------------|--------------------------|----------------|

| IBM p670<br>server                                    | Processors | Memory | I/O<br>and<br>other | Processor<br>and<br>memory<br>fans | I/O<br>component<br>fans | Total<br>watts |

| Small<br>configuration<br>(watts)                     | 384        | 318    | 90                  | 676                                | 144                      | 1,614          |

| Large<br>configuration<br>(watts)                     | 840        | 1,223  | 90                  | 676                                | 144                      | 2,972          |

## Memory power accounts for 40% of the

#### total system power.

\* C. Lefurgy, K. Rajamani, F. Rawson, W. Felter, M. Kistler, and T. Keller, "Energy management for commercial servers, "Computer, vol. 36, pp. 39-48, Dec. 2003.

#### Refresh power accounts for up to 35%

of total DRAM power in high capacity DRAMs

\* J. Liu, B. Jaiyen, R. Veras, and O. Mutlu, "RAIDR: Retention-aware intelligent DRAM refresh," in 2012 39th Annual International Symposium on Computer Architecture (ISCA), pp. 112, June 2012.

## **Previous Works**

### Row Selective

SRA, Smart Refresh, ESKIMO

#### \* Key idea

The DRAM controller has a tag table for all row addresses and prevents pre-activated or unnecessary row from refresh.

#### (+) Pros

1) Simple to implement

### (-) Cons

- 1) Large register size

- 2) Limited effect on refresh power reduction

### Retention Time Aware

RAIDR, VRA, Flikker, RAPID

#### \* Key idea

Adjust refresh period of each row based upon its retention characteristics with OS management.

#### (+) *Pros*

1) Effective to reduce the refresh power

(-) Cons

1) High design complexity

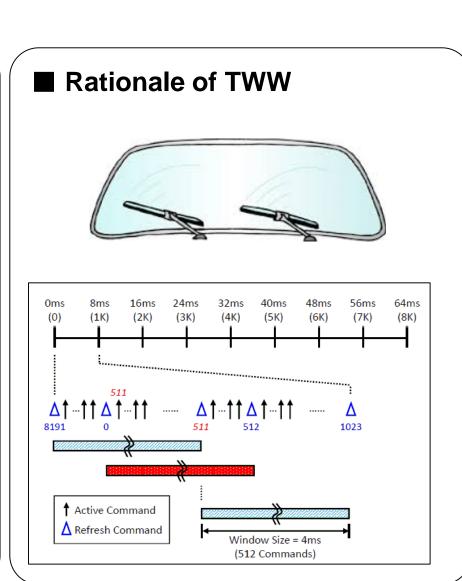

## **Proposed Scheme**

### Proposed Scheme

Timing Window Wiper(TWW)

#### \* Key idea

It captures the row and bank addresses of active commands within a timing window and eliminates the refresh operation of the captured rows within the pre-defined timing window.

### (+) Pros

- 1) Simple to implement

- 2) Appropriate level of register size

### (-) Cons

1) Limited effect on refresh power reduction

# **Timing Window Wiper(1)**

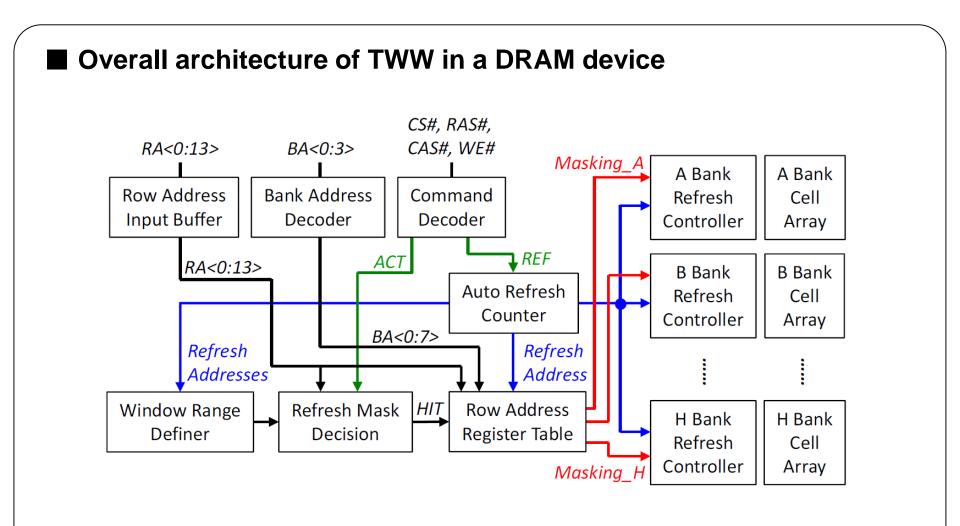

# **Timing Window Wiper(2)**

### TWW Management Algorithm

Algorithm 1 Pseudo code of TWW scheme

**INPUT** : CMD, BA, RA

// Issued command, bank address and row address

- 1: WS  $\leftarrow$  4096 // Window size (for 32 ms)

- 2: RC  $\leftarrow$  0 // Refresh address generated by the counter

- 3: EntryPt  $\leftarrow 0 //$  Entry pointer of the register table

- 4: while CMD do

- 5: if (CMD = "ACT") then

- 6: // When active command is issued

- 7: if  $(RA > RC \text{ and } RA \le RC + WS)$  then

- 8: // If the RA is belonging to the window range

- 9: EntryPt  $\leftarrow$  SearchRA(RA)

- 10: if (EntryPt.ValidBit = 1) then

- 11: UpdateBA(EntryPt, BA)

- 12: else

- 13:  $EntryPt \leftarrow LowestVacantEntry()$

- 14: StoreRA(EntryPt, BA)

- 15: UpdateBA(EntryPt, BA)

- 16: EntryPt.ValidBit = 1

- 17: end if

- 18: end if

- 19: else if CMD = "REF") then

- 20: // When refresh command is issued

- 21: EntryPt  $\leftarrow$  SearchRA(RA)

- 22: // Find the RA corresponding to the RC

- 23: if  $(EntryPt \neq NONE)$  then

- 24: MaskedBank  $\leftarrow$  GenerateMaskSignal(EntryPt)

- 25: ClearEntry(EntryPt) 26: RC++

- 27: end if

- 28: end if

- 29: end while

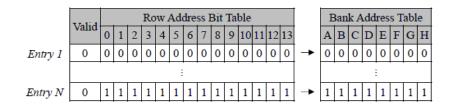

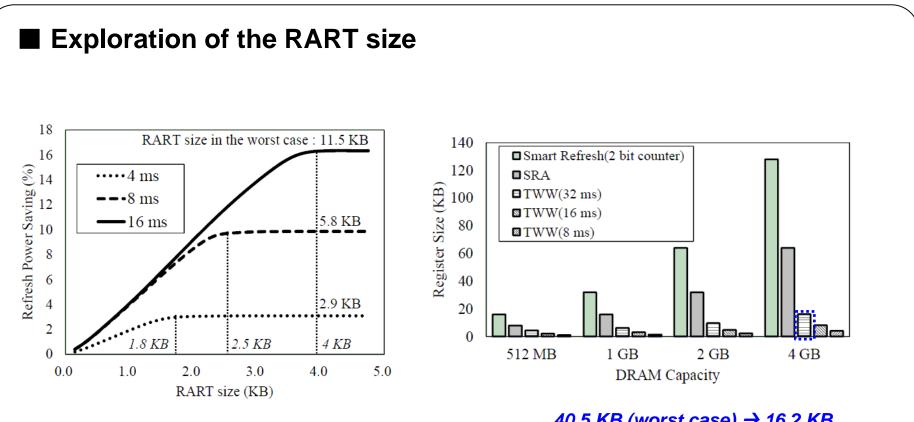

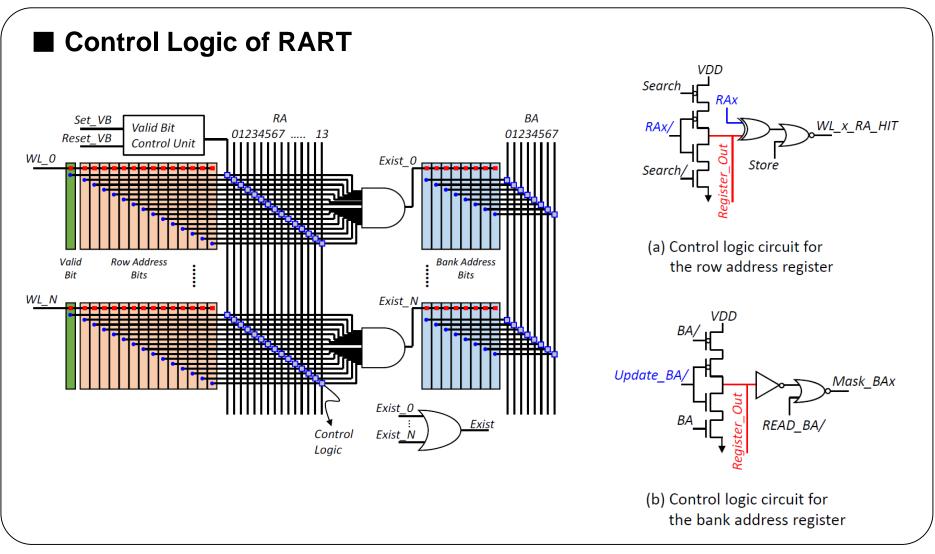

### Row Address Register Table (RART)

#### RART size = {1 + RA + (BA X REF)} X N

- RA : the number of row address bits

- BA : the number of banks

REF : the number of simultaneous refresh rows in a bank

N: the number of entries ( = refresh commands in a timing window)

Ex) Capacity = 4GB & Window Size = 32 ms

→ {1 + 16 + (8 X 8)} X 4096 = 40.5KB (Worst Case)

## **Timing Window Wiper(3)**

40% of the worst case size is enough

40.5 KB (worst case) → 16.2 KB

# **Timing Window Wiper(4)**

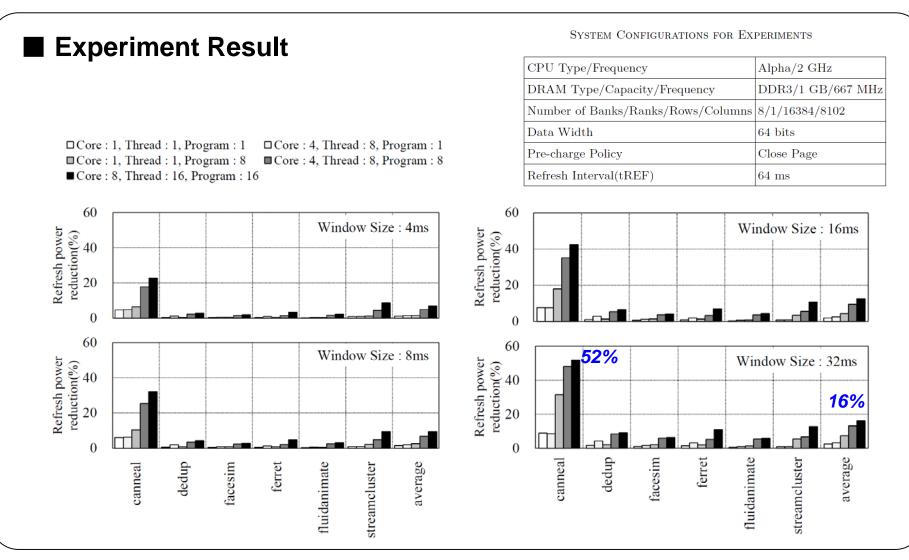

## **Experiment Result**

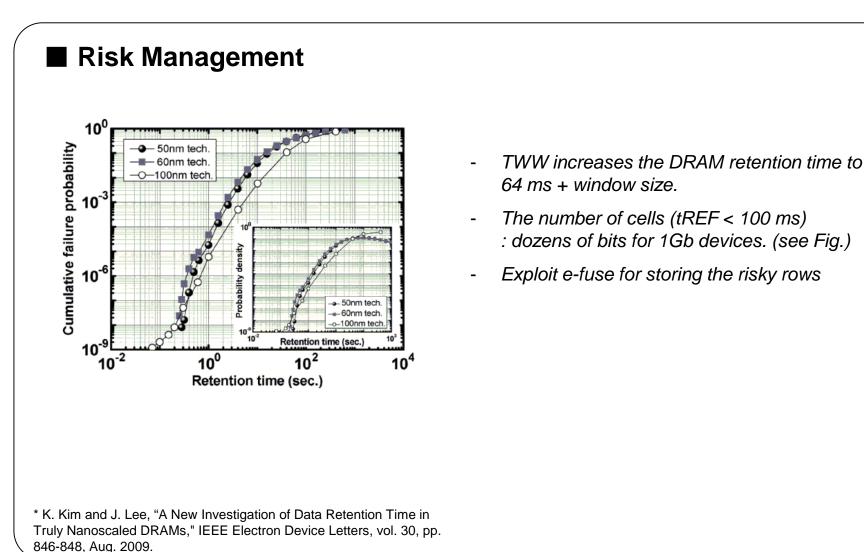

## **Risk Management**

10

## Conclusion

## Conclusion

#### [Performance]

TWW can reduce the average refresh power by up to 16%. (Register Size = 6.2KB)

#### [Compatibility]

TWW can be implemented without modifying the DRAM controller or the OS.