# BHNN: a Memory-Efficient Accelerator for Compressing Deep <u>N</u>eural <u>N</u>etwork with <u>B</u>locked <u>H</u>ashing Techniques

Jingyang Zhu<sup>1</sup>, Zhiliang Qian<sup>2\*</sup>, and Chi-Ying Tsui<sup>1</sup>

<sup>1</sup> The Hong Kong University of Science and Technology, Hong Kong <sup>2</sup> Shanghai Jiao Tong University, Shanghai, China

IEEE/ACM ASP-DAC 2017, 19th Jan., 2017, Chiba

#### Introduction

- Related work

- Blocked hash neural network: algorithm

- Blocked hash neural network: hardware architecture

- Experiment results

- Conclusion

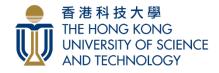

### The renaissance of neural network

- Big data & powerful machine (Moore's Law)

- The increasing scale of neural networks in ImageNet visual recognition challenge

Revolution of Depth in ILSVRC

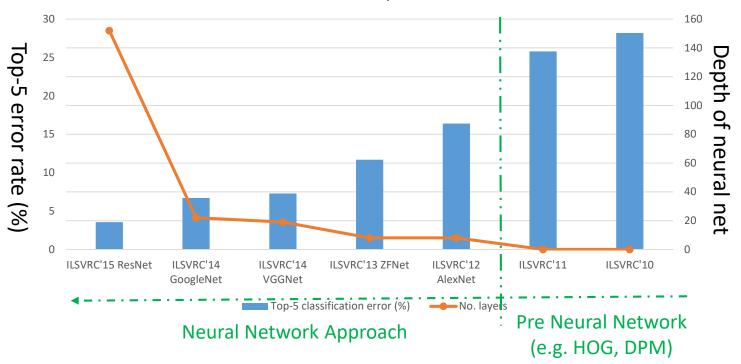

### Three elementary layers in neural network

- Convolutional layer (CONV): mostly computation-intensive

- Pooling layer (POOL)

- Fully-connected layer (FC): mostly memory-intensive

Take up 90% parameters (~120M parameters)

Introduction

#### • Related work

- Blocked hash neural network: algorithm

- Blocked hash neural network: hardware architecture

- Experiment results

- Conclusion

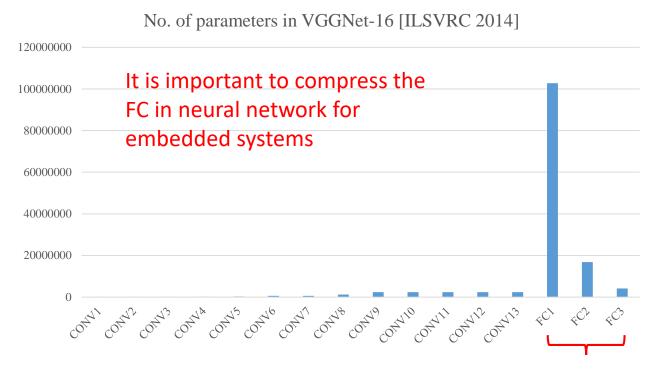

### Related work

- Hash Neural Network<sup>[1]</sup>: map real weights into virtual weights through hash function

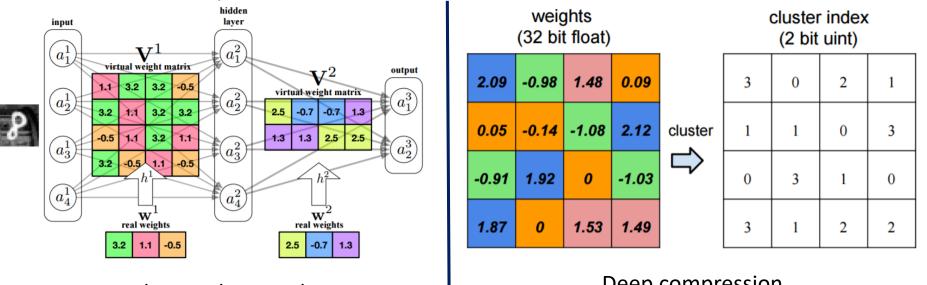

- Deep compression<sup>[2]</sup>: map real weights into virtual weights through cluster index (obtained from k-means)

#### Hash neural network

Deep compression

[1] Chen W, Wilson J T, Tyree S, et al. Compressing neural networks with the hashing trick[J]. [2] Han S, Mao H, Dally W J. Deep compression: Compressing deep neural network with pruning, trained quantization and huffman coding[J].

# Potential issues of hash neural network and deep compression

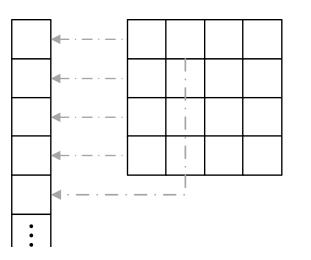

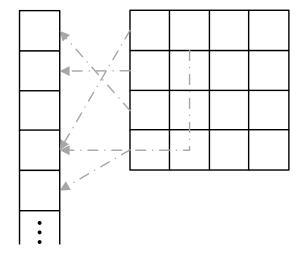

• No spatial locality in hashed neural network

Organize the weights in adjacent locations in memory

Scattering hash map destroys the spatial locality in memory access

• Deep compression: additional storage of cluster index

- Introduction

- Related work

#### • Blocked hash neural network: algorithm

- Blocked hash neural network: hardware architecture

- Experiment results

- Conclusion

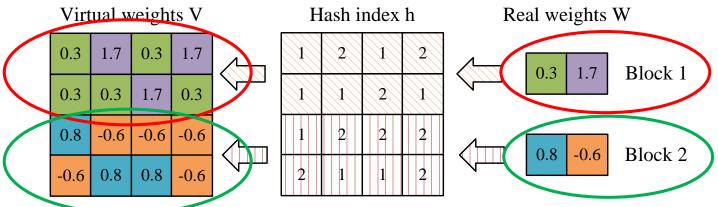

## Our approach: blocked hash neural network

• Basic idea: preserve the spatial locality in hash neural network through the blocked constraint

- Real weights in block 1 only serve for first 2 rows in virtual weights

- Real weights in block 2 only serve for last 2 rows in virtual weights

- No cluster index storage is required since the mapping is through a predetermined hash functions

- Real weight block size b determines the tradeoff of locality and performance degradation

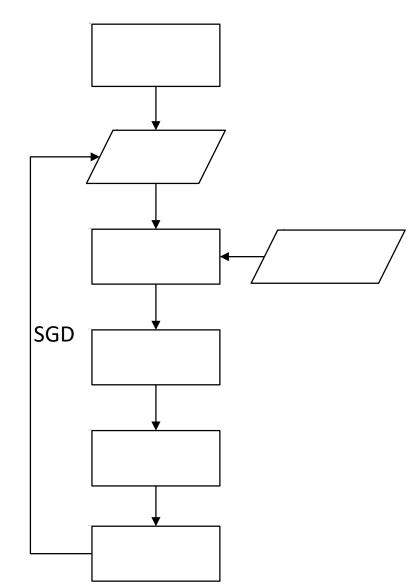

### Training of blocked hash neural network

• Backpropagation into the real weights, derived from chain rules

$\frac{\partial \mathcal{L}}{\partial W_k^{(l)}} = \sum_{i,j} \frac{\partial \mathcal{L}}{\partial V_{ij}^{(l)}} \frac{\partial V_{ij}^{(l)}}{\partial W_k^{(l)}} = \sum_{i,j} \delta_{ij}^{(l)} \mathbb{1}\{h(i,j,l) = k\}$

where  $\delta$  is the error term which can be obtained from backpropagation, and  $1\{\cdot\}$  is the indicator function

Training flow of blocked hash neural network

Hardware acceleration of blocked hash neural network: basic arithmetic operation

• The basic operation of feedforward pass is a matrix vector operation

for

$$i = 0$$

;  $i < n_{out}$ ;  $i = i + 1$  do

$\begin{vmatrix} \operatorname{act}_{out}[i] = 0; \\ \operatorname{for} j = 0; j < n_{in}; j = j + 1$  do

$\mid \operatorname{act}_{out}[i] + = V_{ij} \operatorname{act}_{in}[j]; \\ \operatorname{end} \\ \operatorname{act}_{out}[i] = g(\operatorname{act}_{out}[i]); \\ end \\ Algorithm 1: Pseudo code for the original FC layer. memory since we block the hash neural network$

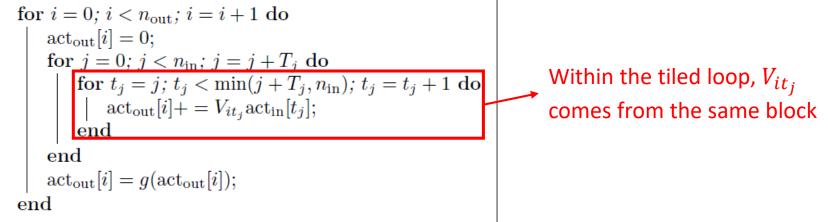

# Hardware acceleration of blocked hash neural network: loop tiling

- Two-level memory hierarchy

- On-chip SRAM: store all the real weights W (we can store weights on-chip since we compress the weights a lot)

- On-chip register file: store only the current active real weight block

Algorithm 2: Pseudo code for the tiled FC layer.

• Loop tiling size  $T_j = b/cr$ , where b is the real block size and cr is the desired compression rate

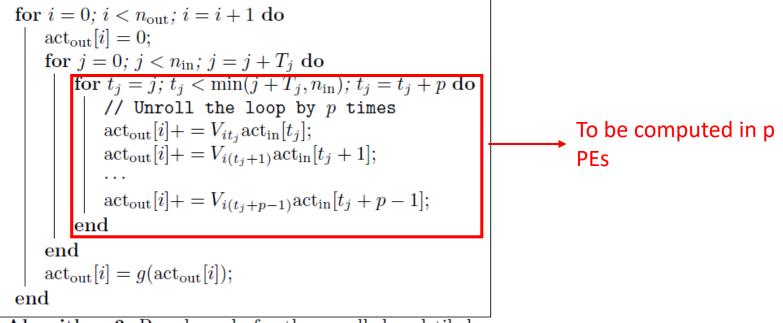

# Hardware acceleration of blocked hash neural network: loop unrolling

• Unroll the loop to parallelize the computation

Algorithm 3: Pseudo code for the unrolled and tiled FC layer.

- Introduction

- Related work

- Blocked hash neural network: algorithm

- Blocked hash neural network: hardware architecture

- Experiment results

- Conclusion

# Hardware architecture of blocked hash neural network

- 5 pipeline stages

- Refresh & Hash: fetch the real weights from on-chip SRAM to local register file & hash computation for index

- XBAR & RE In<sub>act</sub>: crossbar access the corresponding real weights & read the input activations

- Mult: compute the multiplication in parallel

- Merge: compute the accumulation

- ReLU & WB: nonlinear computation & write back to output activation

# Simplified hash function for hardware implementation

- A general hash function is complex: large area & multiple cycles

- A simplified hash function is tolerable due to our simulation results  $V_{ij}^{(l)} = W_{h(i,j,l)}^{(l)} \xi(i,j,l)$

- $h(i, j, l): N^3 \rightarrow \{1, 2, ..., b\}$  determines the mapping procedure. Uniformly distributes the index within range 1 to b:

$h(i,j,l) = (i \oplus j \oplus l)\%b$

•  $\xi(i, j, l): N^3 \rightarrow \{-1, +1\}$  removes the bias of hash inner-product. Randomly generates the  $\pm 1$ :

$\xi(i, j, l) = LFSR\%2$

Hardware block of hash generator

- Introduction

- Related work

- Blocked hash neural network: algorithm

- Blocked hash neural network: hardware architecture

#### • Experiment results

Conclusion

### Simulation setup

- Algorithm level verification on MATLAB

- Verify the performance degradation under different compression rates

- Offline train using stochastic gradient descent (SGD)

- Numerical gradient check to guarantee the backpropagation is correct

- Fixed point simulation of hardware architecture

- Hardware implementation by Verilog

- Synthesize, place and routing using Xilinx Vivado

- Prototype in Xilinx FPGA VC709

- Evaluate performance over 3 different datasets with variant neural network architecture only consisting of FC layers

- Caltech 101 silhouettes

- Handwritten MNIST

- Handwritten MNIST challenging variant ROT

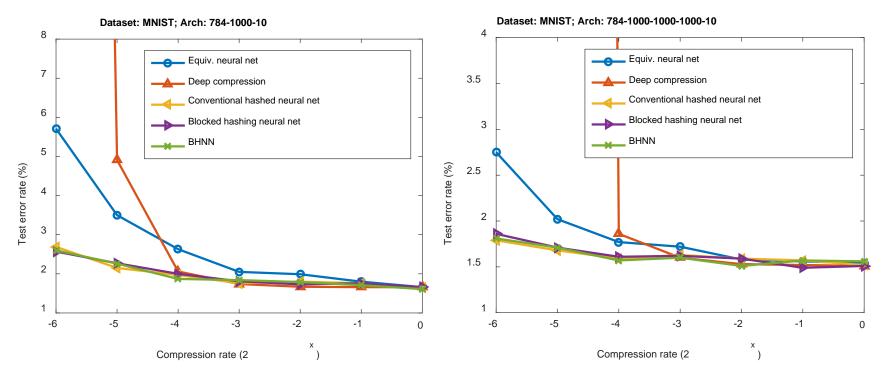

## Algorithm-level compression performance

- Five neural network compression schemes

- Equivalent neural net: plain neural network with equiv. size

- Deep compression

- Conventional hash network: with ideal hash function<sup>[\*]</sup>

- Blocked hash network: hash network with blocked constraints

- BHNN: hardware-mimic blocked hash neural network

# Algorithm-level compression performance (cont.)

- Dataset: MNIST

- Over 2 different neural network architectures

# Algorithm-level compression performance (cont.)

- Dataset: Caltech101

- Over 2 different neural network architectures

# Algorithm-level compression performance (cont.)

- Dataset: ROT

- Over 2 different neural network architectures

### Hardware implementation results

#### • Micro-architectural parameters on Xilinx VC709

| Micro-architectural parameters | Value          |  |

|--------------------------------|----------------|--|

| Parallelism p                  | 32             |  |

| Real block size b              | lock size b 64 |  |

| Quantization scheme            | Q0.15 (16-bit) |  |

| Compression ratio              | 1/16           |  |

| Clock freq                     | 100MHz         |  |

#### • Resource utilization

| Resource        | DSP  | BRAM  | LUT   | FF    |

|-----------------|------|-------|-------|-------|

| Used            | 32   | 939   | 17671 | 13271 |

| Utilization (%) | 0.89 | 63.88 | 4.08  | 1.53  |

### Hardware acceleration results

#### • Baseline: conventional hash (w/o spatial locality) on CPU & GPU

| Arch / Platform            | Intel i7 6700HQ | NVIDIA GTX 960M | Xilinx VC709   |

|----------------------------|-----------------|-----------------|----------------|

| 784-1000-10                | 5.54ms / image  | 1.17ms / image  | 0.25ms / image |

| 784-1000-1000-1000-<br>10  | 20.19ms / image | 2.98ms / image  | 0.89ms / image |

| 784-1000-101               | 6.31ms / image  | 1.25ms / image  | 0.28ms / image |

| 784-1000-1000-1000-<br>101 | 20.96ms / image | 3.05ms / image  | 0.92ms / image |

• FPGA has a speedup of over 20x and 3~5x over CPU and GPU under various neural network architectures

- Introduction

- Related work

- Blocked hash neural network: algorithm

- Blocked hash neural network: hardware architecture

- Experiment results

- Conclusion

### Conclusion

- A novel compression algorithm for neural network

- Spatial locality for the conventional hash neural network

- Maintain the same performance with the conventional hash neural network and outperform the "deep compression" scheme under heavy compression region

- A hardware accelerator catering for the blocked hash neural network

- Two-level memory hierarchy taking advantage of the spatial locality

- Hardware simplification of the general hash function

- Achieves ~20x and ~4x speedup compared with CPU and GPU