# Hardware Implementation of Super Minimum All Digital FM Demodulator

Nursani Rahmatullah

ASP-DAC 2006, Yokohama – Japan January 25, 2006

Department of Electrical Engineering

Bandung Institute of Technology

Indonesia

#### Introduction

- We propose improvement for new architecture of all-digital FM demodulator.

- This work enhances signal quality, system clock frequency, and superior than well known PLL technique today.

- No more multiplier, no more ROM or table, compact size, and very fast in transient or state response, SNR = 30.6 dB

- Real implementation in Altera® APEX20K200 EBC652-1X PLD gives 348 logic elements and run up to 224.42 MHz.

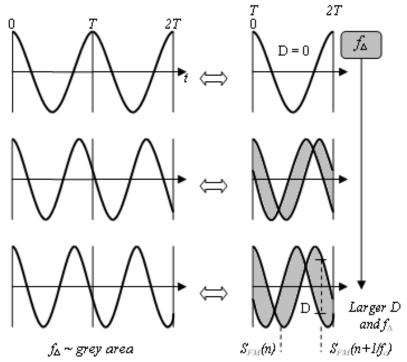

### New FM demodulation algorithm

The new algorithm assumes that process in FM demodulation is equivalent with tracking for frequency deviation. Tracking process is performed for each period of cycle

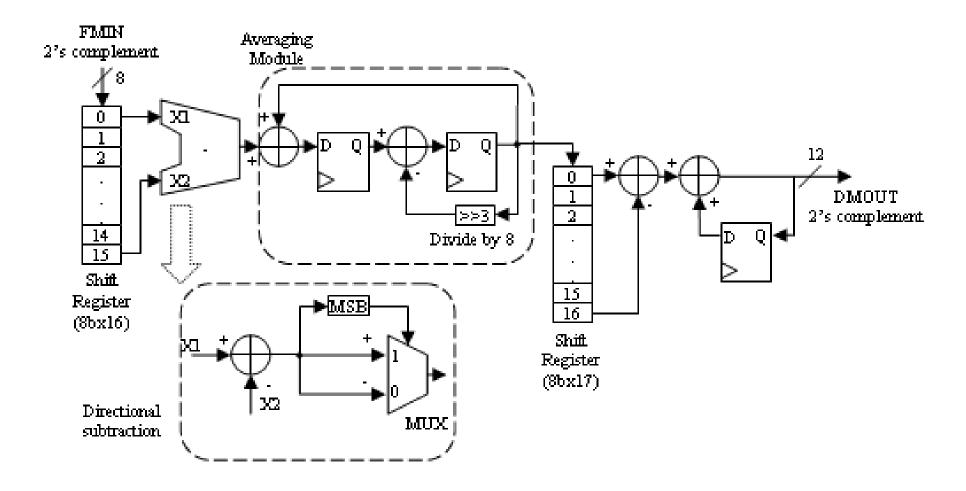

## Proposed Architecture

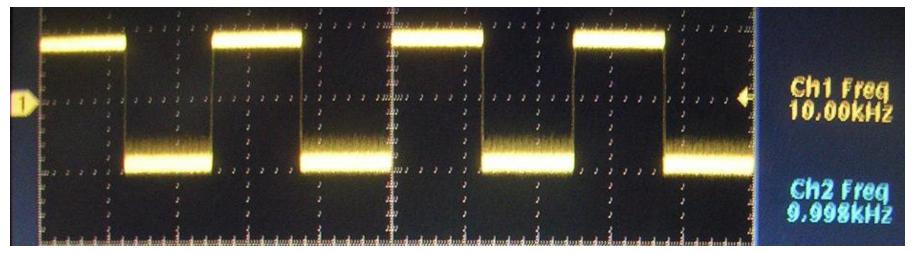

### Implementation Result

Basic architecture

Proposed architecture