# Configurable Multi-Processor Architecture and its Processor Element Design

Tsutomu Nishimura, Takuji Miki, Hiroaki Sugiura, Yuki Matsumoto, Masatsugu Kobayashi, Toshiyuki Kato, Tsutomu Eda, Hironori Yamauchi Ritsumeikan University, Japan

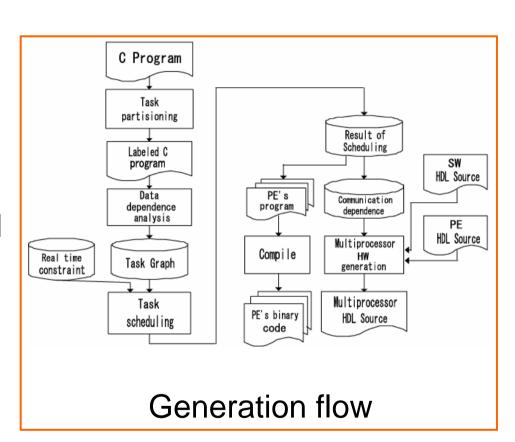

#### Multi-processor generation system

#### Goal

- To solve problem of multi-processor

- To eliminate mismatch between hardware and software

- Source

- C program

- Objectives

- HDL of multi-processor

- Software of each PE

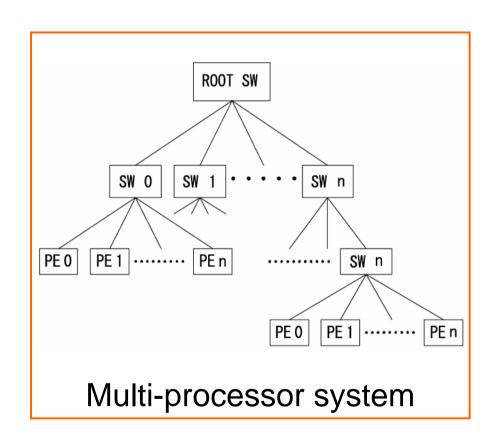

### Multi-processor architecture

#### Feature

- Distributed memory type multi-processor

- Hierarchical tree structure

- Composed as matrix switch

- Advantage

- High scalability

- Flexibility

### Performance of multi-processor

|          | Single<br>(clocks) | Multi<br>(clocks) | Ratio<br>(multi/single) |

|----------|--------------------|-------------------|-------------------------|

| 1024-FFT | 2,283,931          | 490,950           | 4.65 times              |

| DFT      | 1,931,629          | 138,648           | 13.93 times             |

- Simulation by software simulator

- Simulator is made by C++

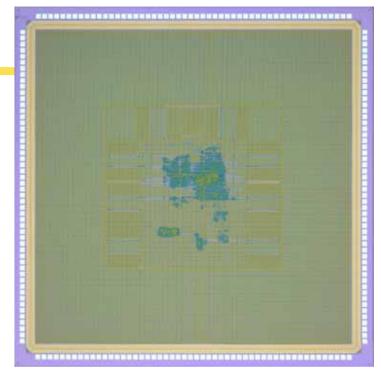

## LSI implementation

- LSI prototype

- Processor element

- Switch

- To achieve multiprocessor

- This chip can operate at 33 MHz

- •0.18um CMOS

- •208 pins

- •Die size: 6,166 × 6,166um

- •37,528 gates

- •Memory: IMEM 512words DMEM 4Kwords (1word = 32bit)