Single-Chip Multi-Processor Integrating Quadruple 8-way VLIW Processors with interface timing analysis considering power supply noise

> S Imai, A Inoue, M Matsumura, K Kawasaki, A Suga

> > Fujitsu Laboratories Ltd.

#### Outline

- Motivation

- Architecture

- Physical design

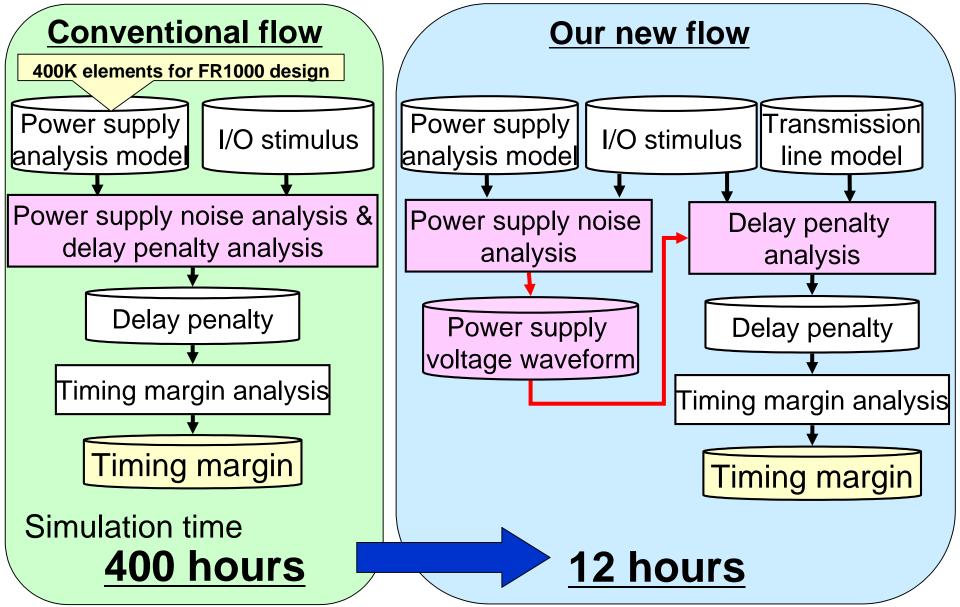

- Design flow considering power supply noise

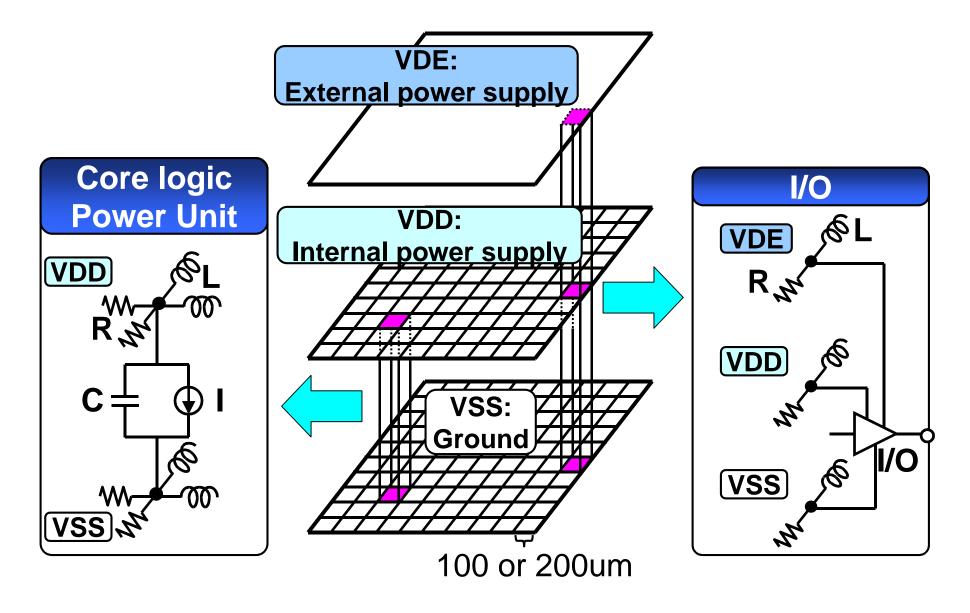

- LSI model for power integrity analysis

- Interface analysis example

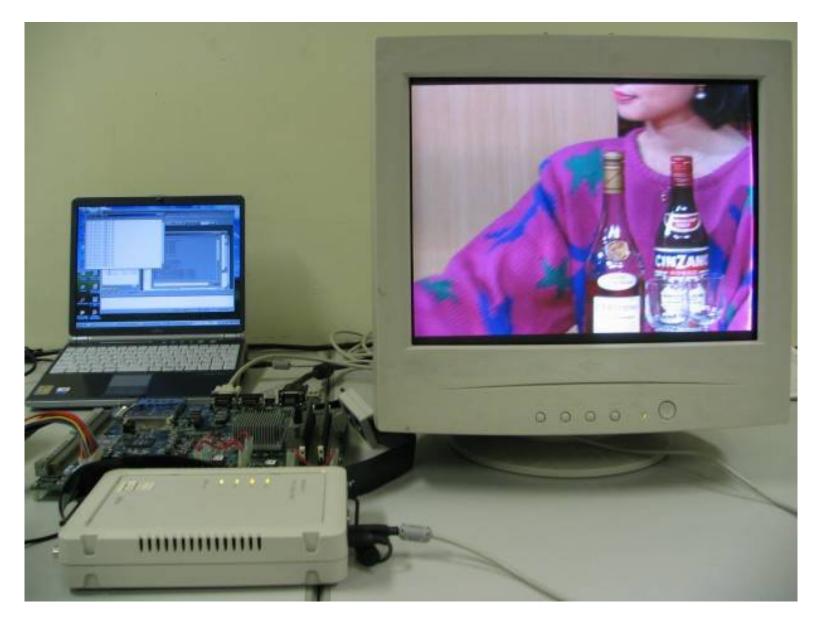

- MPEG2 MP@HL decoding on evaluation board

Summary

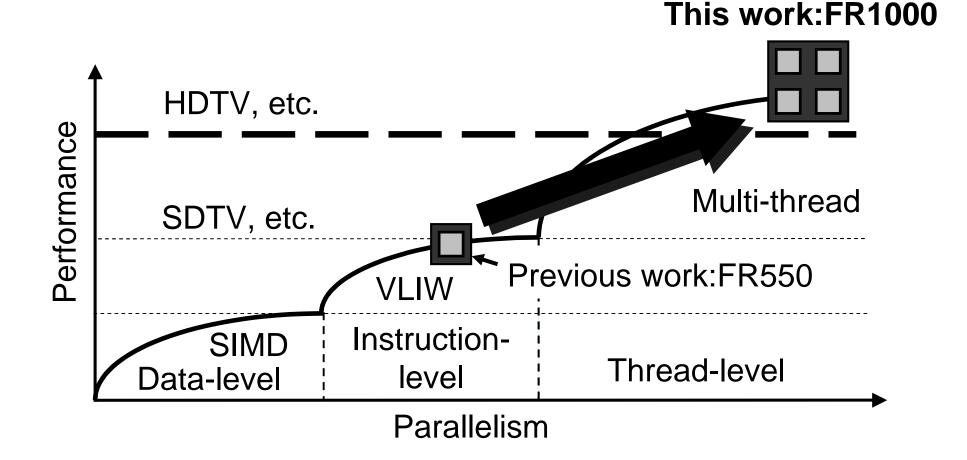

## Motivation: high performance and low power

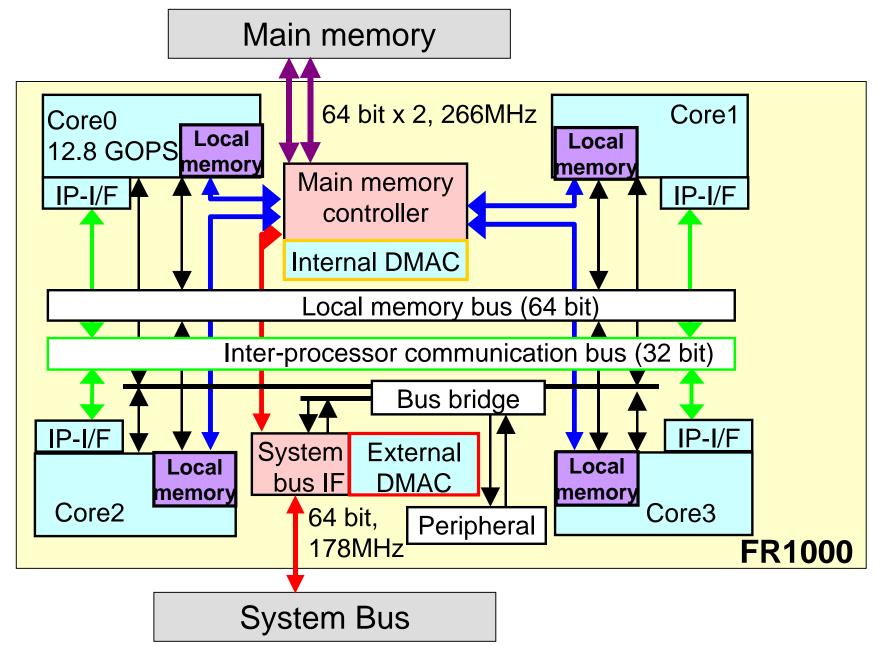

#### FR1000 block diagram

#### FR1000 chip specifications

| Core                | 4 cores with 8-way VLIW architecture |                          |

|---------------------|--------------------------------------|--------------------------|

| Memory              | 32 KB+32 KB/core (D-cache, I-cache)  |                          |

|                     | 128 KB/core (Local memory)           |                          |

| DMA controller      | 16 ch (Internal), 16 ch (External)   |                          |

| Interface           | Main memory 266 MHz 64 bit x 2 ch    |                          |

|                     | System Bus 178 MHz 64 bit            |                          |

| Technology          | 90-nm CMOS, 9-metal layers           |                          |

| Transistor count    | 28M (Logic), 55M (Memory)            |                          |

| Operating frequency | 533 MHz @1.2 V                       |                          |

| Power consumption   | <b>3.0 W</b> @1.2 V, 533 MHz         |                          |

| Package             | 900-pin FCBGA                        |                          |

| size                | 11.9 mm x 10.3mm                     | $\overline{\mathcal{D}}$ |

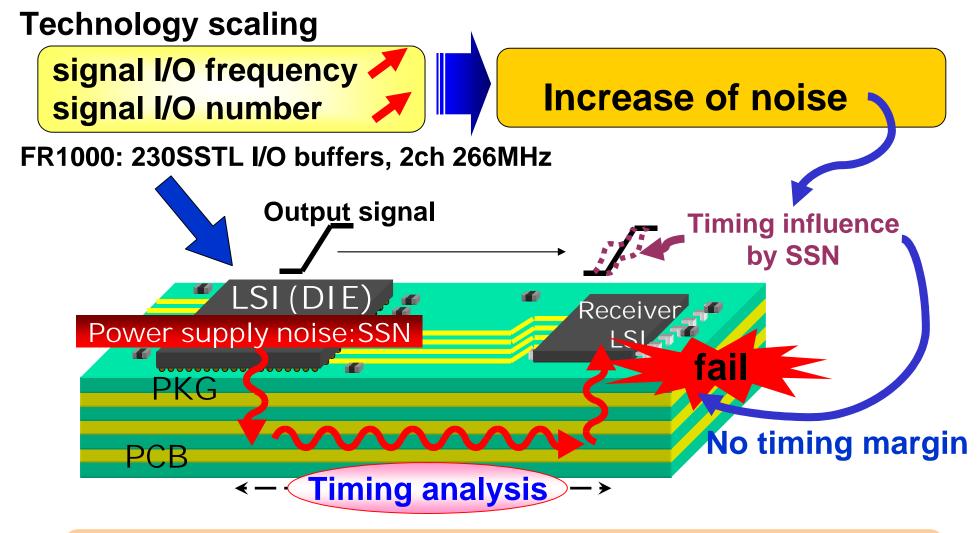

High speed interface cause power supply noise issue

#### Power integrity issue on system board

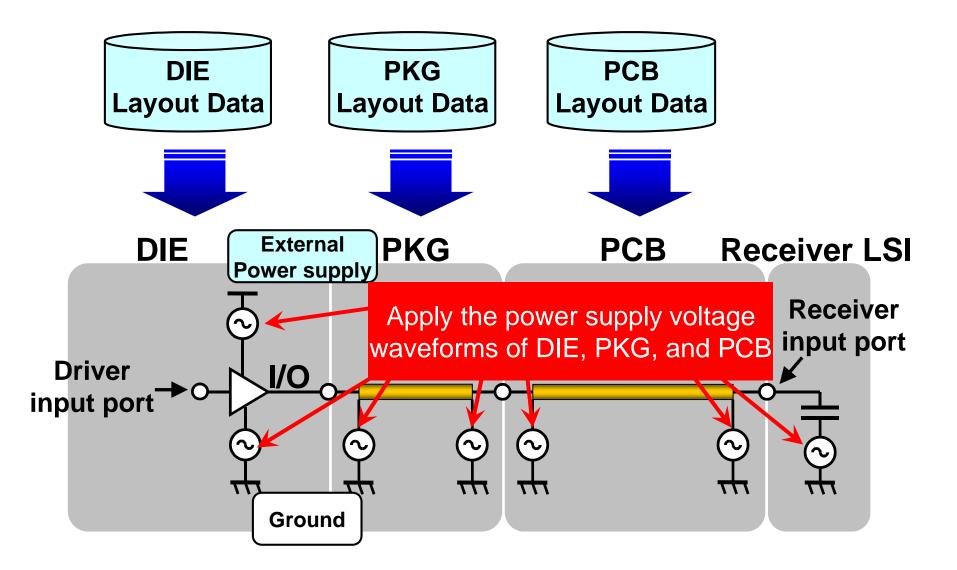

Timing margin analysis considering power supply noise of DIE, PKG and PCB is required

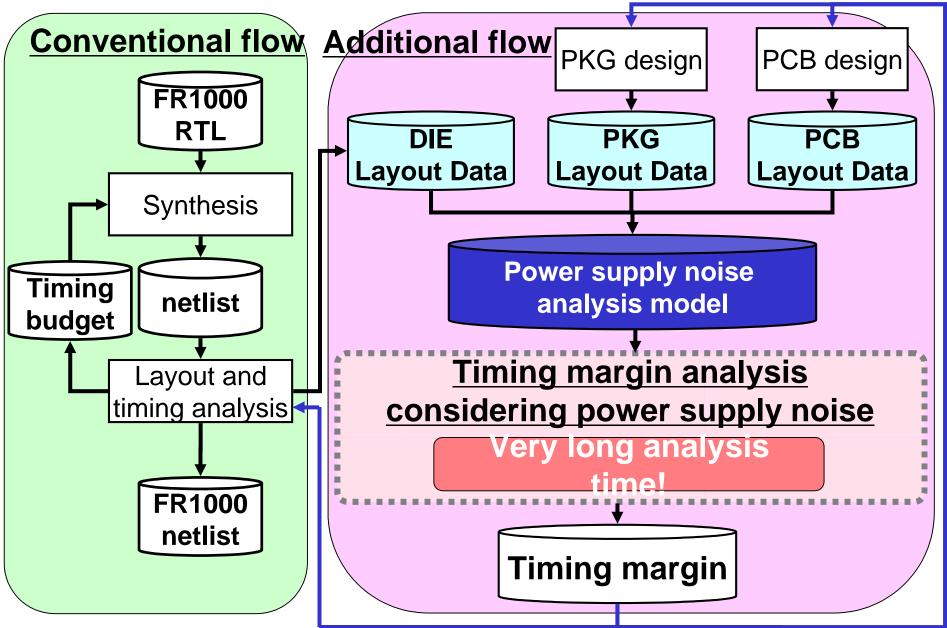

#### Design flow considering power supply noise

LSI power analysis model

#### Our timing margin analysis flow

#### **Transmission line model**

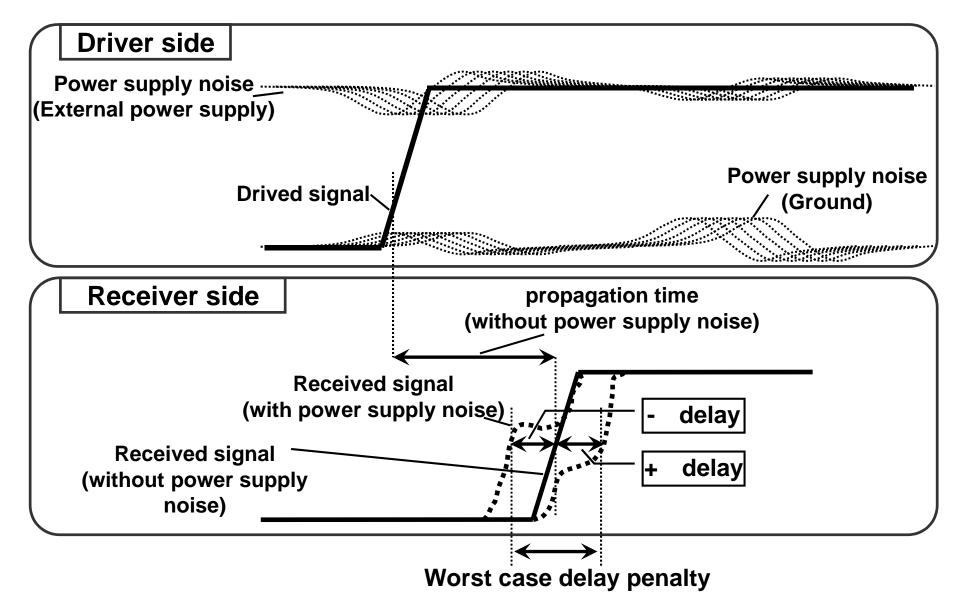

## Delay penalty by power supply noise analysis method

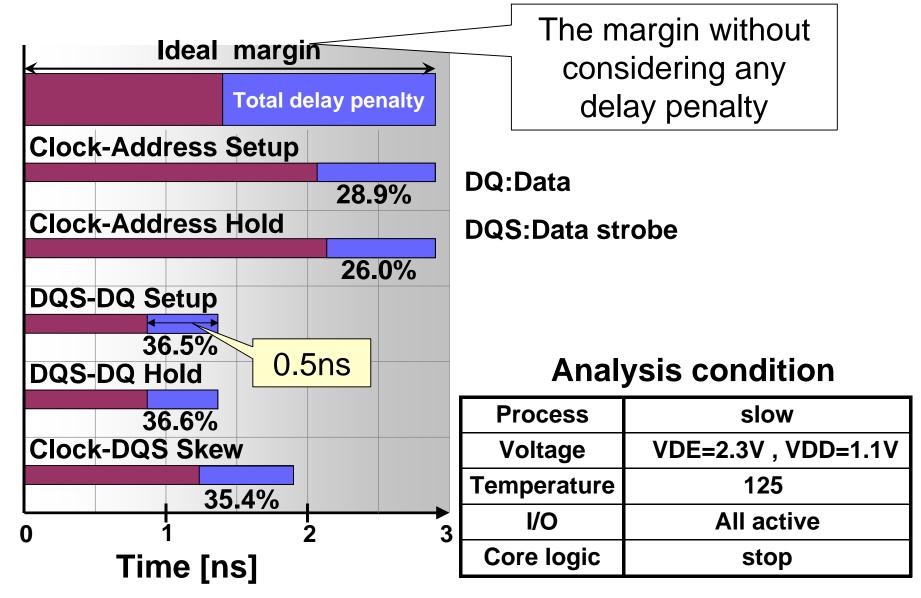

#### Analysis result of main memory interface

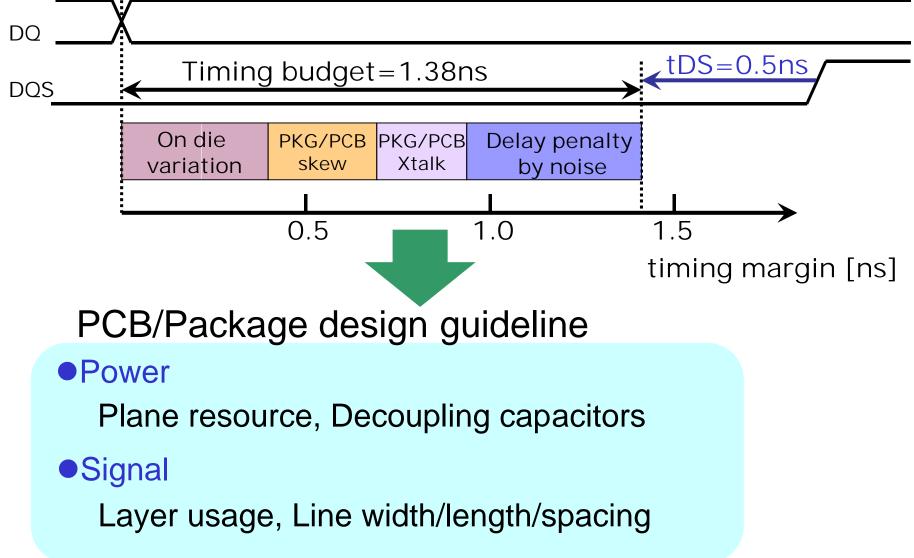

### PCB/Package design guideline

#### **DQ-DQS** interface timing analysis result

#### MPEG2 MP@HL decode for HDTV on FR1000

#### Summary

#### The low power

### single-chip multi-processor FR1000

-4 processor cores, internal DMAC, external DMAC -MPEG2 MP@HL without any dedicated circuits -3.0W@1.2V, 533MHz

# Introducing interface timing analysis considering power supply noise

-DIE(LSI) noise model development

-Timing analysis method at shorter times

#### THE POSSIBILITIES ARE INFINITE