# PowerViP: SoC Power Estimation Framework at Transaction Level

Jan. 26, 2006

Ikhwan Lee et. al.

Corporate Computer-Aided Engineering

Semiconductor Business

Samsung Electronics Co., Ltd.

- Introduction

- Component Power Modeling

- ARM926EJS processor

- AMBA AXI bus fabrics

- Custom IP blocks

- PowerViP

- Concluding Remarks

- Introduction

- Component Power Modeling

- ARM926EJS processor

- AMBA AXI bus fabrics

- Custom IP blocks

- PowerViP

- Concluding Remarks

## Low Power Design Solutions

System/ Circuit/ Software Logic Device Architecture Physical HW / SW **Power** Path Multi-Vth **Dual Gate Partitioning Balancing Management Dynamic Memory Gate Sizing VTCMOS** FinFET / 3D Volt. Scaling **Optimization** Instruction-**Adaptive** Voltage **Clock Gating** SOI Volt. Scaling level Opt. Island **Control-Data Technology Parallelism Power gating Multi-Tox** Transform. **Mapping** "You can't manage it until you can estimate it!" Power **Power** Power Power Power **Estimation Estimation Estimation Estimation Estimation**

## Why System Level Power Estimation?

- Advantages

- Larger opportunities for power reduction

- x10~x20 as compared to logic level

- Faster estimation

- Enables thorough design space exploration

- Power profile given in the system context

- Prevents from falling into a local optimum

## The Requirements and Problems

- Requirements

- System level simulation platform

- ViP (Virtual Platform)

- Power models of system components

- Problems

- Diversity of components (power characteristics)

- Trade-off among the below three factors

- Simulation speed → to maximize

- Estimation accuracy → to maximize

- Modeling effort → to minimize

## Observation in a mobile SoC family

Continuously evolving IPs

• Video IP (MPEG4, H.264)

Frequently reused IPs

- Processor: ARM, StarCore

- Bus: AXI, AHB

- Off-chip memory: DDR, Flash

- Memory controller

- Peripheral: GPIO, USB

- Image filters

Platform-based design enables maximum reusability

3<sup>rd</sup> party IPs

• 3D graphics

Model once, reuse many times

#### **Our Contributions**

- Identification of IP classes

- Power models for major SoC components

- Speed

- Accuracy

- Modeling effort

- Provide cycle-accurate power profile in the system context

- Introduction

- Component Power Modeling

- ARM926EJS processor

- AMBA AXI bus fabrics

- Custom IP blocks

- PowerViP

- Concluding Remarks

- Introduction

- Component Power Modeling

- ARM926EJS processor

- AMBA AXI bus fabrics

- Custom IP blocks

- PowerViP

- Concluding Remarks

#### ARM926EJS Power Profile

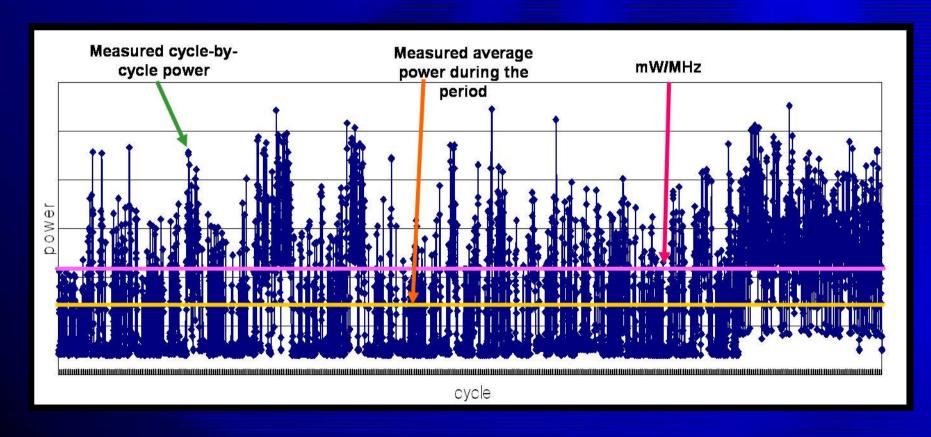

■ Simple mW/MHz model does not reflect power phase transitions during the course of a program execution

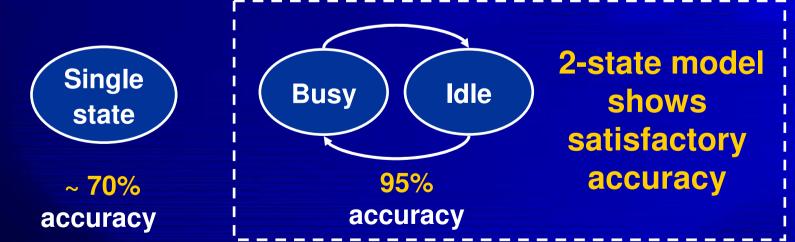

## Defining Power States (1)

- Separate core and cache power states

- Cache size needs to be configurable

- Cache power shows large variation (3~60% of total power)

- Core power states

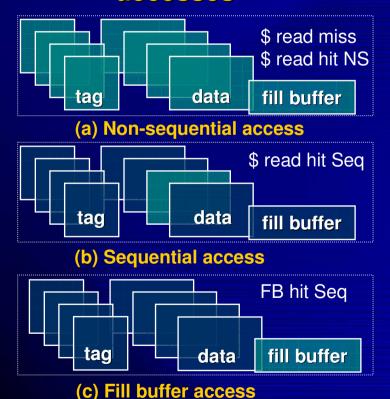

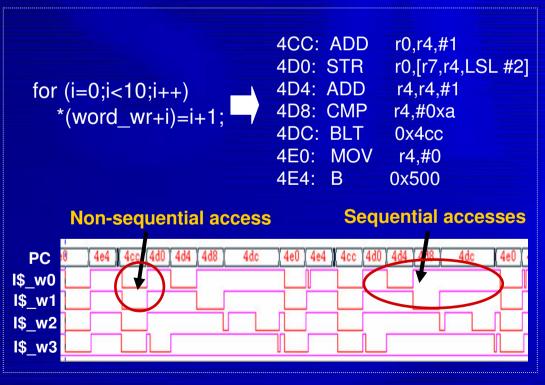

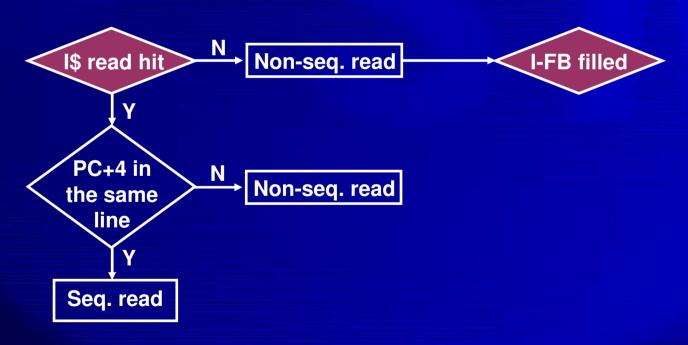

# Defining Power States (2)

- Cache power states

- Activity based coarse-grained power model

- Differentiates non-sequential, sequential, and fill buffer accesses

#### **Power Annotation**

- Core states are visible in the ARM926EJS ISS (instruction set simulator)

- Cache states need to be inferred from transaction level activities

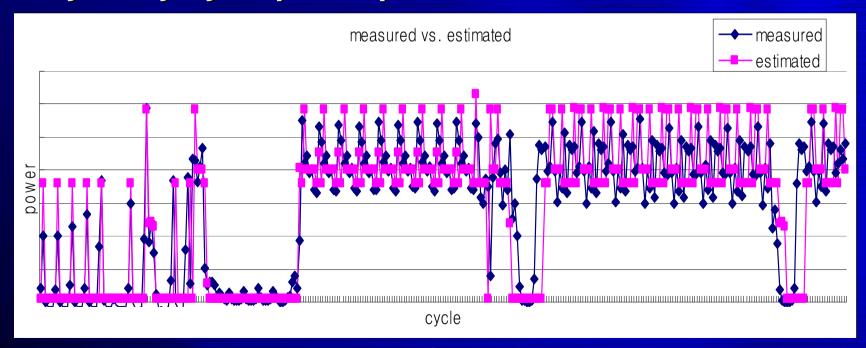

## Estimation Accuracy vs. Gate-level

■ Average estimation accuracy (< 93%)

| dhrystone | cav_detect | adpcm | FFT   | h264 enc |

|-----------|------------|-------|-------|----------|

| 97.1%     | 97.3%      | 98.2% | 96.6% | 93.1%    |

Cycle-by-cycle power profile

- Introduction

- Component Power Modeling

- ARM926EJS processor

- AMBA AXI bus fabrics

- Custom IP blocks

- PowerViP

- Concluding Remarks

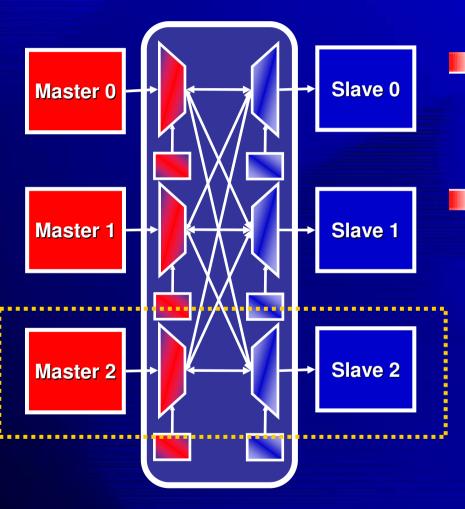

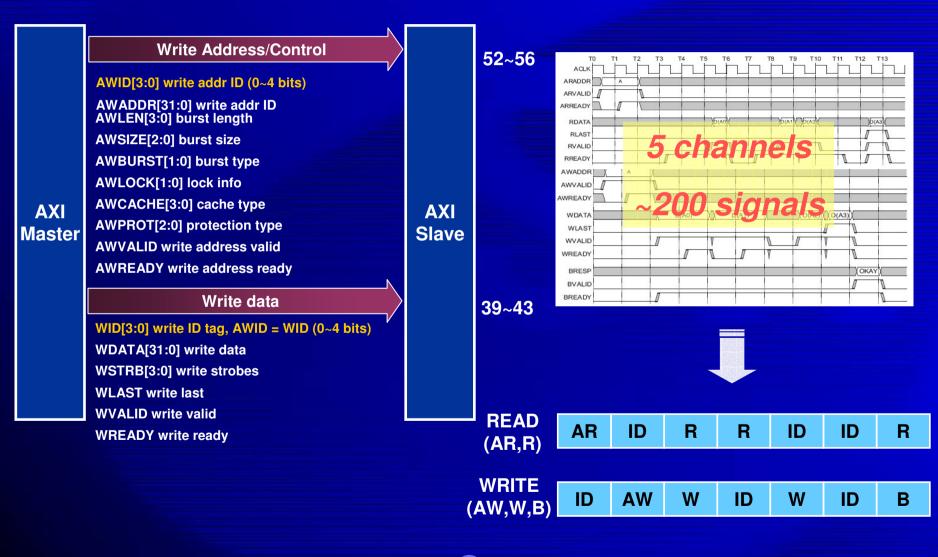

#### PL300 AXI Interconnect

**■** Full crossbar architecture

■ Power characterization when only one master and one slave are active

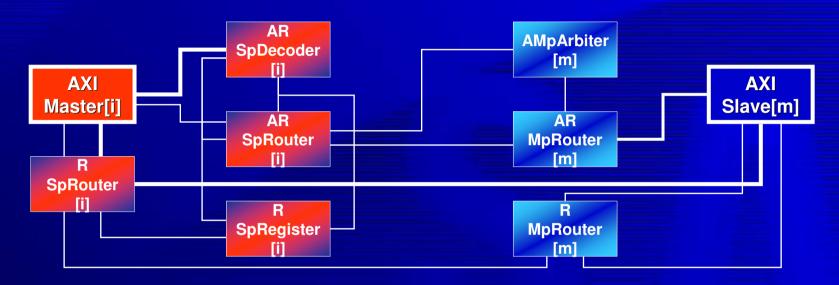

## Component-based Power Model: PL300

- Characterize each component

- For each basic state, find out which component is active and how much power it consumes

- Compose the basic model

- For each cycle, add the power consumption of all active components

- Linear regression model

- Consider the coupling effect

## Linear Regression Model

Each AXI sub-component has its own linear regression model.

$$E_{total} = E_{est} + n_{-}AR * E_{br\_RD} + n_{-}AW * E_{br\_WT} + \frac{n_{-}RD * E_{cyc\_RD} + n_{-}WT * E_{cyc\_WT}}{n_{-}RD + n_{-}WT}$$

$$E_{est} = a_1 E_{comp} + a_0$$

$$a_1 = \frac{n\_RD * a_1\__{RD} + n\_WT * a_1\__{WT}}{n\_RD + n\_WT}$$

$$a_0 = \frac{n\_RD * a_0\__{RD} + n\_WT * a_0\__{WT}}{n\_RD + n\_WT}$$

**Coupling** effects

## Perspective of our bus power TLM

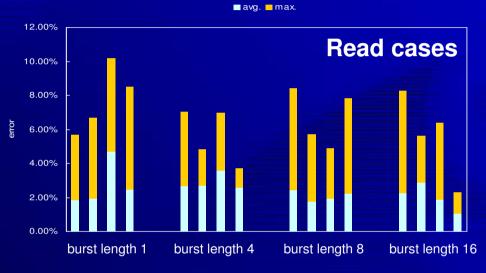

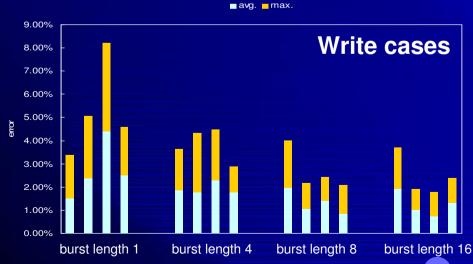

# Estimation Accuracy vs. Gate-level

|  |         | # master | # slave | ID width | data<br>width |

|--|---------|----------|---------|----------|---------------|

|  | conf. 1 | 4        | 4       | 0        | 32            |

|  | conf. 2 | 4        | 4       | 4        | 32            |

|  | conf. 3 | 6        | 2       | 4        | 32            |

|  | conf. 4 | 7        | 3       | 5        | 64            |

Max < ~10% estimation error

- Introduction

- Component Power Modeling

- ARM926EJS processor

- AMBA AXI bus fabrics

- Custom IP blocks

- PowerViP

- Concluding Remarks

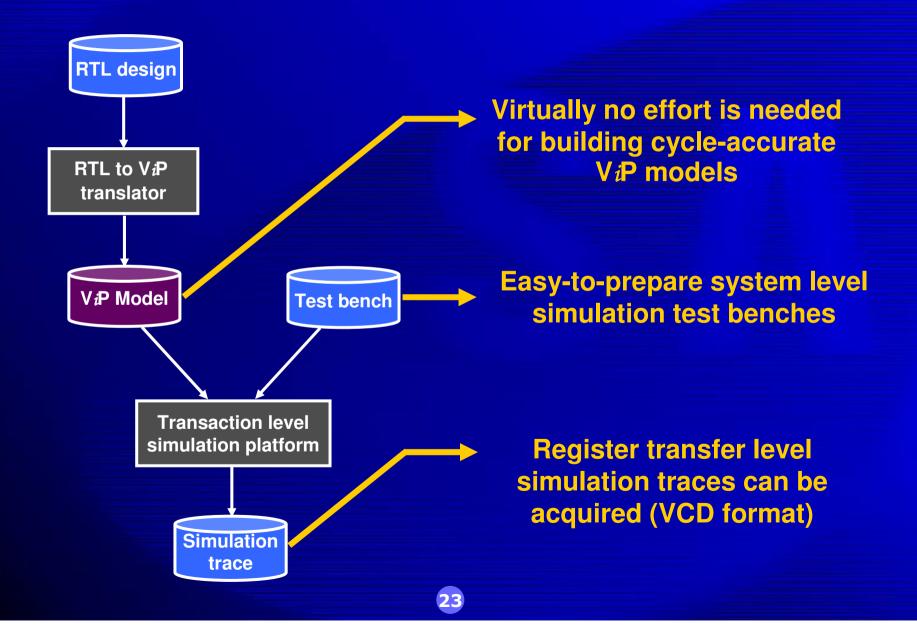

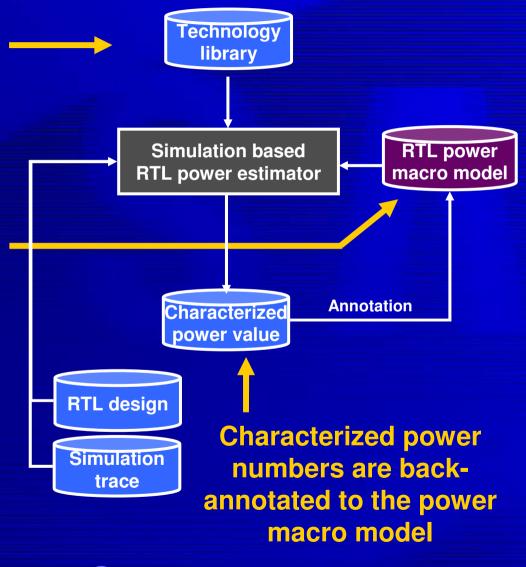

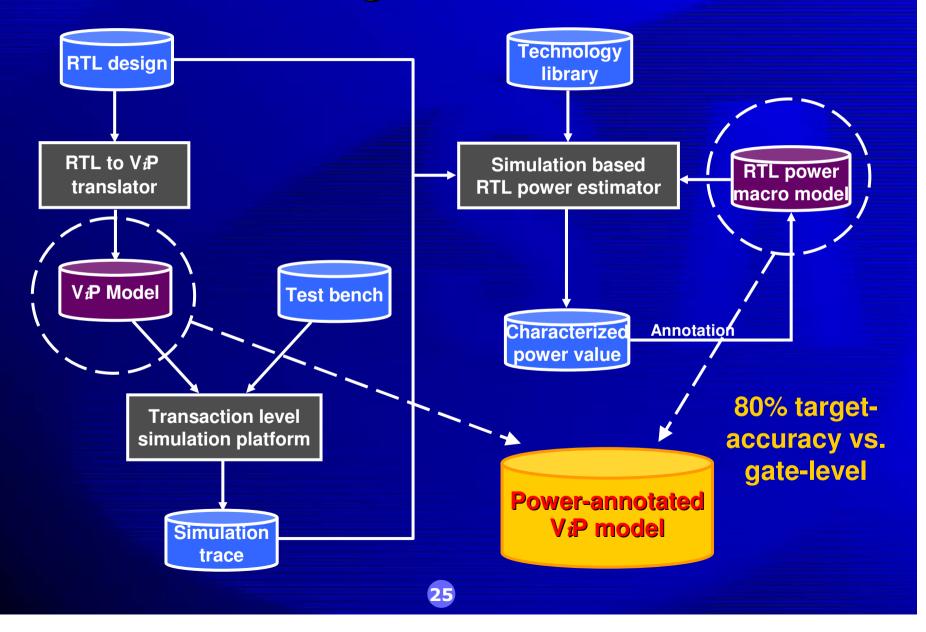

#### ViP Model Generation and Simulation

#### RTL Power Estimation & Characterization

Process-specific libraries (130G, 90LP, etc.)

Power-representative FSM must be manually extracted from the RTL design

# Power Modeling of Custom IP Blocks

- Introduction

- Component Power Modeling

- ARM926EJS processor

- AMBA AXI bus fabrics

- Custom IP blocks

- PowerViP

- Concluding Remarks

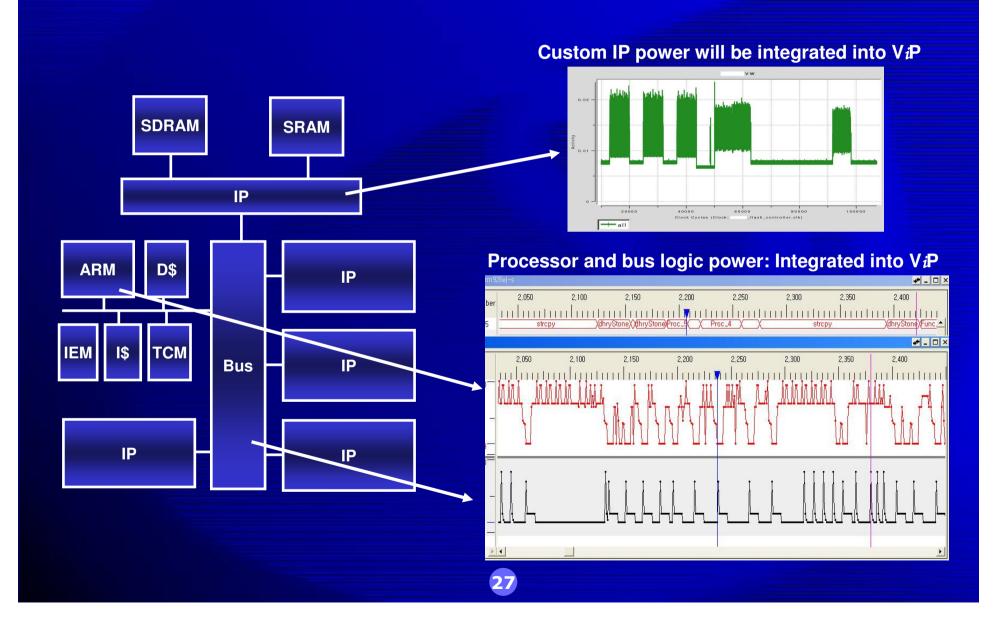

### **Integration of Component Power Models**

## Application of PowerViP

- Peak power analysis

- We can find realistic test patterns to avoid "over-design" of power grid

- Low power bus architecture exploration

- Early development of power management software

- Software code optimization for low power

- Introduction

- Component Power Modeling

- ARM926EJS processor

- AMBA AXI bus fabrics

- Custom IP blocks

- PowerViP

- Concluding Remarks

## Concluding Remarks

- Development of component power models

- 93% accuracy for ARM926EJS

- 95% accuracy for AXI bus

- 80% target-accuracy for custom IP blocks

- Integration into single simulation platform

- Cycle-accurate power profile of each component is shown

- PowerViP can be used in variety of application