#### Mathematically Assisted Adaptive Body Bias (ABB) for Temperature Compensation in Gigascale LSI Systems

January 2006

#### Sanjay Kumar, Chris Kim, and Sachin Sapatnekar

Department of Electrical and Computer Engineering University of Minnesota

# Outline

Motivation

Problem Statement

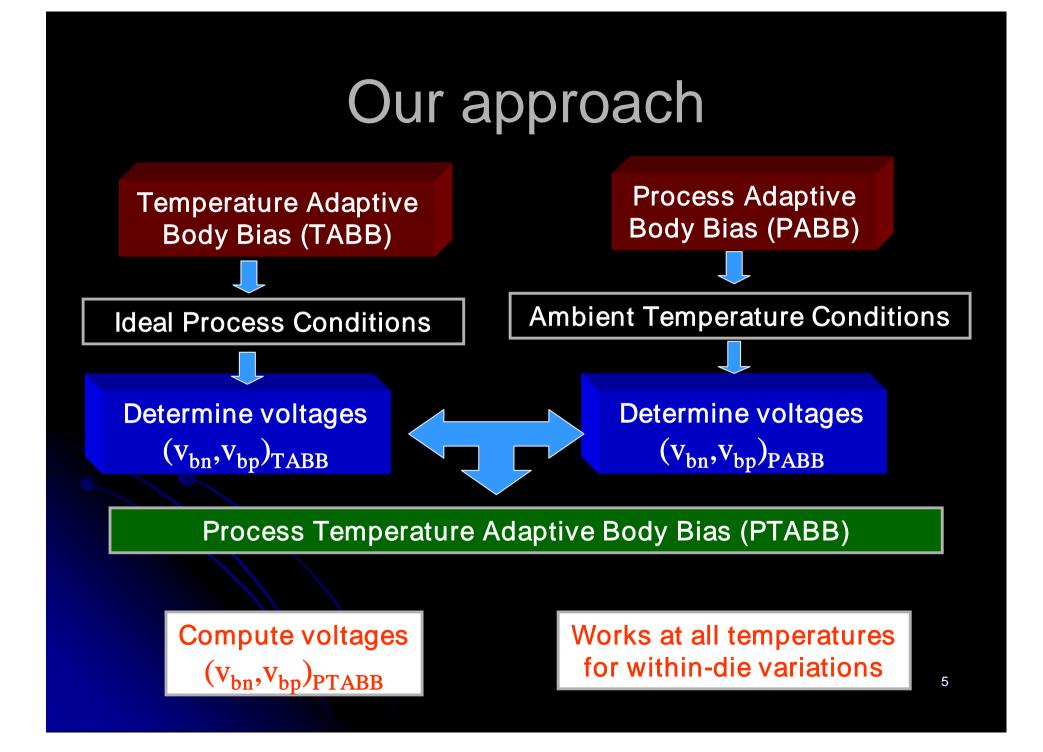

Implementation Overview

CAD Level Solution

Experimental Results

Conclusion

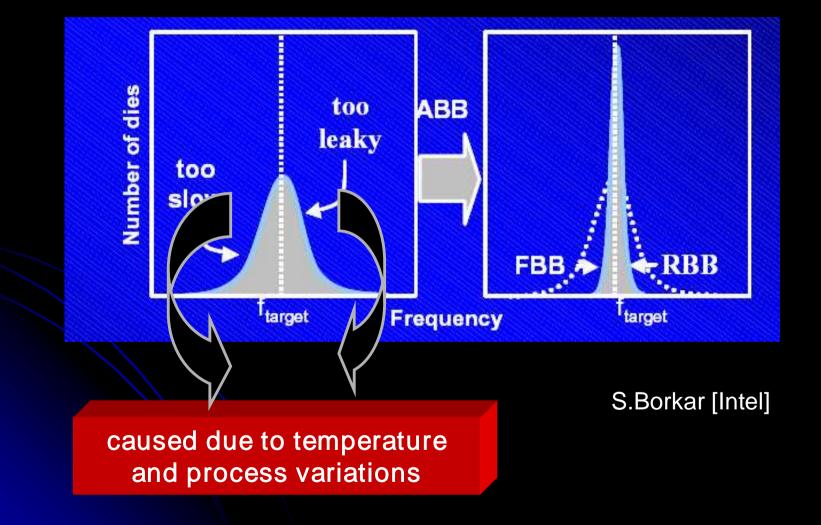

## Motivation

## **Problem Statement**

- Determine the right amount of body bias to compensate for

- process variations

- temperature variations

- Generalized framework for

- one-time compensation

- run-time compensation

- Provide a CAD level solution to the problem of determining the exact body bias values.

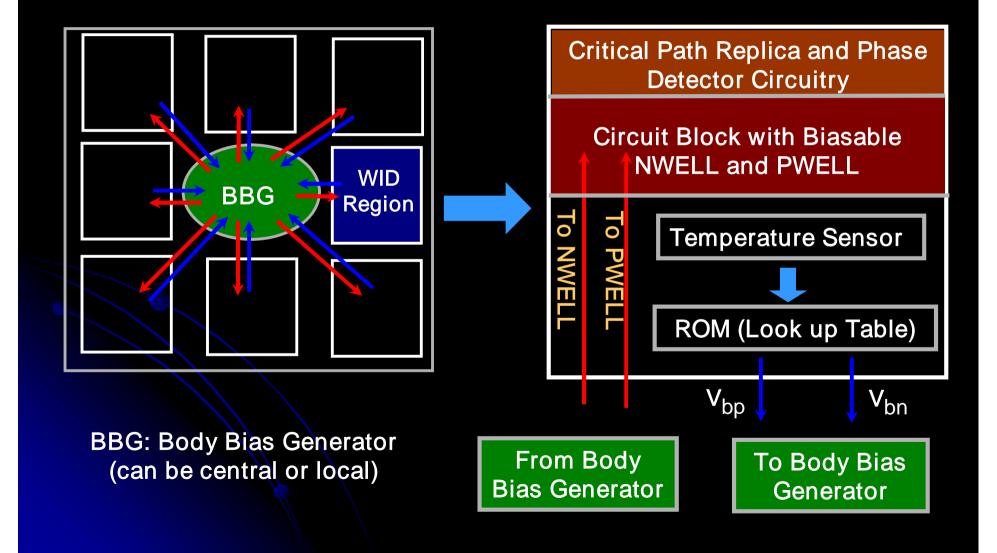

## System Level Block Diagram

#### **Temperature Compensation**

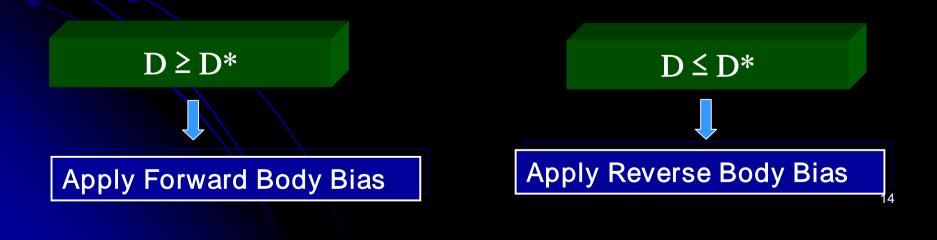

Determine the exact body bias voltage  $(v_{bn}, v_{bp})_{TABB}$  at each temperature point assuming ideal process conditions.

Performed using deterministic simulations

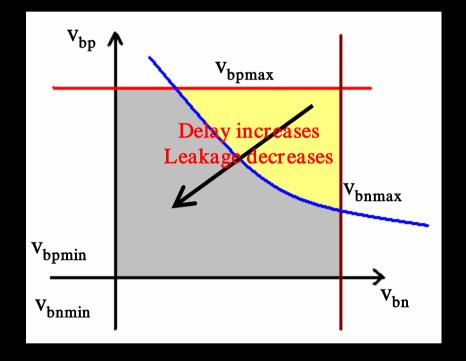

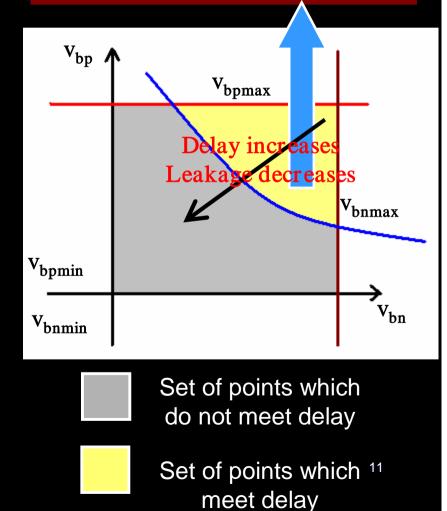

Set of points which do not meet delay

Mathematically assisted TABB

Bounded enumeration based TABB

Set of points which meet delag

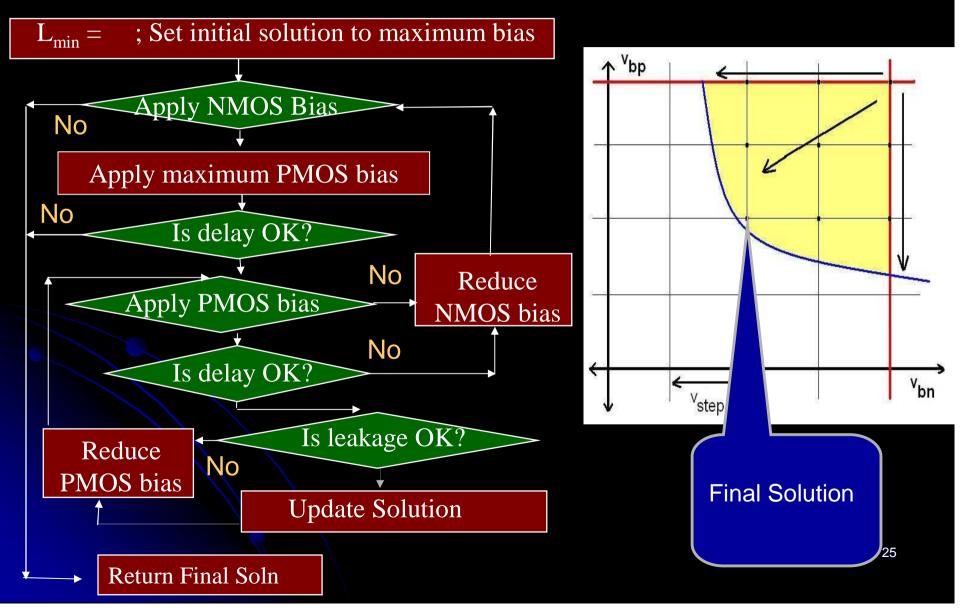

#### **Bounded Enumeration based TABB**

10

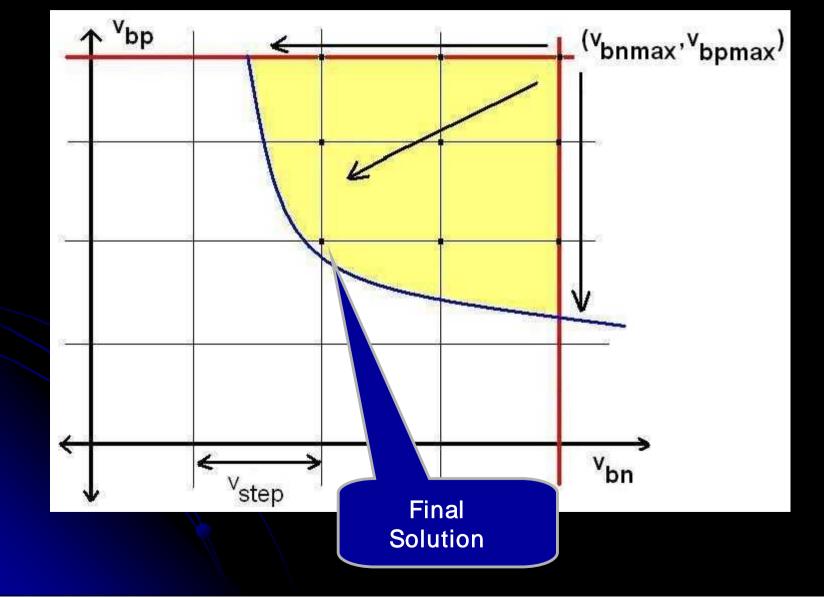

# Mathematically Assisted TABB

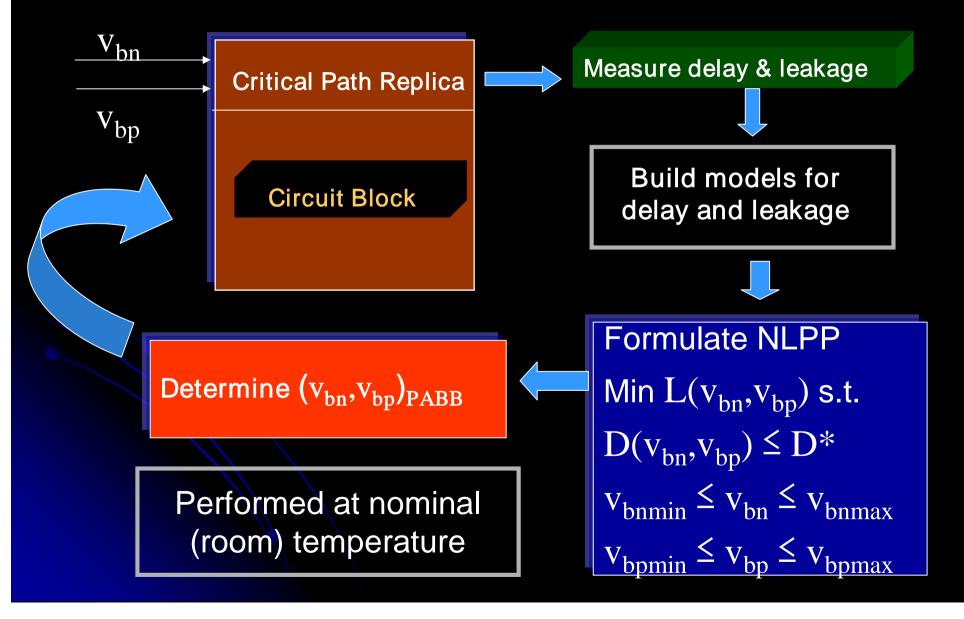

• Problem statement (NLPP) :

• Minimize  $L(v_{bn}, v_{bp})$  s.t.

- $D(v_{bn}, v_{bp}) \leq D^*$

- $v_{bnmin} \le v_{bn} \le v_{bnmax}$

- $v_{bpmin} \le v_{bp} \le v_{bpmax}$ .

- Need models for  $L(v_{bn}, v_{bp})$ and  $D(v_{bn}, v_{bp})$ .

- Use 2<sup>nd</sup> order polynomial best fit expressions.

- Measure leakage and delay at sample points through deterministic simulations.

Find the exact solution which lies along the blue line.

## Solving the NLPP

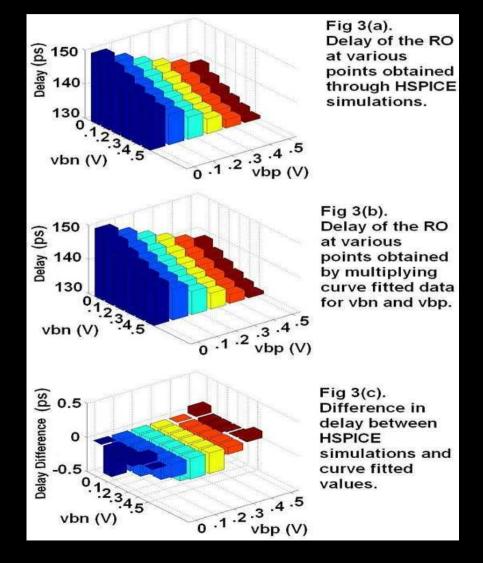

$$D(v_{bn}, v_{bp}) = D_0[\sum_{i=0}^{2} (\sum_{j=0}^{2} a_{ij} v_{bn}^j) v_{bp}^i]$$

Express delay as a product of two independent polynomials

$$D = h(v_{bn}, v_{bp}) \approx f(v_{bn})^* g(v_{bp})$$

$$f(v_{bn}) = 1 + x_1 v_{bn} + x_2 v_{bn}^2$$

$$g(v_{bp}) = 1 + y_1 v_{bp} + y_2 v_{bp}^2$$

Eliminate one variable (say V<sub>bn</sub>)

Express L in terms of  $v_{bp}$  and find the minimum value using Newton Raphson method.

#### Comparing the 2 methods

- Bounded Enumeration based TABB

- Highlights

- Simple

- Few computations

- Drawbacks

- Depends on the granularity of the voltages

- Worst case

complexity O(n<sup>2</sup>)

- Round-off error due to minimum voltage resolution

- Mathematically assisted TABB

- Highlights

- No elaborate search

- Does not depend on the voltage resolution

- Exact solution (which can be added with PABB)

- Drawbacks

- 1% modeling error

- Overkill for P-well processes

- Can be slower than TABB (if search space is limited)

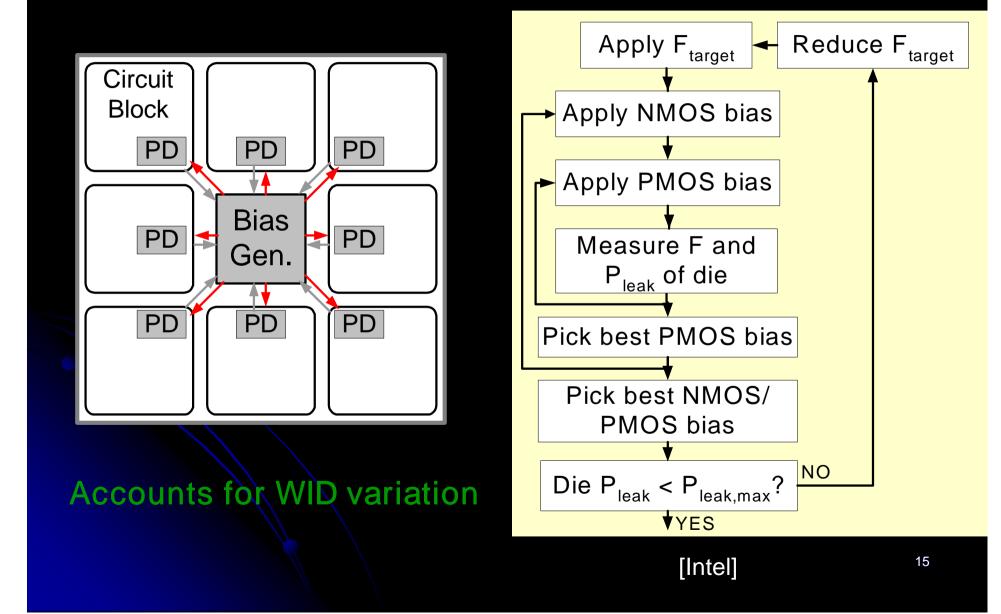

## **Process Compensation**

#### Problem Statement:

Determine the body bias pair (v<sub>bn</sub>,v<sub>bp</sub>) for each WID variational region of each die at room temperature.

Measure the delay and leakage of each WID variational region at room temperature.

## Adaptive Body Bias (ABB)

#### PABB (Process Adaptive Body Bias)

# Simulation Set-up for PTABB

• ISCAS85 benchmarks used.

- Simulations performed with BPTM 100nm technology and  $V_{dd}$ =1.0V.

- Synthesis performed using SIS.

- Library of 26 gates (10 NOT gates, 5 NAND2 gates, 5 NOR2 gates, 3 NAND3 gates and 3 NOR3 gates) of different sizes.

- Each benchmark placed in a different WID zone

- Can be independently compensated.

- Bias range (-0.5 to 0.5V) for  $v_{bn}$  and  $v_{bp}$ .

| C17  | C432 |       | 0880 |  |  |

|------|------|-------|------|--|--|

| C135 | 5    | C3540 |      |  |  |

| C531 | 5    | Ce    | 5288 |  |  |

Test structure showing each WID variational zone.

# Results of TABB

| Bench | T D* | No ABB |       | Enum TABB |                 | Math TABB       |                 | Run time        |                       |  |

|-------|------|--------|-------|-----------|-----------------|-----------------|-----------------|-----------------|-----------------------|--|

| mark  | (C)  | (ns)   | Dly   | Lkg       | v <sub>bn</sub> | v <sub>bp</sub> | V <sub>bn</sub> | v <sub>bp</sub> | Ratio                 |  |

|       |      |        | (ns)  | (uW)      | (V)             | (V)             | (V)             | (V)             | $(t_{Math}/t_{Enum})$ |  |

| C432  | 50   | 0.902  | 0.941 | 4.78      | 0.2             | 0.2             | 0.13            | 0.13            | 0.51                  |  |

| C432  | 75   |        | 0.986 | 11.2      | 0.4             | 0.4             | 0.36            | 0.42            | 1.63                  |  |

| C880  | 50   | 0.763  | 0.801 | 2.90      | 0.2             | 0.3             | 0.16            | 0.24            | 0.52                  |  |

| C880  | 75   |        | 0.838 | 6.85      | 0.5             | 0.5             | 0.49            | 0.44            | 3.11                  |  |

| C1355 | 50   | 0.83   | 0.841 | 5.06      | 0.2             | 0.3             | 0.17            | 0.24            | 0.55                  |  |

| C1355 | 75   |        | 0.879 | 11.9      | 0.5             | 0.5             | 0.5             | 0.5             | 3.10                  |  |

| C3540 | 50   | 1.33   | 1.39  | 16        | 0.2             | 0.1             | 0.19            | 0.08            | 0.41                  |  |

| C3540 | 75   |        | 1.45  | 37.5      | 0.3             | 0.4             | 0.37            | 0.32            | 0.89                  |  |

| C5315 | 50   | 1.20   | 1.25  | 14.9      | 0.2             | 0.2             | 0.19            | 0.19            | 0.42                  |  |

| C5315 | 75   |        | 1.30  | 35        | 0.3             | 0.5             | 0.40            | 0.38            | 1.17                  |  |

| C6288 | 50   | 3.64   | 3.82  | 24.7      | 0.2             | 0.2             | 0.17            | 0.19            | 0.47                  |  |

| C6288 | 75   |        | 3.99  | 57.7      | 0.4             | 0.5             | 0.37            | 0.46            | 1.75                  |  |

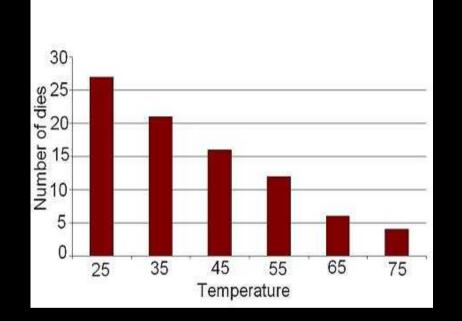

## **Process Compensation**

- PABB actually performed using post-silicon tuning.

- Simulations provide an overview of the utility of our method.

- Test structure (critical path replica) is a RO simulated using 100nm BPTM.

- RO used to determine Go-No Go for each WID.

- Monte Carlo simulations (50) done using Gaussian distributions for v<sub>tn0</sub> and

V<sub>tp0</sub>.

Simulations show that the yield is  $\approx$  50% at room temperature and decreases gradually with increase in T.

## **Process Compensation**

- For each WID region, for each die, calculate the voltages (v<sub>bn</sub>,v<sub>bp</sub>) by solving the NLPP.

- For simulation purposes, we assume that all WID regions have the same  $v_{tn0}$  and  $v_{tp0}$  distribution.

- One set of simulations on the RO can be extended to all ISCAS benchmarks.

|               | NMOS-RBB | NMOS-RBB | NMOS-FBB | NMOS-FBB |

|---------------|----------|----------|----------|----------|

|               | PMOS-RBB | PMOS-FBB | PMOS-RBB | PMOS-FBB |

| No of<br>dies | 6        | 42       | 0        | 2        |

# **PTABB** Compensation

|       | Temp | %Yield | Accepted         | P-FBB | P-RBB | P-FBB |

|-------|------|--------|------------------|-------|-------|-------|

|       |      |        | Dies (out of 50) | N-RBB | N-RBB | N-FBB |

| C432  | 50   | 100    | 50               | 35    | 0     | 15    |

| C432  | 75   | 76     | 38               | 0     | 0     | 38    |

| C880  | 50   | 100    | 50               | 24    | 0     | 26    |

| C880  | 75   | 54     | 27               | 0     | 0     | 27    |

| C1355 | 50   | 100    | 50               | 24    | 0     | 26    |

| C1355 | 75   | 48     | 24               | 0     | 0     | 24    |

| C3540 | 50   | 100    | 50               | 0     | 4     | 46    |

| C3540 | 75   | 92     | 46               | 0     | 0     | 46    |

| C5315 | 50   | 100    | 50               | 29    | 0     | 21    |

| C5315 | 75   | 76     | 38               | 0     | 0     | 38    |

| C6288 | 50   | 100    | 50               | 27    | 0     | 23    |

| C6288 | 75   | 78     | 39               | 0     | 0     | 39    |

## Conclusion

- Bidirectional Adaptive Body Bias can be used to improve the yield of dies for reasonable ranges of operating temperatures.

- New scheme to determine the exact values of body bias, PTABB compensation developed.

- One-time compensation for process variations and run-time compensation for temperature variations performed.

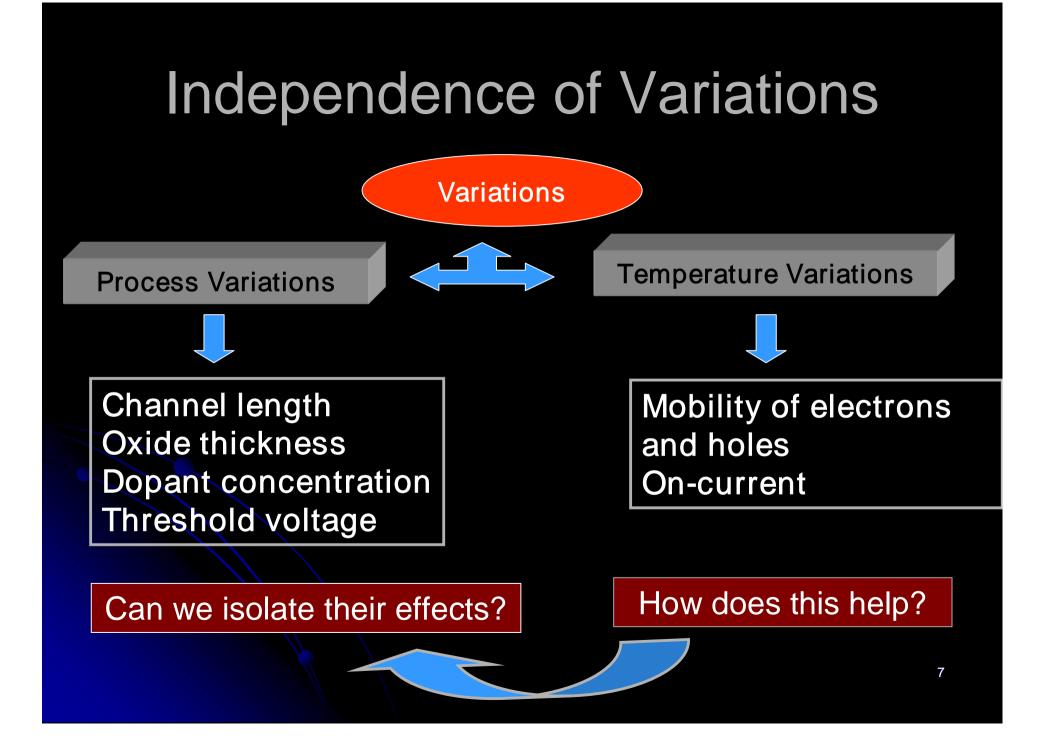

#### Independence of Variations

- Delay of a combinational circuit in the presence of temperature and process variations: D=f (x ,T)

- x is the vector of process variables

- T is the operating temperature.

- $x_0$  and  $T_0$  are the nominal values :  $f(x_0,T_0)=D^*$ .

- At any other point  $(x_1,T_1) \Delta D$  can be written as  $\Delta D = f(x_1,T_1) f(x_0,T_0)$

If x and T are independent variables,

$$\Delta D = \frac{\partial f}{\partial x} (T = T_0) \Delta x + \frac{\partial f}{\partial T} (x = x_0) \Delta T$$

$\Delta D \approx [f(x_1, T_0) - f(x_0, T_0)] + [f(x_0, T_1) - f(x_0, T_0)]$

#### **Bounded Enumeration based TABB**

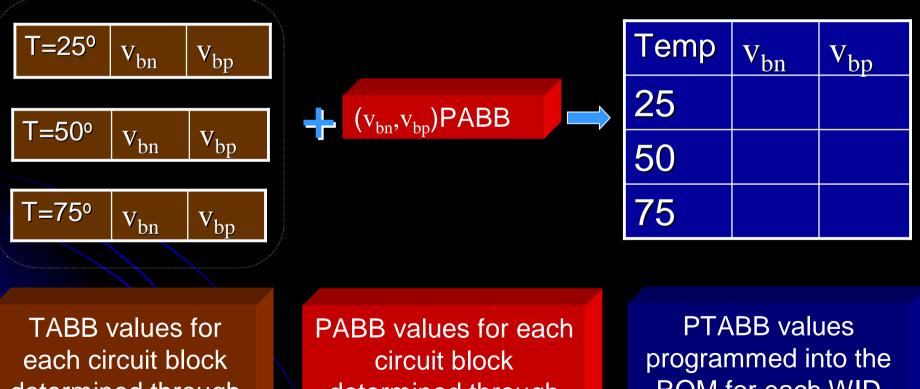

## **PTABB** Computations

$(v_{bn}, v_{bn})PTABB = (v_{bn}, v_{bn})PABB + (v_{bn}, v_{bn})TABB$

determined through simulations.

determined through post-silicon tuning.

**ROM for each WID** variational region.

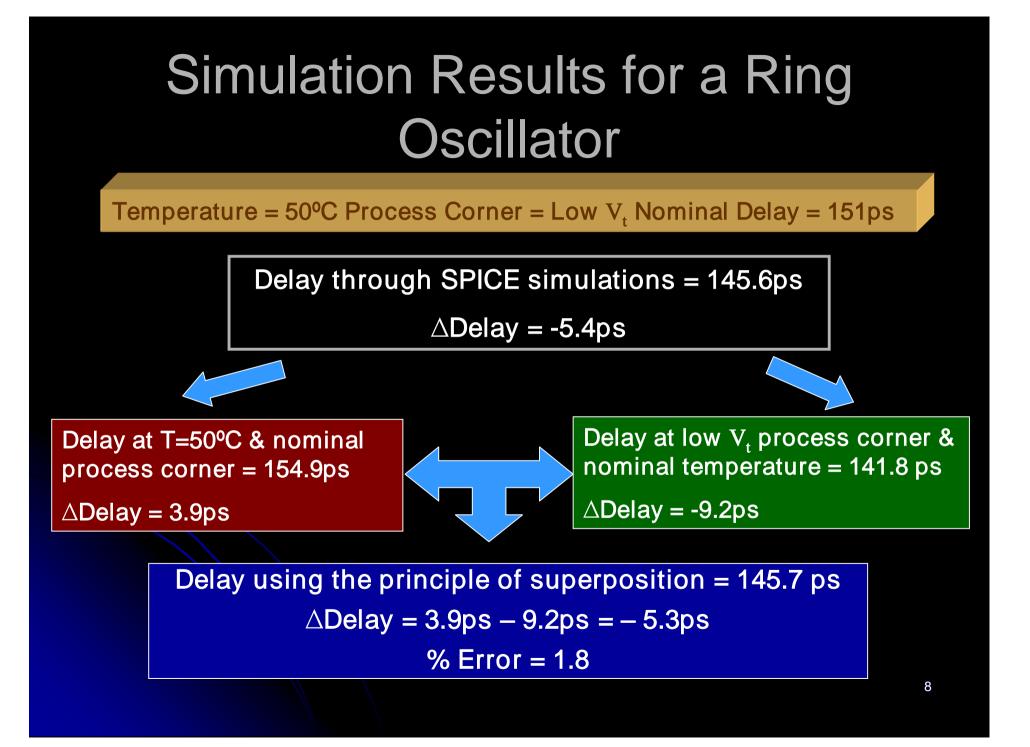

# Results of Simulation on RO

Simulation using BPTM 100nm model files

RO delay with nominal temperature and process conditions = 151ps

| Temp | Process             | DelayPT      | DelayP                                   | DelayT        | △DelayPT | △DelayP         | Diff |

|------|---------------------|--------------|------------------------------------------|---------------|----------|-----------------|------|

|      | Corner              | $f(x_1,T_1)$ | $\mathbf{f}(\mathbf{x}_1, \mathbf{T}_0)$ | $f(x_0, T_1)$ |          |                 |      |

| 50   | Low V <sub>t</sub>  | 145.6        | 141.8                                    | 154.9         | -5.4     | ∆DelayT<br>-5.3 | -0.1 |

| 50   | Low V <sub>t</sub>  | 165.3        | 161.2                                    | 154.9         | 14.3     | 14.2            | 0.1  |

| 75   | High V <sub>t</sub> | 149.2        | 141.8                                    | 158.6         | -1.8     | -1.5            | -0.3 |

| 75   | High V <sub>t</sub> | 169.3        | 161.2                                    | 158.6         | 18.3     | 17.8            | 0.5  |