Signal-Path Driven Partition and Placement for Analog Circuit

> Di Long, Xianlong Hong, Sheqin Dong EDA Lab, Tsinghua University

# Agenda

- Research Background

- Overview of the analog placement researches

- Signal-Path Driven Analog Circuit Partition

- Algorithm of Core-Circuit Placement

Algorithm of Bias-Circuit Placement

Experiment and Conclusion

## **Research Background**

SOC integrates all of the circuits on one chip

Analog circuits' design is still a manual process

The fast changes of demands in ASIC market

- Research Background

- Overview of the analog placement researches

- Signal-Path Driven Analog Circuit Partition

- Algorithm of Core-Circuit Placement

Algorithm of Bias-Circuit Placement

Experiment and Conclusion

Researches about the analog placement automation

- The constructive placement techniques

- M. Kayal--SALIM

- Iteratively combining min-cut partitioning and force-directed placement

- E. Malavasi--Quick placement with geometric constraints

- simulated annealing and genetic algorithms

ILAC, KOAN/ANAGRAM II, PUPPY-A, LAYLA

- Topological representations (BSG, SP, CBL), which still adopts the optimization engines of SA or GA and implement symmetry constraints

- Research Background

- Overview of the analog placement researches

- Signal-Path Driven Analog Circuit Partition

- Algorithm of Core-Circuit Placement

Algorithm of Bias-Circuit Placement

Experiment and Conclusion

**Observations of the Methodology**

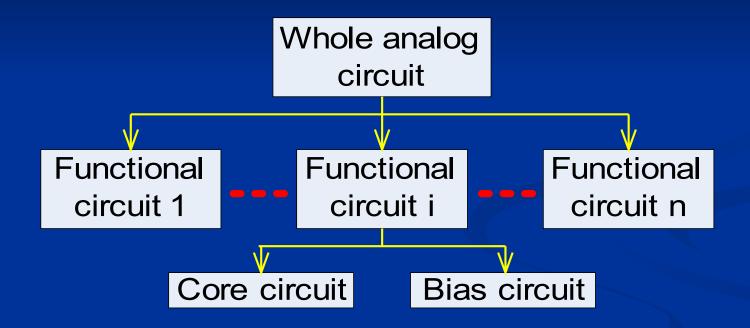

hierarchical design for analog circuit

structural feature of circuit based on signal-path

requirements of matching/symmetry constraint and the reduction of parasitics

# The methodology of hierarchical design and layout

## **Necessary Definition (1)**

core-circuit, which is the main circuit in each unit-functional circuit, is responsible for transporting and processing analog signal. **bias-circuit** is responsible for providing bias voltages and bias currents for some MOS transistors in core-circuit.

# **Necessary Definition (2)**

- power-earth transistor chain is a chain composed of transistors satisfying the following conditions

- The source/drain of each transistor in the chain must be connected to the power net or the earth net or the source/drain of another transistor in the same chain.

- There is one and only one transistor in the chain, source/drain of which is connected to the power net and there is one and only one transistor in the chain, source/drain of which is connected to the earth net.

# **Necessary Definition (3)**

signal-path is a special type of power-earth transistor chain, the generation algorithm of which is listed as follows:

- I: set of signal input nets

- $\Gamma_{pec}$ : set of all pecs

$Mj = \{g_j, s_j, d_j\}$ : set of transistor's gate net, source net and drain net

$\Phi = \{ Mj \mid Mj \cap I \not \forall \} : set of initial input transistors$

$\Psi_0 = \{ pec_i | pec_i \cap \Phi^{\dagger} \phi \}$ : initial set of signal-paths can be defined

# **Necessary Definition (4)** A loop procedure to generate the set of signal-paths $\Psi_{n+1} = \Psi_{n+1} = \Psi_{n} \cup \Psi_{sd_n} \cup \Psi_{g_n}$ $\Psi_{sd_n} = \left\{ pec_i \mid \left( pec_i \ddagger \Gamma_{pec} - \Psi_n \right) \mid \left( \exists pec \ddagger \Psi_n \right) pec_i \cap pec \ddagger \phi \right\}$ $\Psi_{g_n} = \bigotimes_{i=1}^{n} pec_i \begin{pmatrix} pec_i & \Gamma_{pec} - \Psi_n \end{pmatrix} & (\exists pec & \Psi_n \end{pmatrix} \\ (\exists Mj & pec_i) (\exists Mh & pec) s_h = g_i & d_h = g_i \end{pmatrix}$

The stop condition of the above loop procedure

$$\Psi_{sd_n} = \phi \Downarrow \Psi_{g_n} = \phi$$

#### **Comments on the sets**

$\Psi_{sd_n}$ : the current of pec<sub>i</sub> in the set is controlled by the source/drain current of pec, which is the direct front-stage of pec<sub>i</sub>

$\Psi_{g_n}$ : the current of pec<sub>i</sub> in the set is controlled by the source/drain voltage of pec, which is the direct front-stage of pec<sub>i</sub>

$\Psi_n$  is core-circuit and  $\Gamma_{pec} - \Psi_n$  is bias-circuit

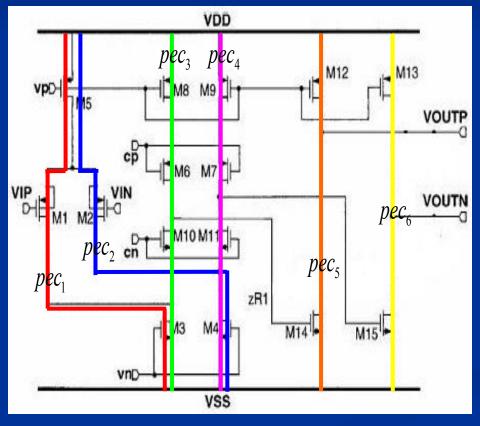

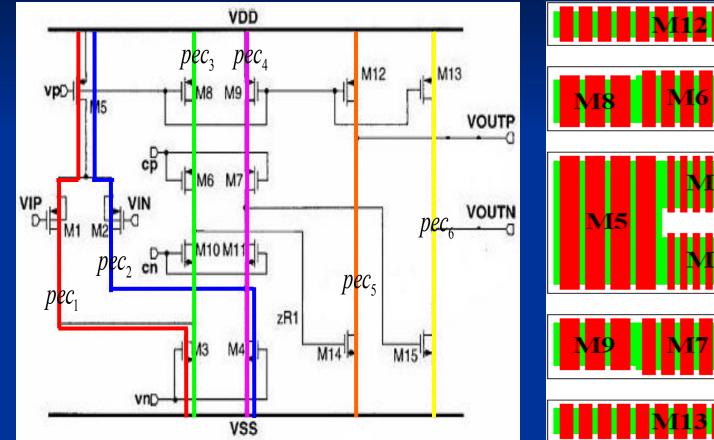

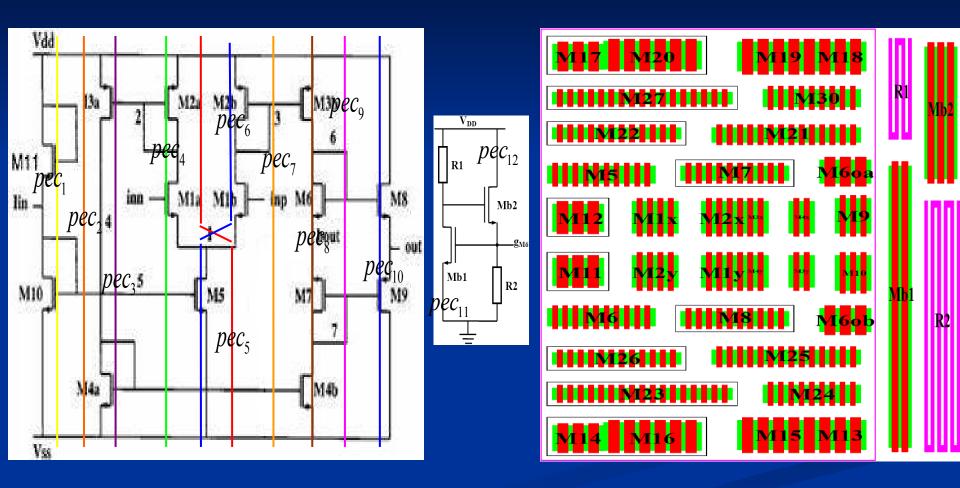

# Example for signal-path generation (1)

Schematics of full-differential Miller-compensated two-stage amplifier and the diagram of all pecs

$\Gamma_{pec} = \{ pec_1, pec_2, ..., pec_6 \} \text{ and } I = \{ VIP, VIN \}$ so  $\Phi = \{ M1, M2 \}$  and  $\Psi_0 = \{ pec_1, pec_2 \}$

when

$$n = 0$$

,  $\Psi_{sd_0} = \{pec_3, pec_4\}$  and  $\Psi_{g_0} = \emptyset$

So  $\Psi_1 = \Psi_0 \bigcup \Psi_{sd_0} \bigcup \Psi_{g_0} = \{pec_1, pec_2, pec_3, pec_4\}$

when  $n = 1, \Psi_{sd_1} = \emptyset$  and  $\Psi_{g_1} = \{pec_5, pec_6\}$ So  $\Psi_2 = \Psi_1 \bigcup \Psi_{sd_1} \bigcup \Psi_{g_1} = \{pec_1, pec_2, pec_3, pec_4, pec_5, pec_6\}$

when  $n = 2, \Psi_{sd_2} = \phi$  and  $\Psi_{g_2} = \phi$ , stop

- Research Background

- Overview of the analog placement researches

- Signal-Path Driven Analog Circuit Partition

- Algorithm of Core-Circuit Placement

Algorithm of Bias-Circuit Placement

Experiment and Conclusion

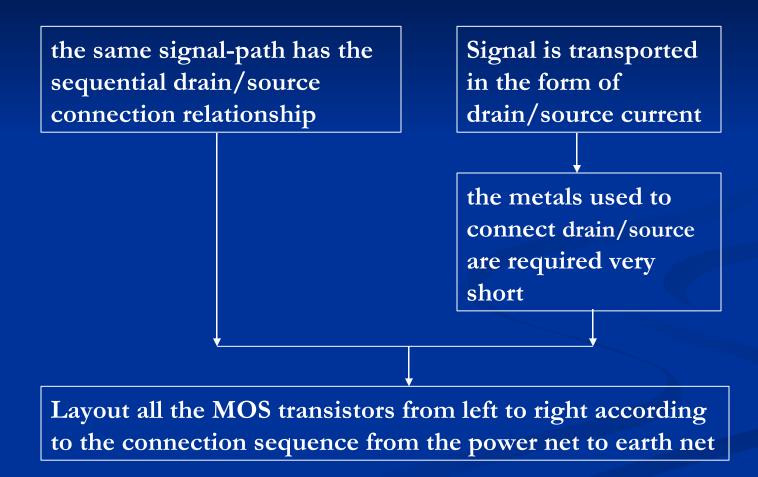

### Inner placement of each signal-path

#### whole placement of the core-circuit

Consideration: metals used to connect the nets among signal-paths are to transport the voltage, so these metals are not required very short

assuming

$$\Psi_n = \{pec_1, ..., pec_j\}$$

$\Psi_{0}, \Psi_{sd_{0}}, \Psi_{g_{0}}, \dots, \Psi_{sd_{n-1}}, \Psi_{g_{n-1}}$  is arranged by generation sequence

core-circuit is full-symmetrical structure

$\Psi_n$  is divided into  $\Psi_n = \{pec_1, ..., pec_{j/2}\}$  and  $\Psi_n = \{pec_{1+j/2}, ..., pec_j\}$

- core-circuit is not full-symmetrical structure

- part but not all of transistors in pec<sub>i</sub> have symmetry constraints with others in pec<sub>i</sub>

# Objectives of the core-circuit placement

- minimizing the differences of the height of all MOS transistor layouts in the same signal-path;

- minimizing the differences of the width of all signal-paths in the core-circuit;

- minimizing the total capacitance parasitics of all the MOS transistors;

- maximizing the area utility.

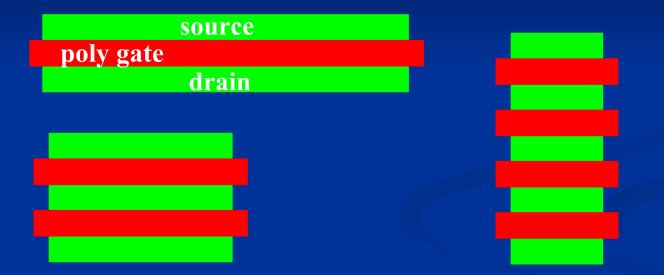

# Transistor's variants for objectives implementation

$W_m I F_m = W_n I F_n$

# Cost function to be optimized

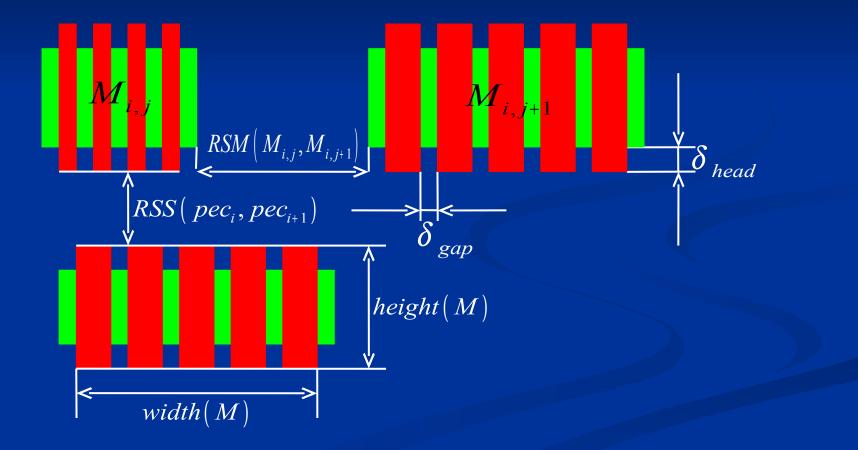

$$\begin{split} CP_{core} &= \alpha \; H_{\max\_diff} + \beta \; W_{\max\_diff} + \gamma \; P_{cap} + \delta \; (1 - U_{area}) \\ H_{\max\_diff} &= \max_{pec_k^{\dagger} \notin \pi_n} \bigotimes_{M_{k,i},M_{k,j}^{\dagger} \; pec_k} \left| height \left( M_{k,i} \right) - height \left( M_{k,j} \right) \right| \\ W_{\max\_diff} &= \max_{pec_i, pec_j^{\dagger} \notin \pi_n} \left| width(pec_i) - width(pec_j) \right| \\ P_{cap} &= \bigotimes_{i=1}^{n} \int_{j=1}^{h(i)} C_{jBSt} \left( F_{i,j} \right) \\ U_{area} &= \frac{\sum_{i=1}^{n} \int_{j=1}^{h(i)} height \left( M_{i,j} \right) I \; width \left( M_{i,j} \right) \\ \max_{pec_i^{\dagger} \notin \pi_n} \bigotimes_{i=1}^{n} vidth(pec_i) I \bigotimes_{i=1}^{l} \max_{M_{i,j}^{\dagger} pec_i} \bigotimes_{i=1}^{n} height \left( M_{i,j} \right) + \int_{i=1}^{l-1} RSS(pec_i, pec_{i+1}) \\ height \left( M_{i,j} \right) &= W_{i,j} / F_{i,j} + 2\delta_{head} \\ width (pec_i) &= \bigotimes_{j=1}^{m(i)} F_{i,j} L_{i,j} + \left( F_{i,j} + 1 \right) \delta_{gap} + \int_{j=1}^{h(i)-1} RSM \left( M_{i,j}, M_{i,j+1} \right) \end{split}$$

# Calculation of distance between transistors

# Calculation of source/drain bulk capacitance

$\left[C_{jSBt}\left(F\right) = \left(\alpha WL + \alpha W\delta_{gap} + 2\beta \delta_{gap}\right) + 2\beta \left(L + W\delta_{gap}\right)F + W\left(\alpha \delta_{gap} + 2\beta\right)\frac{1}{F}\right]$

- Research Background

- Overview of the analog placement researches

- Signal-Path Driven Analog Circuit Partition

- Algorithm of Core-Circuit Placement

Algorithm of Bias-Circuit Placement

Experiment and Conclusion

Objectives of the bias-circuit placement

minimizing the total parasitic capacitance of all the MOS transistors belonging to the bias-circuit;

minimizing the total length of routing metals;

maximizing the area utility.

$CP_{bias} = \omega P_{cap} + \theta L_{routing} + \lambda (1 - U_{area})$

- Research Background

- Overview of the analog placement researches

- Signal-Path Driven Analog Circuit Partition

- Algorithm of Core-Circuit Placement

Algorithm of Bias-Circuit Placement

Experiment and Conclusion

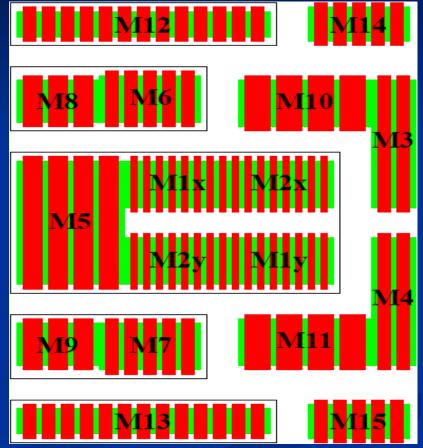

# Case 1

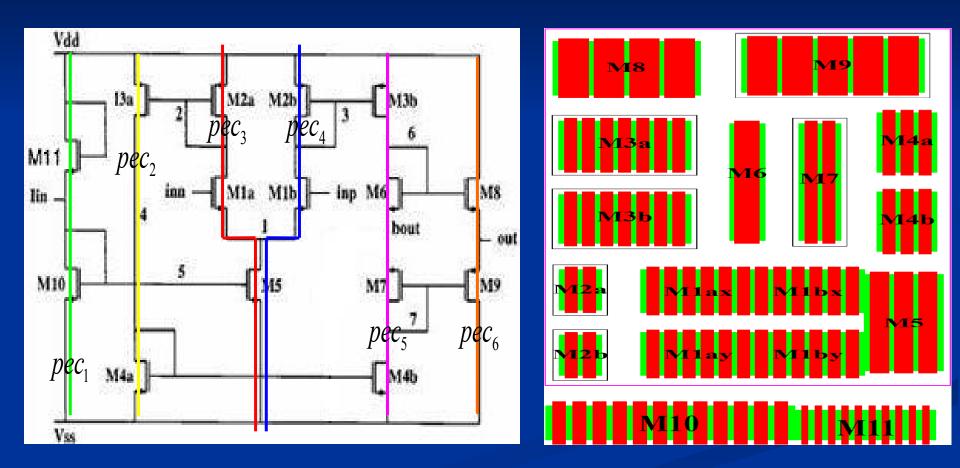

## Case 3

#### Conclusions

- a new methodology of signal-path driven partition and placement for analog

- the thinking of hierarchical design

- structural feature of analog circuit based on signal-path

- variants of MOS transistors.

- Layout is compact with high performance and it is universal and effective.