# Design Space Exploration for Minimizing Multi-Project Wafer Production Cost

Rung-Bin Lin, <u>Meng-Chiou Wu</u>, Wei-Chiu Tseng Ming-Hsine Kuo, Tsai-Ying Lin, Shr-Cheng Tsai Department of Computer Science and Engineering Yuan Ze University, Taiwan

# Outline

- Introduction

- Cost Model

- Compatibility & Area Driven Floorplanner

- Space Exploration Methodology

- Experimental Results

- Conclusions

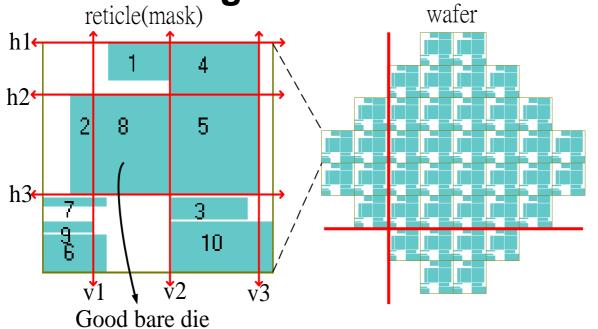

# Multiple Project Wafers (MPW)

- An MPW consists of many reticle fields, each of which has more than one chip from different projects

- To amortize mask cost and wafers' cost among chips from different projects

- Side-to-side dicing constraint

# **Reticle Floorplanning Problem**

#### Input

*N* chips, their widths and heights, their required production volumes, and the upper bounds on reticle width and height

#### Constraints

Non-overlapping constraints and side-to-side dicing constraints

#### Objective

Dicing yield is maximized

Output

The coordinates of these chips in a reticle

# Wafer Dicing Problem

#### Input

A reticle floorplan of *N* chips and the required production volumes  $V_p$  for chips *p*'s

#### Constraints

Side-to-side dicing constraint

$$V_p \leq B_p$$

(number of good bare dice)

Objective

Min Q (the number of wafers used)

Output

The wafer dicing plan for each of the Q wafers

## Ways for Satisfying Production Volumes

#### Wafer yield

$z_{k} = \min_{\forall p} B_{p} / V_{p}$ where  $B_{p}$  is the number of good bare dice,  $V_{p}$  is the required production volume, k is the given number of wafers • Estimate the number of wafers used Q $Q = k \lceil 1/z_{k} \rceil$

# Why Design Space Exploration?

- Production cost is not solely decided by the number of wafers

- Wafer lithography cost

- Reticle area → mask cost

# **Cost Analysis for Wafer Fabrication**

#### Mask cost

- The reticle area is larger, the mask cost is higher

- Main contributors

- Data preparation, mask write, mask inspection, mask repair, etc.

#### Wafer production cost

- Wafer field size (reticle size) dependent

- Exposure

- Wafer field size independent

- Hot process, etching, sputtering, polishing, materials, etc.

### **Total MPW Fabrication Cost**

$$T_{mpw}(A) = C_m(A) + Q(A) C_e(A) + Q(A) C_w$$

Where

- A: reticle area

- C<sub>m</sub>(A): mask cost

- C<sub>e</sub>(A): exposure cost per wafer

- C<sub>w</sub>: field-size independent wafer cost

- Q(A):the number of wafers needed to satisfy volume requirements

### **Exposure Cost per Wafer**

$$C_e(A) = n_A(l_v c_v + l_c c_c + l_n c_n)$$

where

- A: the wafer field size

- $n_A$ : the number of reticle on a wafer

- $I_v$ ,  $I_c$  and  $I_n$ : the number of very critical, critical, and non-critical layers, respectively

- $c_v$ ,  $c_c$  and  $c_n$ : costs per exposure for the corresponding layers

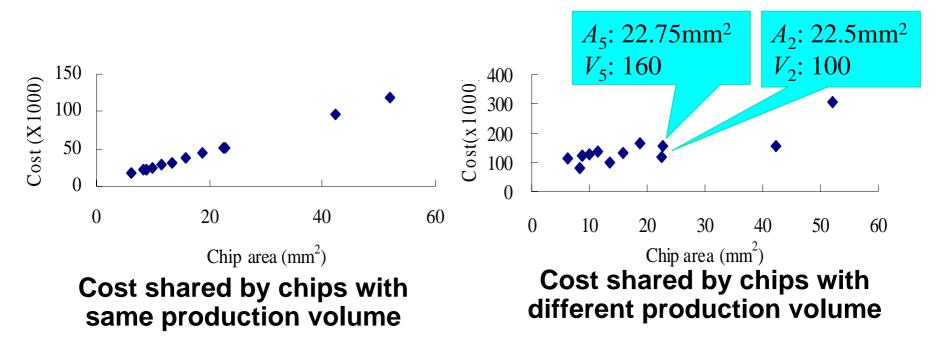

## **Our Cost Share Model**

$$C_{mpw}(p) = C_{m}(A)A_{p} / \sum_{i=1..N} A_{i} + C_{e}(A)Q(A)V_{p} / \sum_{i=1..N} V_{i} + Q(A)C_{w}A_{p}V_{p} / \sum_{i=1..N} A_{i}V_{i}$$

Where

*N*: the number of chips going with MPW

- $C_m(A)$ : the mask set cost with reticle area A  $A_i$ : the area of chip *i*

- $C_e(A)$ : the exposure cost per wafer

- Q(A): the total number of wafers used

- *C<sub>w</sub>*: the field-size independent cost per wafer

- V<sub>i</sub>: the required production volume of chip *i*

## **Production Cost Share**

#### Properties

- A smaller chip should pay less than a larger chip if they have the same production volume

- A chip with larger production volume should pay more than a chip with smaller production volume if they have the same area

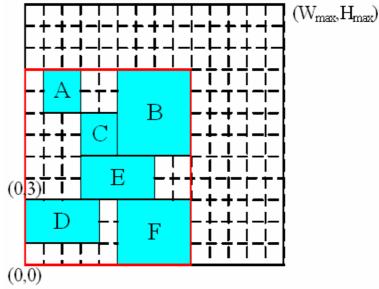

# Compatibility & Area Driven Floorplanner

Discretized reticle plane

- Neighborhood structures for SA

- Move a chip to a new location

- Rotate a chip

- Move a chip and then rotate it

- Move a chip and align it with another chip

# Compatibility & Area Driven Floorplanner cont.

#### Objective function

$$Max \quad (1 - \delta_1 - \delta_2) \sum_{p=1}^{N-1} \left( \sum_{q=p+1}^{N} E_{pq}(V_p + V_q) \right) - \delta_1 \beta W H - \delta_2 \beta R$$

#### where

#### *E<sub>pq</sub>*: 1 if chips *p* and *q* are compatible $\beta = (N-1)\sum_{p=1}^{N} V_p / (W_{max}H_{max})$ : normalizing factor *W*(*H*): reticle width(height) *R*: the total overlap area of chips

$\delta_1(\delta_2)$  : coefficient for reticle and compatibility (penalty)

## **Space Exploration Methodology**

Use the SA floorplanner to perform reticle floorplanning design space exploration with different weighting on compatibility and reticle area

Employ the *HVMIS-SA-Z* dicing method [6] to obtain the number of wafers used for each floorplan

Calculate the total fabrication cost based on the reticle size and the number of wafers needed for each floorplan

Select the floorplan with least production cost

Compute cost shared by each project

# **Experimental Setup**

- 300mm wafers

- 8 very critical layers (I<sub>v</sub>), 8 critical layers (I<sub>c</sub>), and 12 non-critical layers (I<sub>n</sub>) from [7]

- Costs per exposure from [7]: c<sub>v</sub>=\$2.5, c<sub>c</sub>=\$1.5, c<sub>n</sub>=\$0.5

- Field size independent wafer cost (C<sub>w</sub>) from [12]: \$2500

# Mask Cost & Test Cases

#### Source: [7]

| Wafer      | 25*25              | 16*24   | 16*16   | 8*16    | 8*8     |

|------------|--------------------|---------|---------|---------|---------|

| field size | 625mm <sup>2</sup> | 384 mm² | 256 mm² | 128 mm² | 64mm²   |

| Mask cost  | 1,240,000          | 728,000 | 532,000 | 352,000 | 296,000 |

|    | ( <i>w</i> , <i>h</i>   1X required volume) <i>W</i> <sub>max</sub> =20 mm, <i>H</i> <sub>max</sub> =20 mm                                                                                                                                       |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 | (2.5,6.25   100 ), (1.8,5.5   200), (2,1.25   300), (2.2,1.75  <br>200), (1.7,2.25   200), (1.5,1.55   200), (2.3,3.75   200),<br>(1,3.25   200), (1.3,4.25   80), (2.7, 1.1   60)                                                               |

| 16 | (6.5, 6.5   60), (4.5, 5.0   100), (5.5, 1.5   120), (4.5, 3.0   120),<br>(6.5, 3.5   160), (4.5, 3.5   160), (6.5, 8.0   200), (3.3, 3.5  <br>200), (2.5, 3.5   200), (3.5, 2.5   200), (7.5, 2.5   200), (4.0,<br>2.5   200), (2.5, 2.5   200) |

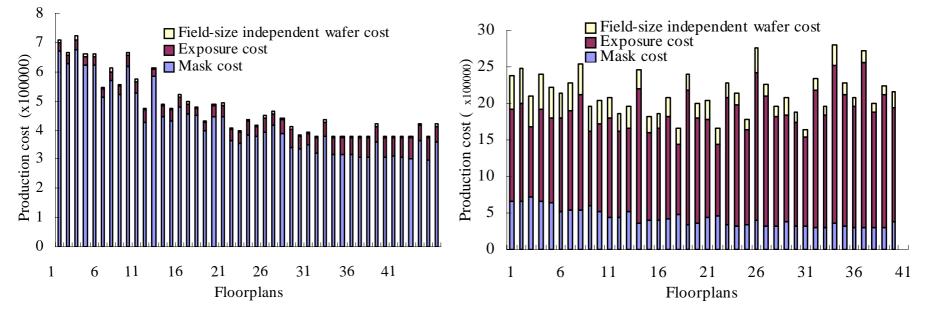

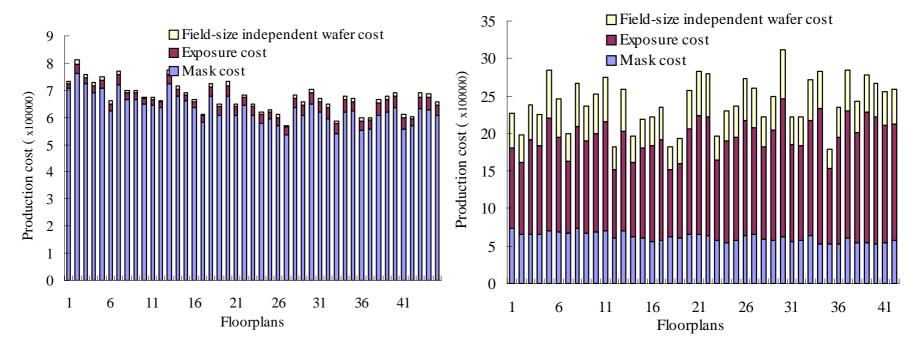

### **MPW Production Cost**

#### 48% saving w/r poorest 34% saving w/r average

#### 41% saving w/r poorest 24% saving w/r average

I5 with 50X volume

### **MPW Production Cost**

#### 30% saving w/r poorest 17% saving w/r average

#### 42% saving w/r poorest 22% saving w/r average

I6 with 1X volume

**I6 with 50X volume**

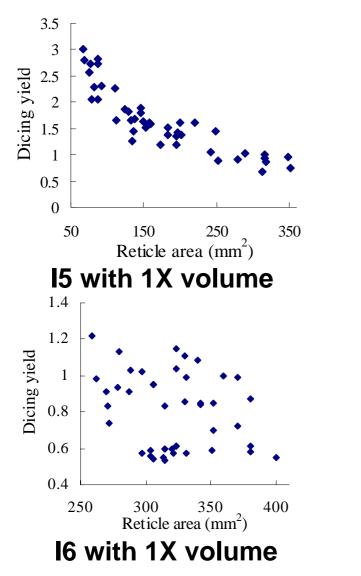

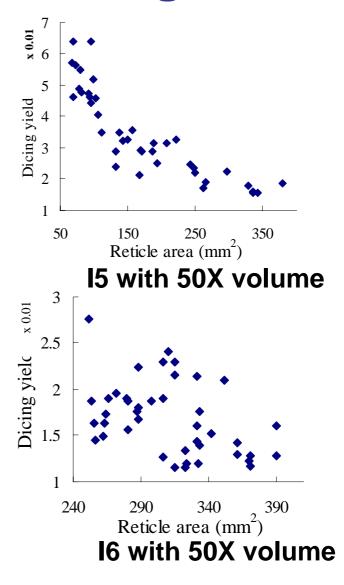

### **Reticle area vs. Dicing Yield**

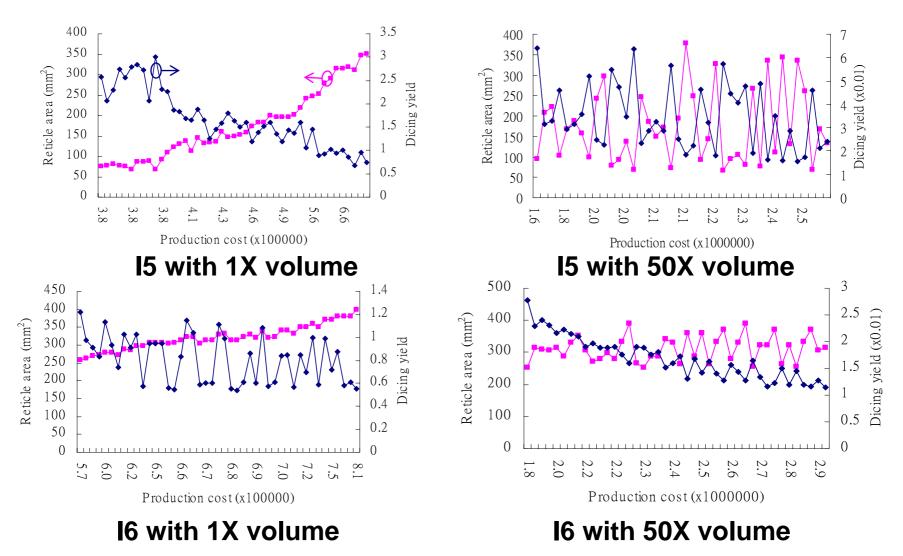

### Reticle Area, Dicing Yield, and Production Cost

# Conclusions

- A methodology to explore MPW reticle floorplan design space

- A compatibility and area-driven floorplanner based on SA

- A new formula for computing the MPW fabrication cost assumed by each chip

- A good floorplan saving up to 48% cost for small volume production and 42% cost for medium volume production

- Although reticle area generally corresponds well to production cost, especially for small volume production, a design space exploration is strongly recommended for achieving minimal-cost production

# Thank you for your attention!