# Single-Issue 1500MIPS Embedded **DSP with Ultra Compact Codes**

Li-Chun Lin, Shih-Hao Ou, Tay-Jyi Lin, Siang-Sen Deng, and Chih-Wei Liu

> Department of Electronics Engineering National Chiao Tung University

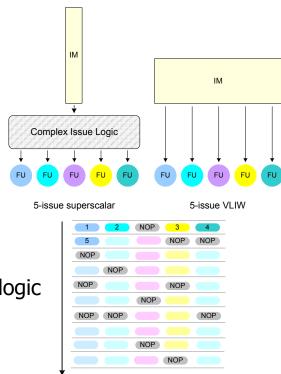

# **▶** Architecture Issue

- Single-issue RISC cores

- Only one FU is activated

- → low hardware utilization

- Multi-issue architecture

- Pros

- Better performance

- Higher hardware utilization

- Cons

- Superscalar: complex issue logic

- VLIW: poor code density

- Our proposed architecture

- Simpler single-issue unit with vector processing

- Peak performance as that of VLIW

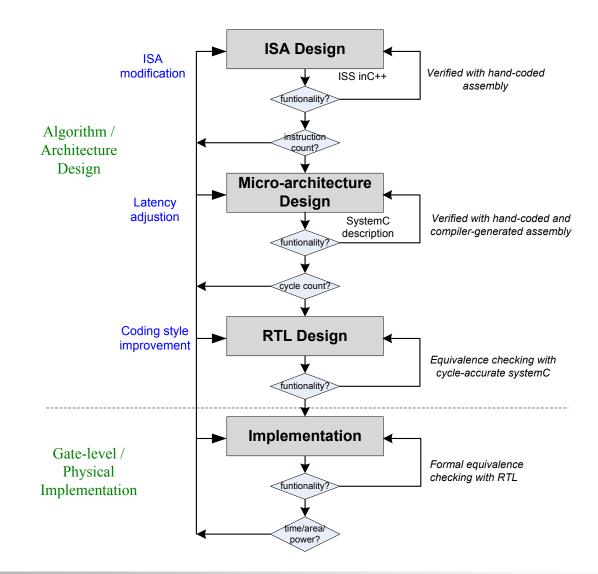

# **Design Flow**

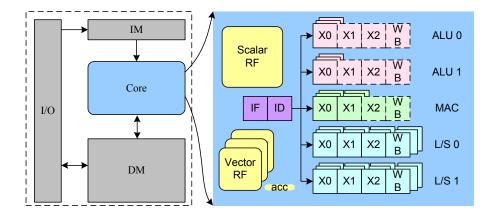

# Processor Design (1/2)

- Instruction set architecture design

- Register file organization

- Scalar RF

- Vector RF

- Accumulator

- Instruction set

- Three types

- scalar instructions

- vector-scalar instructions

- vector instructions

- Functionality

- program flow control

- memory reference

- arithmetic

- Instruction encoding

- 16/32-bit encoding for instructions with/without immediate

- Instruction-set simulator in cycle-accurate SystemC

Institute of Electronics, National Chiao Tung University

# Processor Design (2/2)

- Design space exploration

- Functional unit configuration

- Vector length

- Number of vector registers

- Micro-architecture design

- Single-issue logic modified from RISC

- 6-state pipeline

# Institute of Electronics, National Chiao Tung University

# >> Performance Evaluation

|                | <u>TI C55x</u> |            | Proposed DSP |            |

|----------------|----------------|------------|--------------|------------|

|                | Cycle counts   | Code sizes | Cycle counts | Code sizes |

| FIR filtering  | N*(T+2)/2+18   | 99         | N*(T+9)+6    | 54         |

| Vector add.    | N+7            | 66         | 3*N/2+5      | 40         |

| Vector max.    | N/2+15         | 99         | N+15         | 56         |

| 8-point 1D DCT | 67             | 94         | 82           | 50         |

\*code sizes in bytes

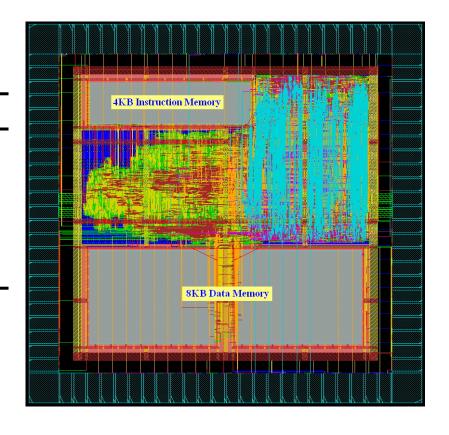

# >> Silicon Implementation

| Technology            | TSMC 0.13um 1P8M CMOS       |  |  |

|-----------------------|-----------------------------|--|--|

| Core size             | 1.45 x 1.40 mm <sup>2</sup> |  |  |

| On-chip memory        | 8KB DM & 4KB IM             |  |  |

| Transistor/gate count | 269,739                     |  |  |

| Max. frequency        | 305MHz                      |  |  |

| Power dissipation     | 38mW                        |  |  |