# An Interconnect-Centric Approach to Cyclic Shifter Design

Haikun Zhu, Yi Zhu C.-K. Cheng Harvey Mudd College. David M. Harris Harvey Mudd College.

### Outline

- Motivation

- Previous Work

- Approaches

- Fanout-Splitting

- Cell order optimization by ILP

- Conclusions

### Motivation

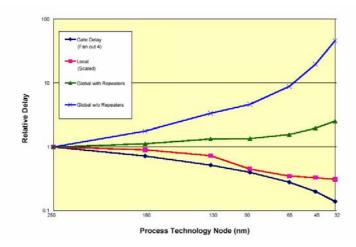

- Interconnect dominates gate in present process technology

- Delay, power, reliability, process variation, etc.

Source: ITRS roadmap 2005

Conventional datapath design focuses on logic depth minimization

# Technology Trends

• Device (ITRS roadmap 2005, Table 40a)

| Gate length (nm)          | 90    | 65    | % decreasing |

|---------------------------|-------|-------|--------------|

| Vdd (V)                   | 1.1   | 1.1   | -            |

| Vth (V)                   | 0.195 | 0.165 | -            |

| NMOS gate Cap (fF/µm)     | 0.573 | 0.469 | 18.2%        |

| NMOS intrinsic delay (ps) | 0.870 | 0.640 | 26.4%        |

• Updated Berkeley Predictive Interconnect Model

| Gate length (nm)                          | 90    | 65    | % decreasing |

|-------------------------------------------|-------|-------|--------------|

| Inter-layer dielectric<br>constant        | 2.8   | 2.6   | -            |

| Capacitance of local interconnect (fF/um) | 0.186 | 0.173 | 7.0%         |

# Shifter Taxonomy

- Functionality

- Logical Shift: MSBs stuffed with 0's

- Arithmetic Shift: Extend original MSB

- Cyclic Shift (rotation)

- Bidirectional Shift

- Circuit Topology

- Barrel Shifter

- Logarithmic Shifter

### **Barrel Shifter**

- Pros

- Every data signal pass only one transmission gate

- Cons

- Input capacitance is O(N)

- # transistors =  $O(N^2)$

- Requires additional decoder for control signals

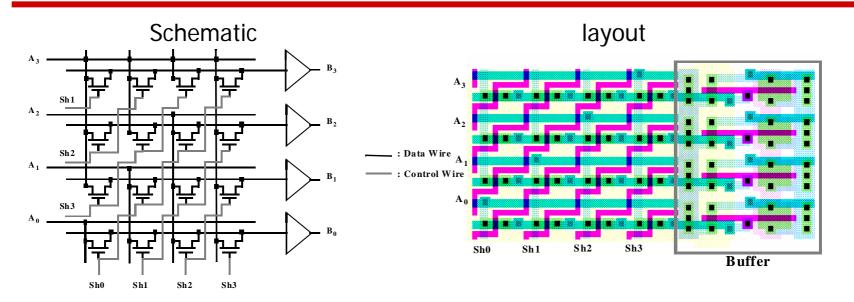

### Logarithmic Shifter

Schematic

layout

- Pros

- # transistors =  $O(N \log_2 N)$

- Cons

- Long inter-stage wires, especially for cyclic shifter Target of Optimization

## Cyclic Shifter -- Applications

- Finite Field Arithmetic

- In normal basis, squaring is done by cyclic shifting.

- Encryption

- ShiftRows operation in Rijndael algorithm.

- DCT processing unit

- Address generator

- Bidirectional shifting

- Can be implemented as a cyclic shifter with additional masking logic

- CORDIC algorithm

- etc ...

### **Previous Work**

- Bit interleave

- Two dimensional folding strategy

- Gate duplicating

- Ternary shifting

- Comparison between barrel shifter and log shifter

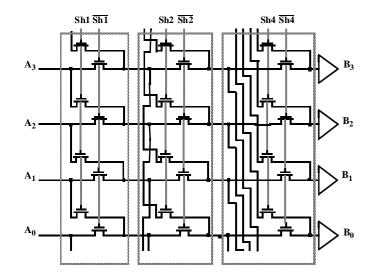

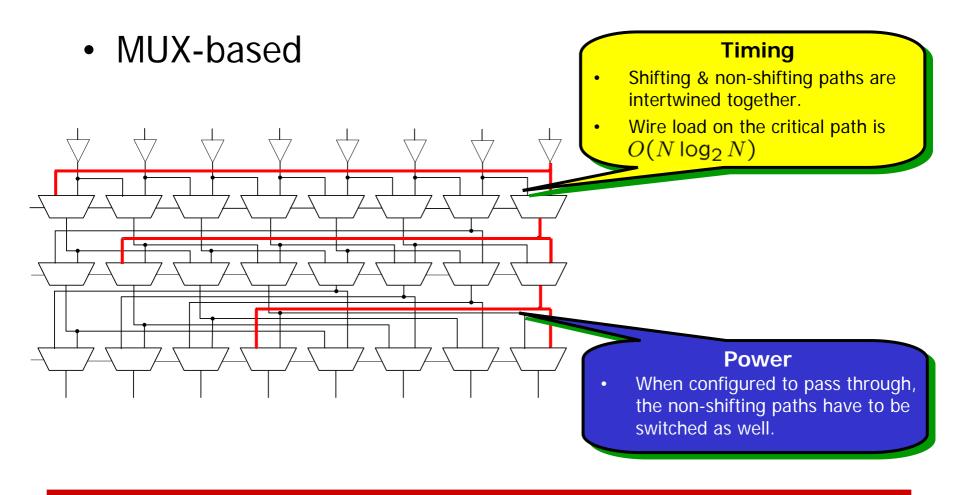

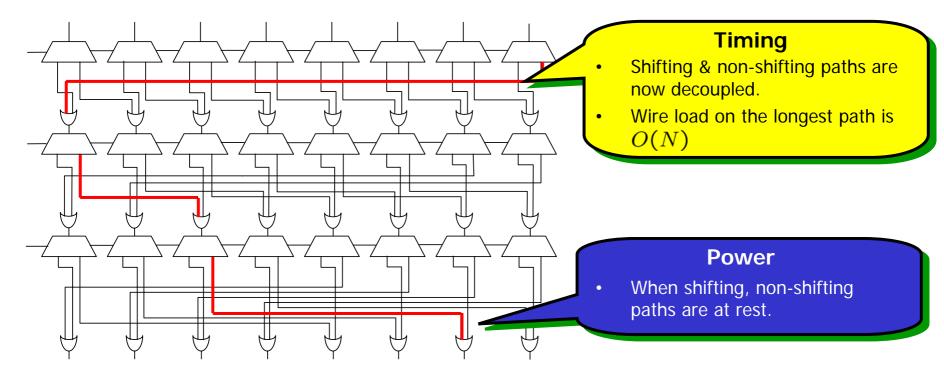

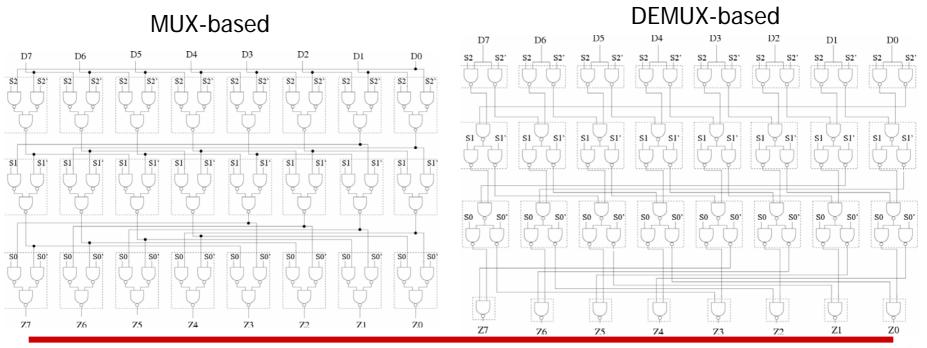

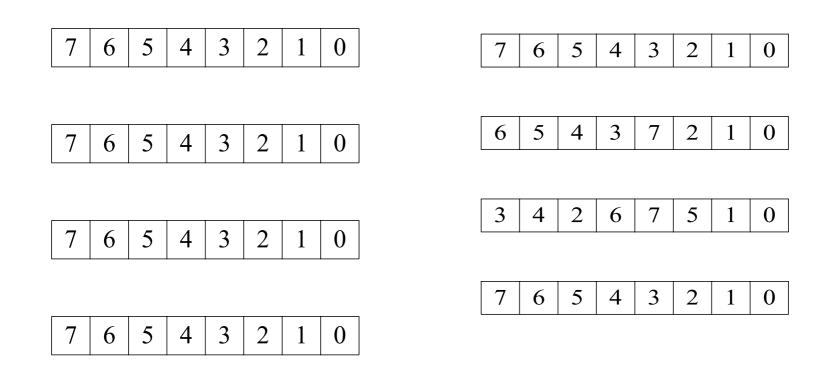

### Cyclic Shifter – Traditional Design

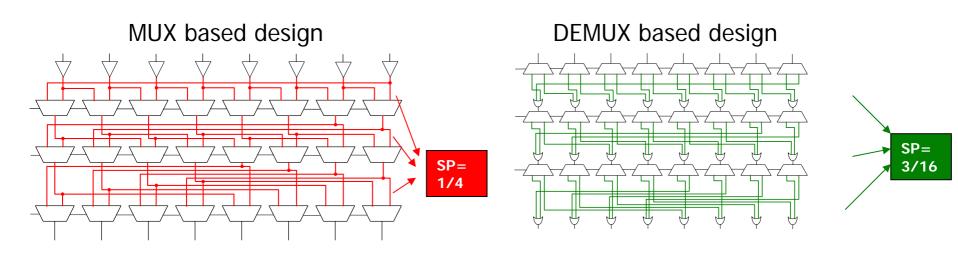

# Fanout Splitting Shifter

Use DEMUXes instead of MUXes

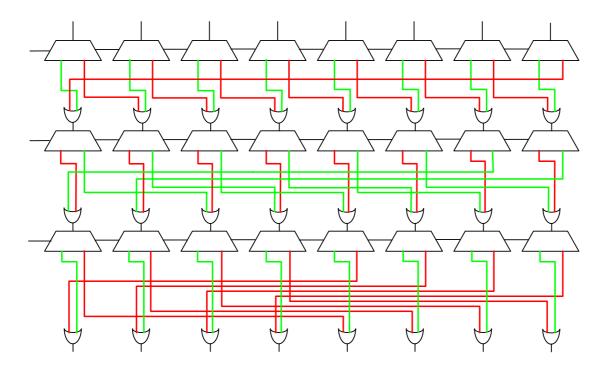

### Example

Right rotate 5 bits

Red lines are signal lines Green lines are quiet lines

### **Dynamic Power Consumption**

- Dynamic Power  $P_{\text{dynamic}} = \frac{C_{\text{eff}}V_{\text{supply}}^2}{2} = \frac{(C_{\text{load}}P_{0\to 1})V_{\text{supply}}^2}{2}$

- Switching Probability  $P_{X|0->1} = P_{X=0}(1 P_{X=0})$

SP = Switching Probability

### Gate Complexity

- Re-factoring design

- No extra complexity at gate level, both are O(N log<sub>2</sub> N)

### Duality

- Duality provides flexibility for low level implementation

- NAND gates are good for static CMOS.

- NOR gates are good for dynamic circuits.

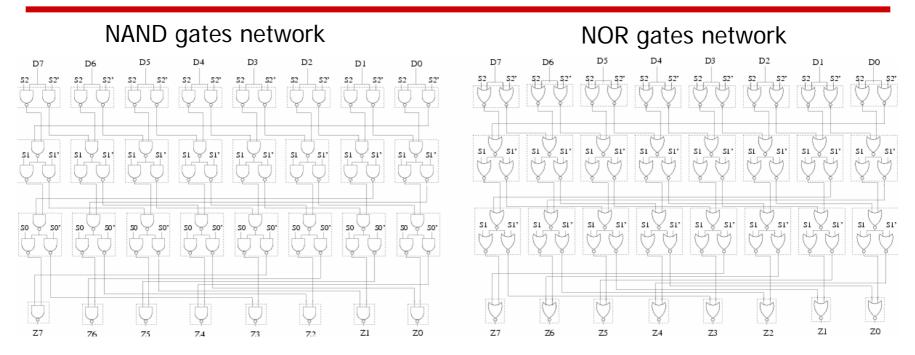

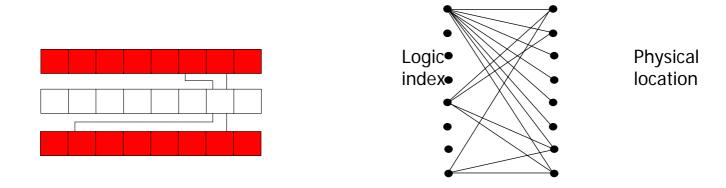

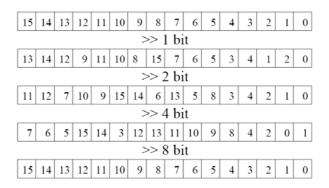

### **Cell Permutation**

- Datapath usually assumes bit-slice structure

- The cell order of the input/output stages must be fixed

- However, the cells in the intermediate stages are free to permute.

### **Problem Statement**

- Given

- A N-bit rotator

- Fixed linear order of the input/output stages

- Find

- An optimal permutation scheme of the intermediate stages such that the longest path is minimized (or, the total wire length s.t. delay constraint).

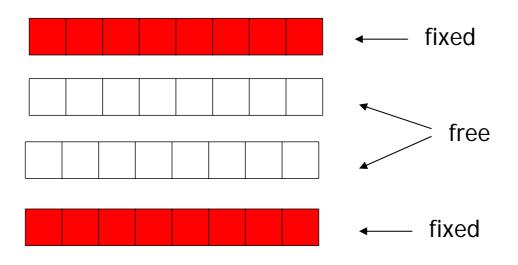

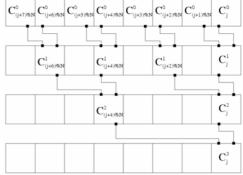

### **ILP** Formulation

- Introduce a set of binary decision variables  $x_{ij}^l \in \{0, 1\}$

- $x_{ij}^l = 1$  if and only if logic cell *i* is at physical location *j* on level *l*

- The solution space is fully defined by constraints

$$\sum_{i=0}^{N-1} x_{ij}^l = 1 \quad (0 \le j \le N-1, 1 \le l \le n-1)$$

$$\sum_{j=0}^{N-1} x_{ij}^l = 1 \quad (0 \le i \le N-1, 1 \le l \le n-1)$$

# ILP Formulation (cont')

### Minimum delay formulation

$T_{\max} = \max\{ \text{length of the delay path from} \\ C_i^0 \text{ to } C_j^n, \ 0 \leq i,j \leq N-1 \}$

#### Which can be expanded into

$T_{\max} \ge \text{length of the delay path from } C_i^0 \text{ to } C_j^n$ for  $0 \le i, j \le N-1$

objective

minimize  $T_{max}$

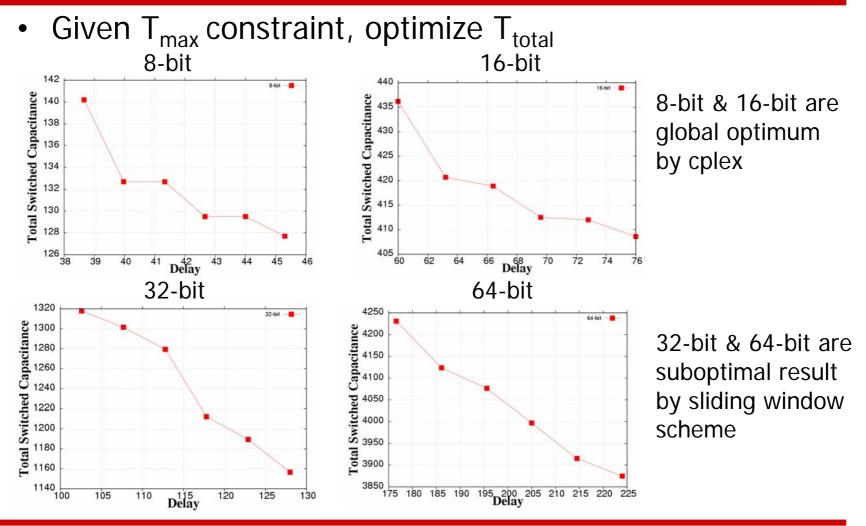

### • Minimum power formulation

minimize  $T_{total}$ s.t.  $T_{max} < const$

# ILP Formulation (cont')

Represent the length of a single wire segment

$$d = \Big|\sum_{j=1}^{N-1} j \cdot x_{i_1 j}^0 - \sum_{j=2}^{N-1} j \cdot x_{i_2 j}^1\Big|$$

Formulating absolute operation

$$d = |D| \quad \Rightarrow d = \max\{D, -D\}$$

$$\Rightarrow \begin{cases} d \ge D \\ d \ge -D \\ d \le D + \mathsf{INF} \cdot g \\ d \le -D + \mathsf{INF} \cdot (1) \end{cases}$$

Psuedo-linear constraints discarded because we're trying to minimize

Ŷ)

### Complexity

- Minimum total wire length formulation

- The case of one level of free cells is a minimum weight bipartite matching problem

- For the case of two or more levels of free cells, optimal polynomial algorithm is unknown

- Hardness of minimum delay formulation unestablished.

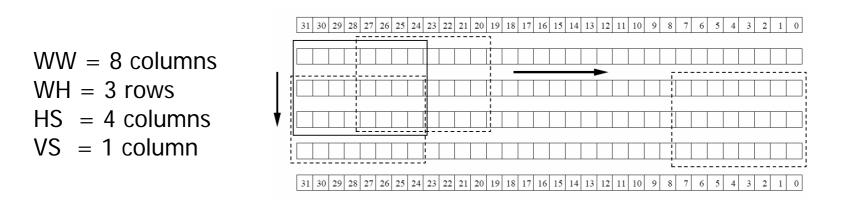

# ILP Complexity

- The ILP formulation does not scale well

- Both #integer variables and #constraints are  $O(N^2)$

- CPLEX uses on branch & bound exponential growth

- Sliding window scheme

- Only cells in the window are allowed to permute

- Consists of multiple passes; terminate when there is no improvement between passes

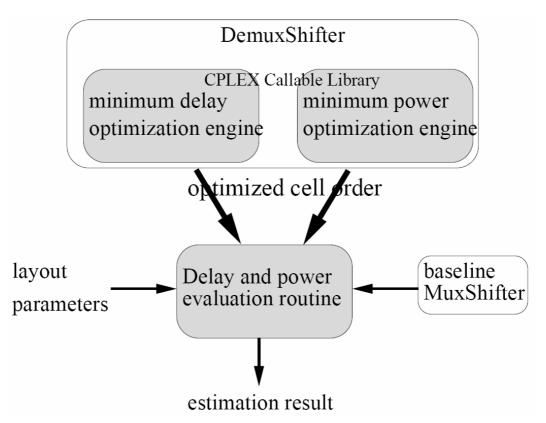

### **Power & Delay Evaluation**

• Overall Flow

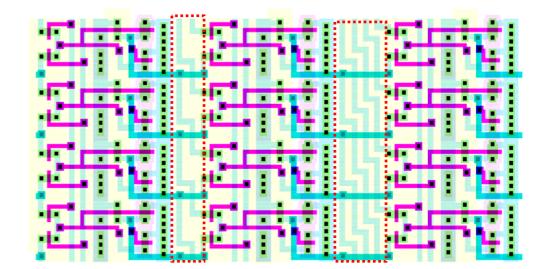

### Optimal solution for 8-bit case

A global optimal solution

### 16-bit and 32-bit cases

#### 16-bit, global optimal solution

#### 32-bit, suboptimal solution by sliding window method

| 31 | 30        | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16   | 15   | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6  | 5 | 4 | 3 | 2 | 1 | 0 |

|----|-----------|----|----|----|----|----|----|----|----|----|----|----|----|----|------|------|----|----|----|----|----|----|---|---|----|---|---|---|---|---|---|

|    | >> 1 bit  |    |    |    |    |    |    |    |    |    |    |    |    |    |      |      |    |    |    |    |    |    |   |   |    |   |   |   |   |   |   |

| 30 | 29        | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15   | 31   | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 6 | 7  | 5 | 4 | 3 | 2 | 1 | 0 |

|    | >> 2 bit  |    |    |    |    |    |    |    |    |    |    |    |    |    |      |      |    |    |    |    |    |    |   |   |    |   |   |   |   |   |   |

| 28 | 27        | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 31 | 15 | 14   | 30   | 13 | 12 | 29 | 11 | 10 | 9  | 8 | 7 | 5  | 6 | 4 | 3 | 0 | 1 | 2 |

|    | >> 4 bit  |    |    |    |    |    |    |    |    |    |    |    |    |    |      |      |    |    |    |    |    |    |   |   |    |   |   |   |   |   |   |

| 24 | 23        | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 31 | 13 | 12 | 30 | 29   | 28   | 27 | 26 | 11 | 10 | 25 | 8  | 9 | 7 | 6  | 5 | 2 | 3 | 4 | 0 | 1 |

|    |           |    |    |    |    |    |    |    |    |    |    |    |    | >  | >> { | 3 bi | t  |    |    |    |    |    |   |   |    |   |   |   |   |   |   |

| 15 | 14        | 13 | 12 | 16 | 11 | 10 | 31 | 9  | 8  | 30 | 29 | 28 | 27 | 26 | 25   | 24   | 23 | 22 | 21 | 20 | 19 | 18 | 7 | 6 | 17 | 5 | 2 | 4 | 3 | 1 | 0 |

|    | >> 16 bit |    |    |    |    |    |    |    |    |    |    |    |    |    |      |      |    |    |    |    |    |    |   |   |    |   |   |   |   |   |   |

| 31 | 30        | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16   | 15   | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6  | 5 | 4 | 3 | 2 | 1 | 0 |

|    |           |    |    |    |    |    |    |    |    |    |    |    |    |    |      |      |    |    |    |    |    |    |   |   |    |   |   |   |   |   |   |

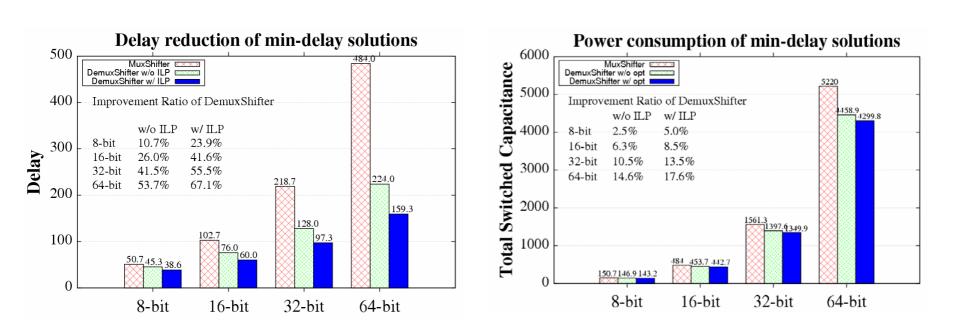

### **Analysis Results**

### **Power-Delay Tradeoff**

### **Implementation Results**

- Implementation methodology

- Standard cell based design using relative placement (by synopsys Physical Compiler)

- Routing and timing analysis in synopsys Astro

- Power estimation by synopsys PrimePower

- Control signals manually buffered following FO4 rule

- TSMC 90nm technology

- Three types of designs investigated

- Mux shifter using NAND2X2 gates

- Mux shifter using MX2X2 gates

- Demux shifter using NAND2X2 gates

### Implementation Results – Cont'

- 64-bit results

- Most improvement comes from the interconnect

|                                 | De                   | lay Compone  | nts          | muxsft64 <sup>A</sup> | muxsft64 <sup>B</sup> | Demuxsft64 <sup>C</sup> | Imp.  |  |

|---------------------------------|----------------------|--------------|--------------|-----------------------|-----------------------|-------------------------|-------|--|

|                                 | Gate Wire load Xtalk |              | (NAND2X2)    | (MX2X2)               | (NAND2X2)             | ( <mark>C/A</mark> )    |       |  |

| Global critical path            | $\checkmark$         |              |              | 0.7243                | 0.8731                | 0.7243                  | 0%    |  |

| delay (ns)                      | $\checkmark$         | $\checkmark$ |              | 1.5534                | 1.5534                | 1.1135                  | 28%   |  |

|                                 | $\checkmark$         | √ √          |              | 1.9599                | 2.073                 | 1.4503                  | 26%   |  |

| Critical data-                  | $\checkmark$         |              |              | 0.4839                | 0.6120                | 0.4717                  | 2.5%  |  |

| in/data-out path<br>delay (ns)* | $\checkmark$         | $\checkmark$ |              | 1.2520                | 1.1745                | 0.8473                  | 32.3% |  |

|                                 | $\checkmark$         | $\checkmark$ | $\checkmark$ | 1.5986                | 1.5578                | 1.0882                  | 31.9% |  |

| Power (w) @ 500M                |                      | Cell Power   |              | 5.165e-04             | 7.707e-04             | 5.129e-04               | 0.7%  |  |

|                                 |                      | Net Power    |              | 1.112e-03             | 9.907e-04             | 9.833e-04               | 11.6% |  |

|                                 | Total                |              |              | 1.629e-03             | 1.761e-03             | 1.496e-03               | 8.2%  |  |

\* For mux shifters, this is  $d[0] \rightarrow z[0]$  while for demux shifter it is  $d[0] \rightarrow z[1]$

### Outline

- Motivation

- Previous Work

- Approaches

- Fanout-Splitting

- Cell order optimization by ILP

- Conclusions and future work

### Conclusions & Future Work

- We have proposed

- Fanout-splitting design

- ILP based layout optimization

- Future directions

- Extend the fanout splitting idea and ILP formulation to ternary shifter

- Try alternative hierarchical approach to tackle the ILP complexity issue

### The End

Thank you!