### The Future of Semiconductor Industry – A Foundry's Perspective –

Dr. F.C. Tseng Vice Chairman TSMC January 24, 2008

Outline

- Semiconductor Market Outlook

- Challenges and Solutions

- Economic

- Technology

- Summary

Proprietary

& Confidential

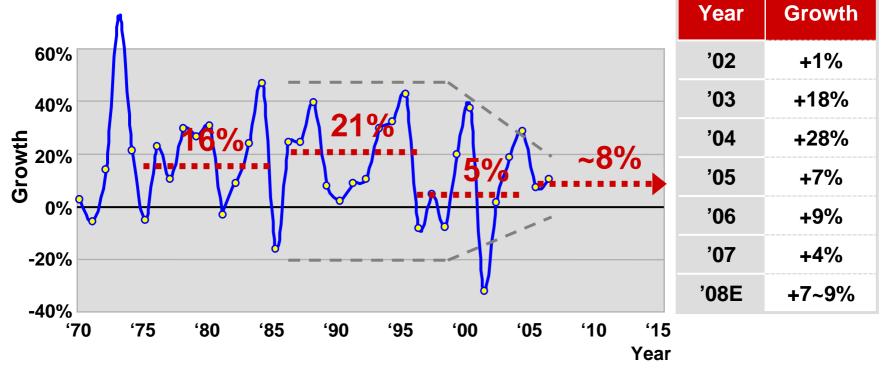

#### Semiconductor Market Will Continue to Grow

The Proven Path to Success

#### **Steady Market Expansion**

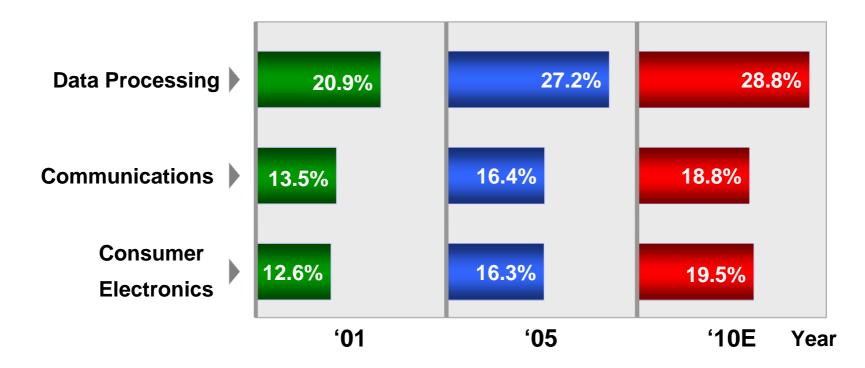

#### Increasing semiconductor penetration in electronics

Source: WSTS, IC Insights, TSMC estimates

The Proven Path to Success

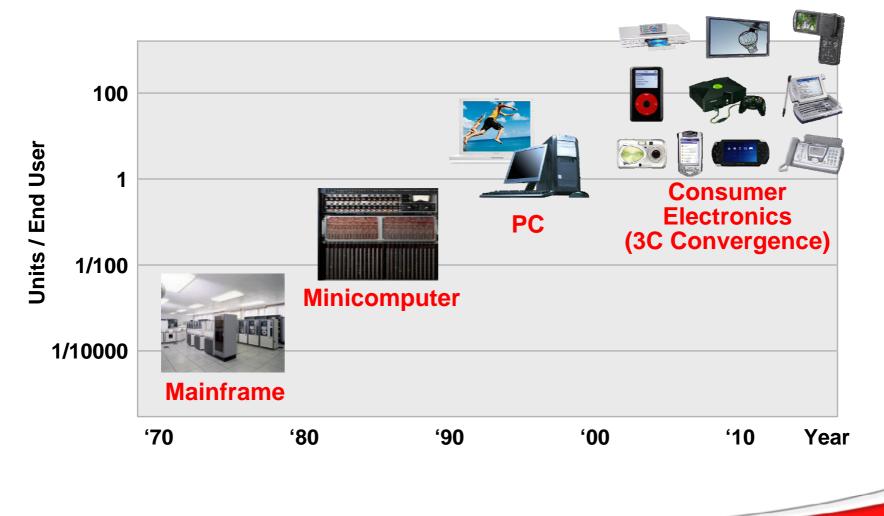

### Increasing Semiconductor Content in Systems

#### - Functionalities and performance

& Confidential

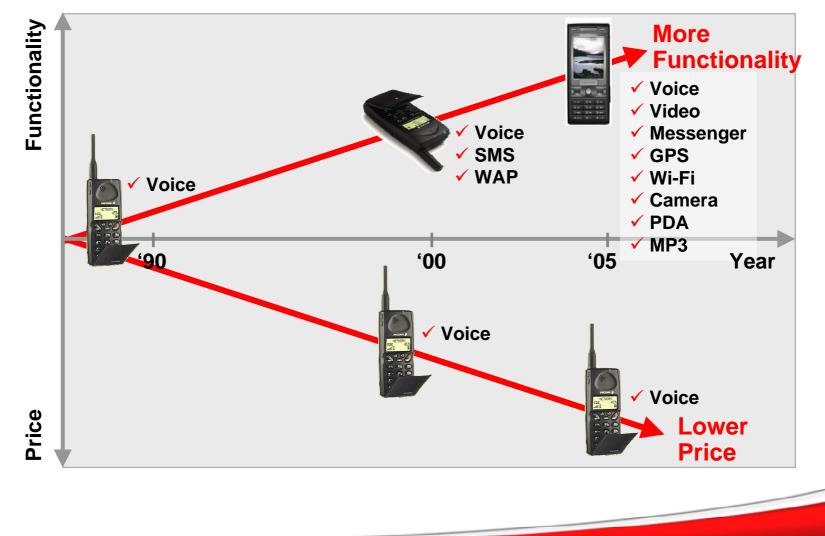

#### **New Applications as Growth Drivers**

6

The Proven Path to Success

#### Demand from High-end and Low-end Markets

The Proven Path to Success

& Confidential

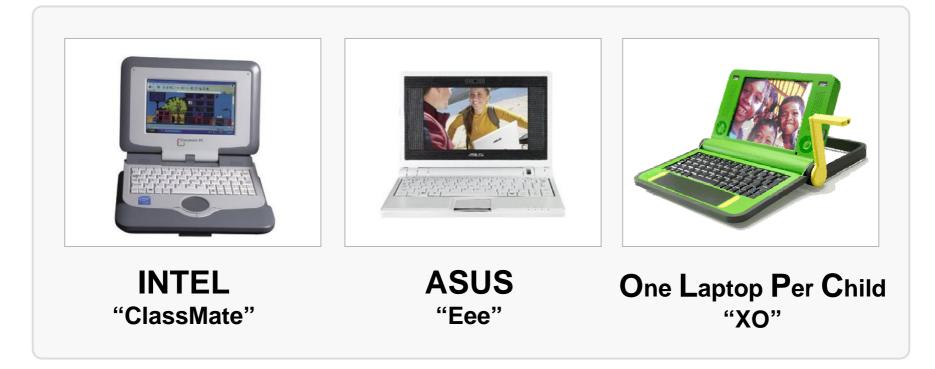

# In Search of A PC to Serve "The Next Billion"

#### • The low-cost PCs for the developing nations:

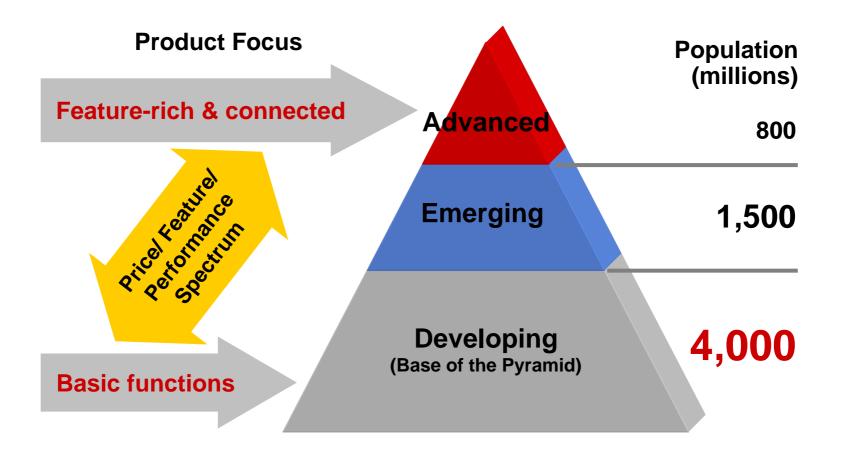

#### **Growth Opportunities are Global**

Source: "The fortune at the bottom of the pyramid" by C. K. Prahalad, and IMF

The Proven Path to Success

& Confidential

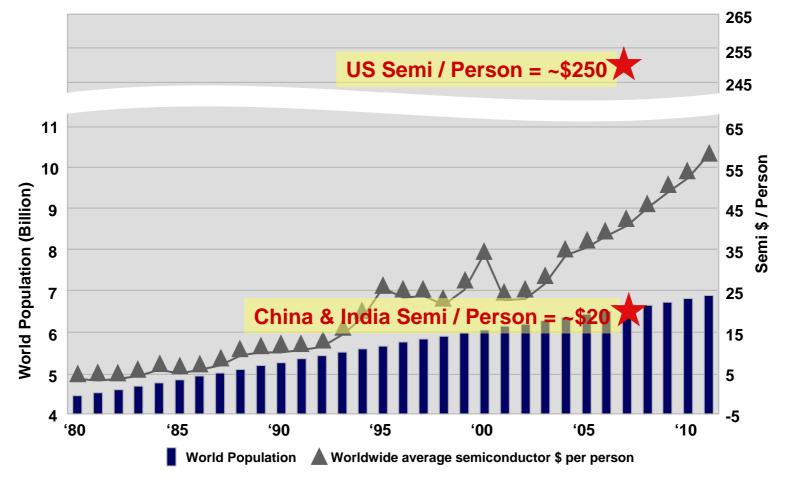

#### **Plenty of Opportunity Ahead**

Source: US Census Bureau; IC-Insights; TSMC estimates

10

#### Outline

Semiconductor Market Outlook

- Challenges and Solutions

- Economic

- Technology

- Summary

#### Challenges

#### **Economic**

- 1. Huge CapEx

- 2. ROI Risk Process

- 3. ROI Risk Product

#### **Technology**

4. Nanometer Manufacturing

The Proven Path to Success

- 5. Nanometer Design

- 6. Design Complexity

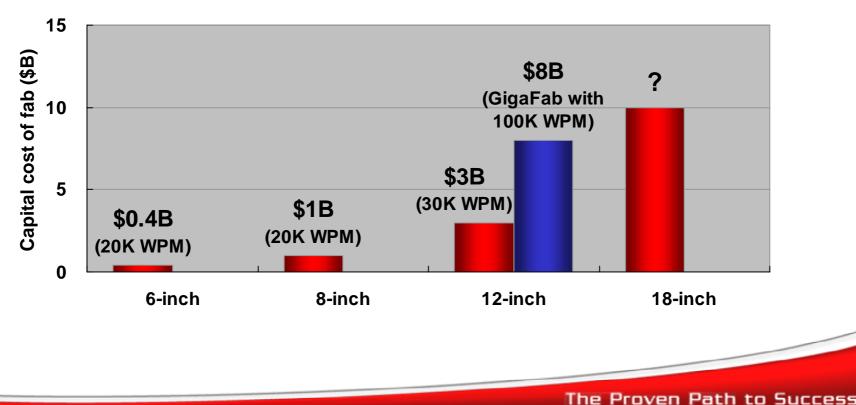

#### 1. Huge CapEx

- Capital expenditure for constructing a new fab is rapidly increasing

- Major factor for financing and future profit

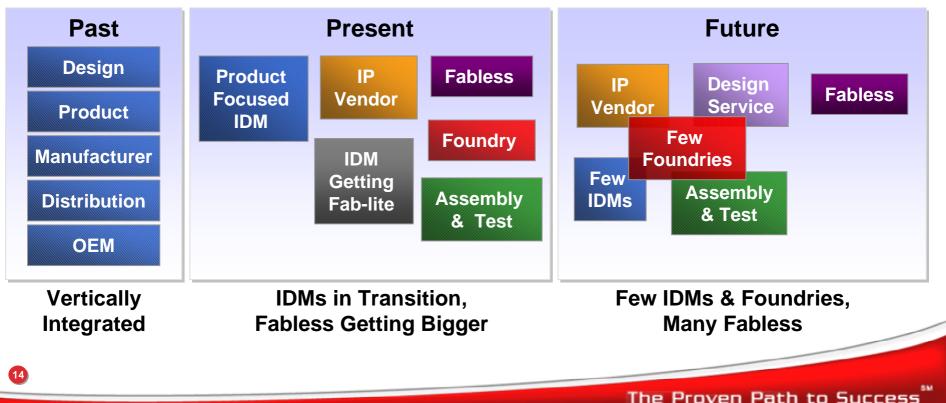

### Solution – Foundry Based Business Model

- Many IDMs are changing to either fab-lite of fabless

- A wide variety of consolidation and collaboration are inevitable

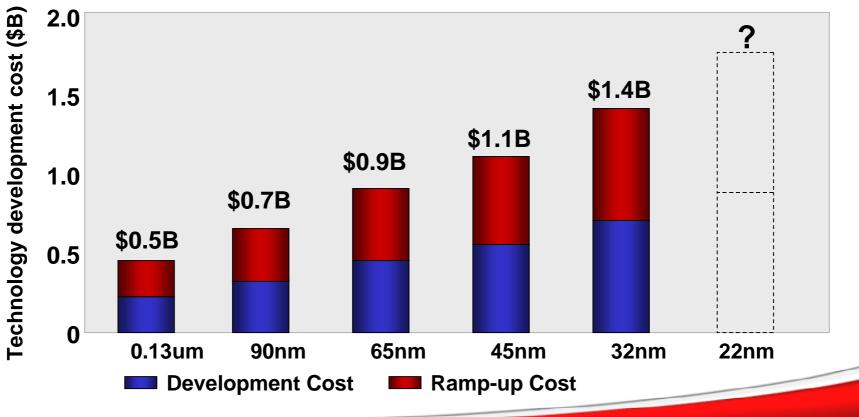

### 2. ROI Risk – Process

- Incremental challenges in developing next generation processes

- Process technology development costs are continuously increasing

The Proven Path to Success

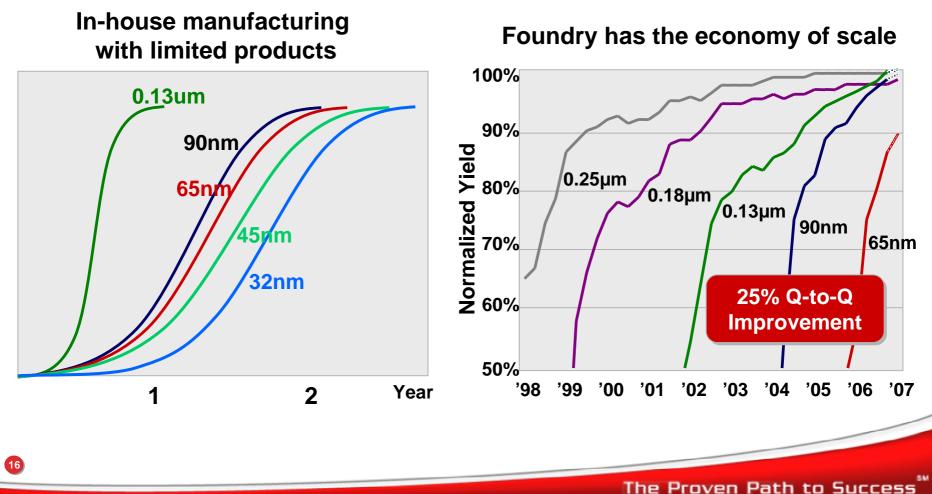

#### 2. ROI Risk – Process (Cont'd)

• Yield ramp-up requires significant time and investment

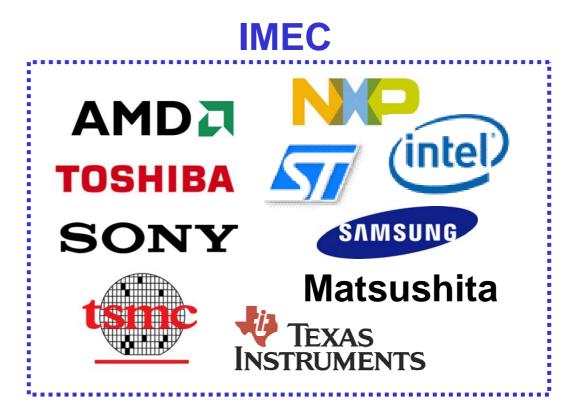

### **Solution I – Technology Alliance**

Collaboration is required to overcame ever – increasing financial as well as technical challenges

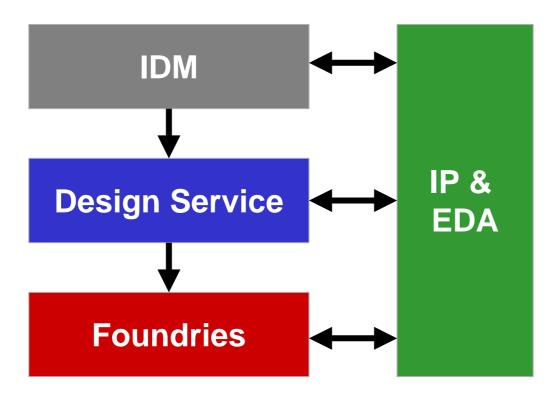

### Solution II – Collaboration among Foundry, IP/EDA Vendors, And Design Service Suppliers

Standardization of IP & EDA tools

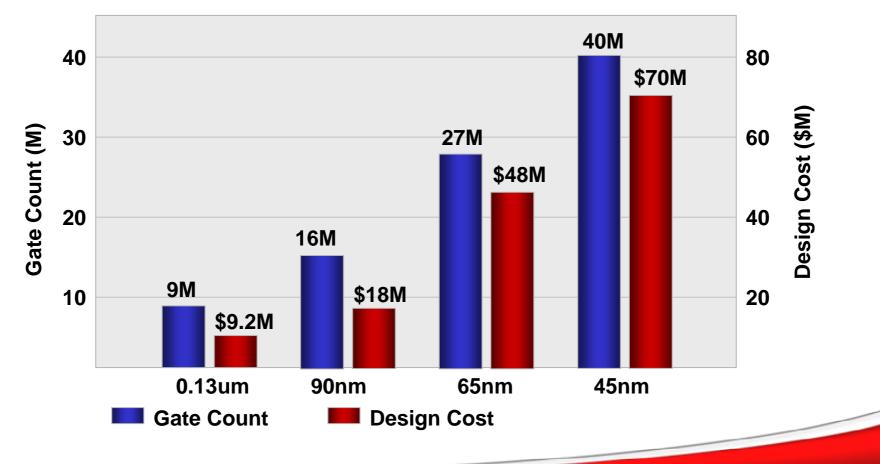

#### 3. ROI Risks - Product

- Design complexity and cost increase rapidly

- Short time to market

19

The Proven Path to Success

#### **Solution - Product**

Optimal system partition

#### • Foundry

- Design Infrastructure

- ♦ SPICE

- PDK

- Foundation IP

- Prototyping

- Cybershuttle

- MLM

#### Minimize the product risk and NRE

### 4. Nanometer Manufacturing

- New materials and device structure

- High-K gate dielectric

- Metal gate

- 3D FINFET

- Low-K Interconnect

- New EDA solutions for technology modeling and advanced lithography

The Proven Path to Success

& Confidentia

### Solution – Technology Modeling / Advanced Lithography

- Modeling in new material, 3D device and equipment / topography

- Polarization, OPC, double exposure and mask 3D effects

# Collaborate with EDA vendors to achieve seamless interfacing hierarchy

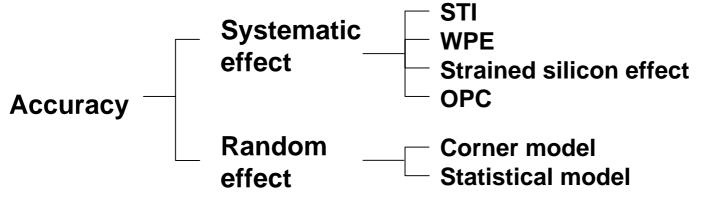

#### 5. Design for Nanometer

- Increasing systematic / parameter / random yield loss due to process variation

- Physical patterning effects, open and short, etc.

- Chemical and mechanical impact, planarity, antenna effect, and via opens, etc.

- Timing, signal integrity and voltage drop

- Increasing leakage (quantity, source, variation)

### **Solution – Accurate DFM**

- Model & simulation-based approach for physical and electrical DFM that represents Manufacturing accurately

- Physical DFM

- Identify hot spot, fix it and improve geometric yield.

- Electrical DFM

- ◆ Identify electrical performance deviation, correct it and improve paramedic yield

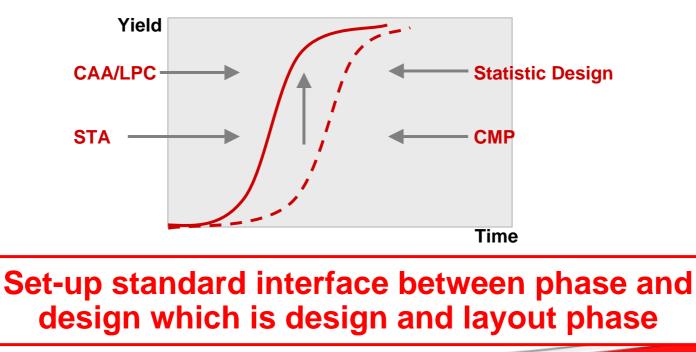

#### **Solution – DFM Ecosystem**

- Foundry to set up DFM ecosystem and open license DUF to reduce cost

- Standard interface between the design infrastructure and manufacturing

| Example: |                                |                 |      |                            |

|----------|--------------------------------|-----------------|------|----------------------------|

|          | EDA Alliance                   | IP/Lib Alliance | TSMC | TSMC/GUC +<br>DCA Alliance |

|          | TSMC DFM Compliance Initiative |                 |      |                            |

|          |                                |                 |      |                            |

The Proven Path to Success

### **Solution – Low Power**

- Aggressively develop integrated low power solutions for dynamic and leakage power reduction

- Low power process

- Advanced processes with ELK/XLK die-electric: lower voltage, smaller geometry and capacitance for dynamic power reduction

- HK/MG and gate CD bias for leakage reduction

- Low power IP

- Full set of low power foundation IP, dual power SRAM

- Low power design Reference Flow

- Silicon proven design methodologies for TSMC IP and processes

- Voltage scaling (DVFS, AVS), power gating with data retention

- Low power design automation enabling

Develop vertically integrated solution from system-level to layout and to process

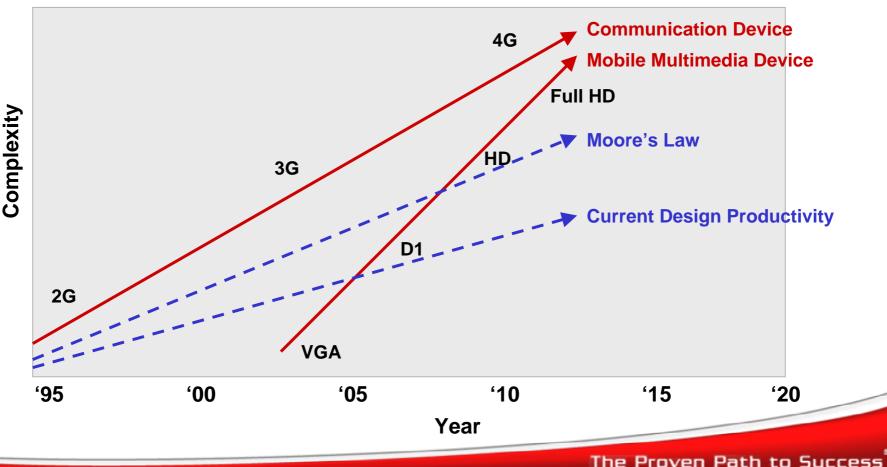

#### 6. Design Complexity

Increased design complexity causes longer time-tomarket and requires significant effort for verification and software design

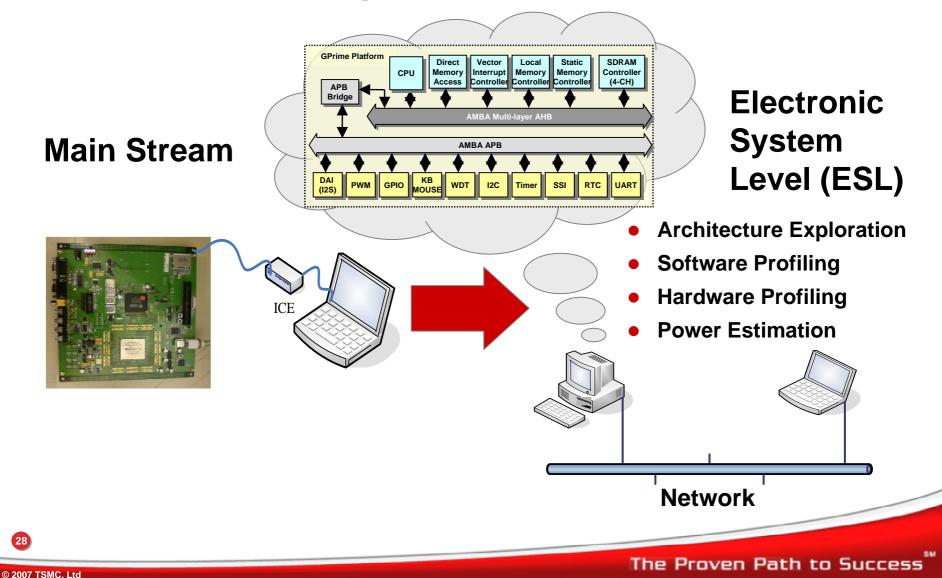

### Main Stream vs. ESL Co-development Environment

#### Solution – ESL

- New ESL design technology to address design complexity, and to provide massively parallel heterogeneous MPSOC design

- SIP and 3D packaging can integrate large capacity memory and analog circuit with short time to market and low cost

- Develop product with chip and PC board at same time to improve success rate

#### **Collaborate with EDA vendors**

#### Summary

- Semiconductor market growth will continue but moderate

- Future growth opportunities will be global but bifurcate

- High ROI risks in design, fab, and technology could be alleviated with the integrated foundry model

- Close collaboration is required between EDA vendors, foundry and IC companies

## **Thank You**

www.tsmc.com

The Proven Path to Success