## A Wireless Real-Time On-Chip Bus Trace System

#### Shusuke Kawai, Takayuki Ikari, \*Yutaka Takikawa, Hiroki Ishikuro, and Tadahiro Kuroda

Keio University \*Renesas Design Corp.

Shusuke Kawai (1/7)

# Background

- Inductive coupling technique

- ♦ High speed, low power

- Communication range: 10um-1mm

- New applications: Wireless detachable interface

- ♦ Real time on chip bus trace system

- High speed memory access

- Wireless connector

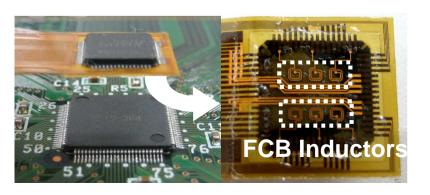

- Real time on chip bus trace system

Probe (FCB)

Target LSI

Shusuke Kawai (2/7)

## **Problems**

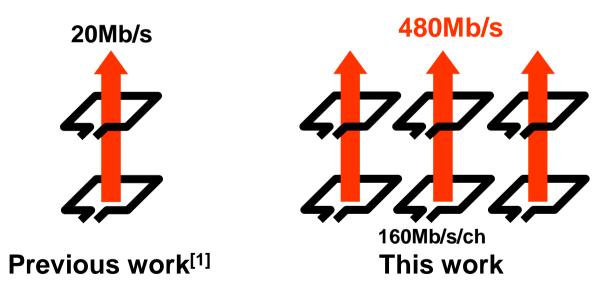

Real time on chip bus trace system

several hundred Mb/s

High speed communication by arranging channels in parallel

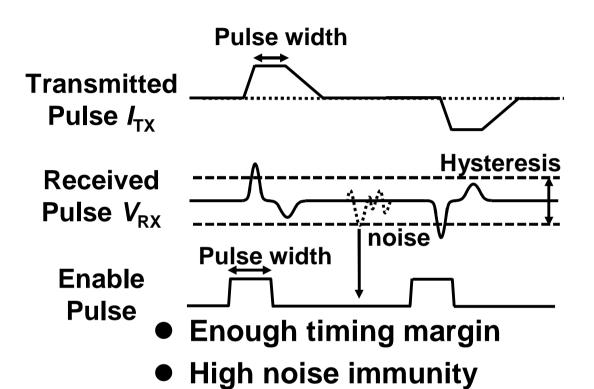

• Crosstalk and timing margin must be considered

[1]H.Ishikuro *et al.*, *ISSCC*, 2007.

### **Quasi-Synchronous System**

|                | Sync | Async | Quasi-Sync |

|----------------|------|-------|------------|

| Noise immunity | 0    | ×     | 0          |

| Timing margin  | X    | 0     | 0          |

Shusuke Kawai (4/7)

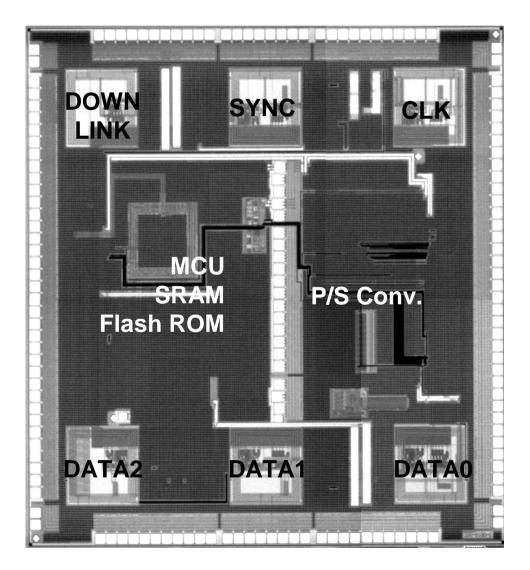

## **Die Photo**

- Technology

- ♦ 0.25µm CMOS

- Standard digital process

- Die size

- ◆ 4mm x 4mm

Shusuke Kawai (5/7)

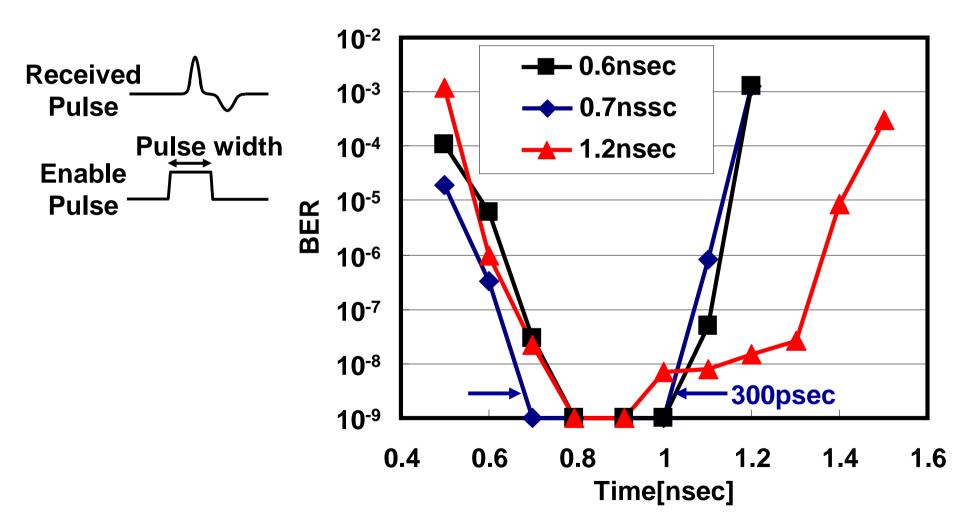

#### **BER measurement**

# Conclusion

- Wireless real-time on-chip bus trace system is developed using a 0.25µm CMOS process

- The quasi-synchronous system is proposed to obtain an enough timing margin and high noise immunity

- Timing margin of 300psec is obtained with a BER less than 10<sup>-9</sup>