## Vertical Interconnects Squeezing in Symmetric 3D Mesh Network-on-Chip

Cheng Liu, Lei Zhang, Yinhe Han, Xiaowei Li Key Lab of Computer System and Architecture Institute of Computing Technology Chinese Academy of Sciences

## Outline

- Background

- Motivation

- TSV Squeezing Scheme

- Experiments

- Conclusion

## Background

- 3D Technique

- Low latency

- Heterogeneous integration

- Manufacture challenge

- Network-on-Chip

- High bandwidth

- Excellent scalability

- Large p2p latency

- 3D Network-on-Chip

- High bandwidth

- Low latency

- Excellent scalability

- Heterogeneous integration

- Manufacture challenge

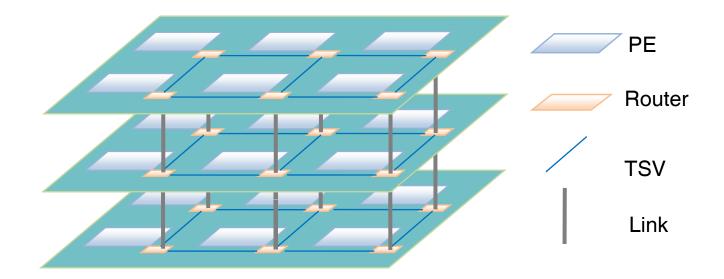

#### **3D Network-on-Chip**

- 3D Mesh-bus hybrid architecture

- True 3D fabric architecture

- 3D symmetric architecture

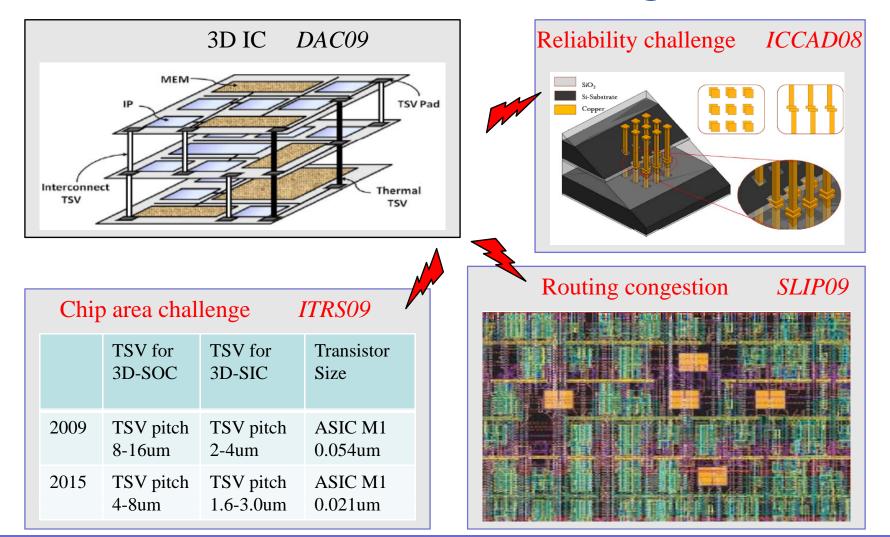

#### **3D IC Manufacture Challenges**

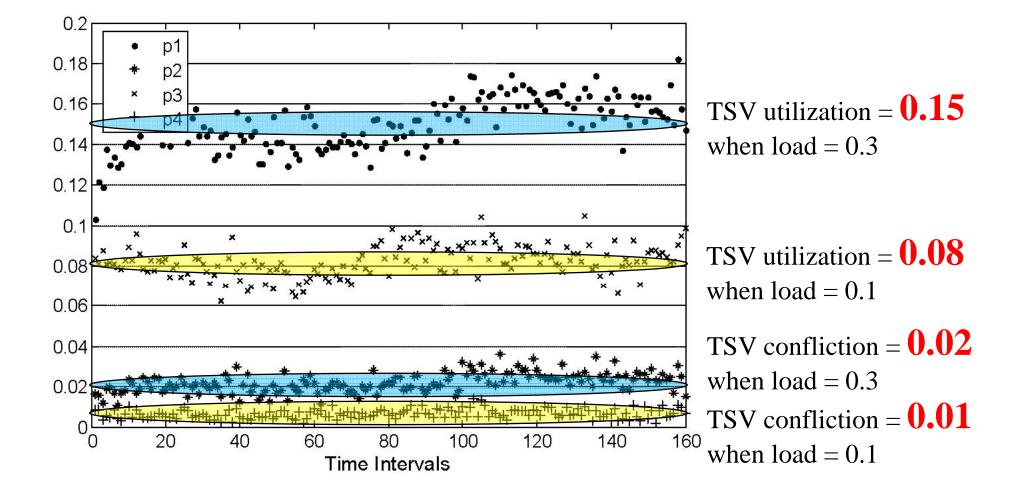

#### **Observation**

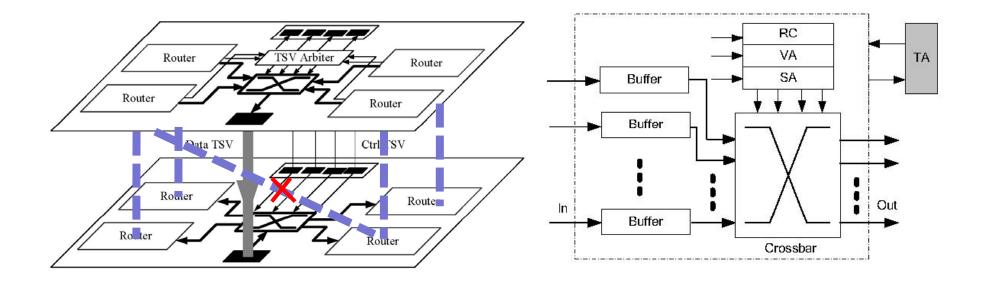

### **TSV Squeezing Scheme**

Squeezing Scheme with 4:1

**Router Modification**

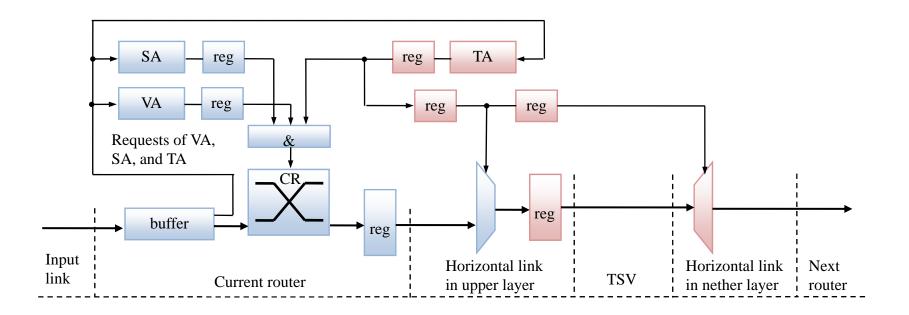

#### **Router Microarchitecture**

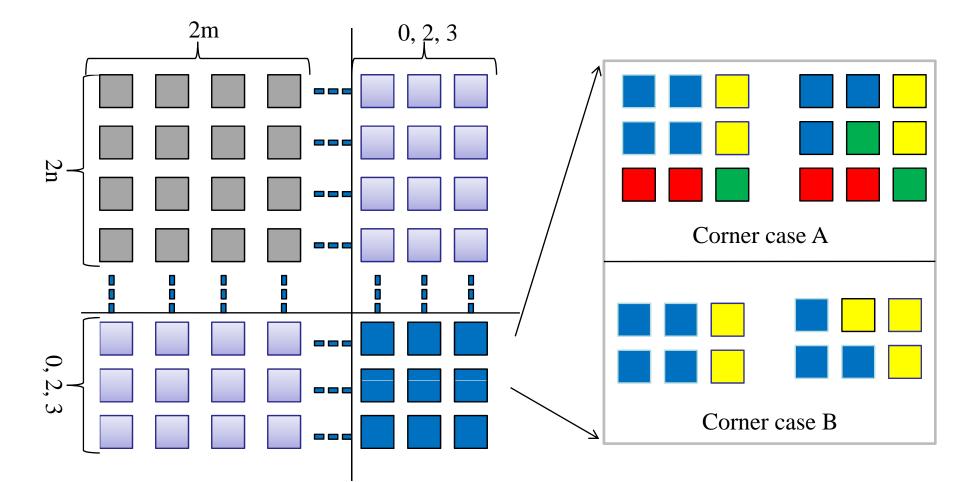

#### **NoC Organization for TSV Squeezing**

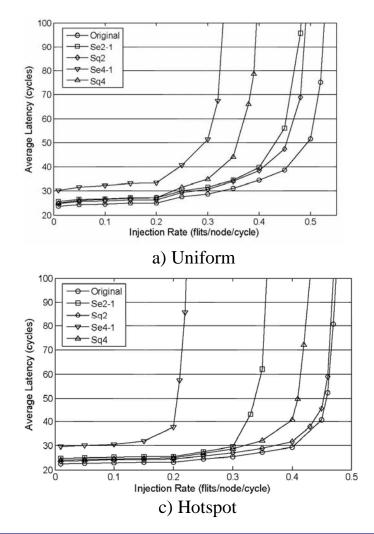

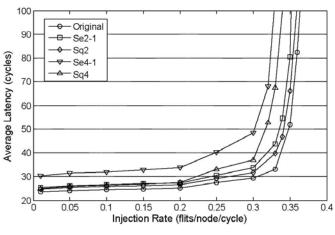

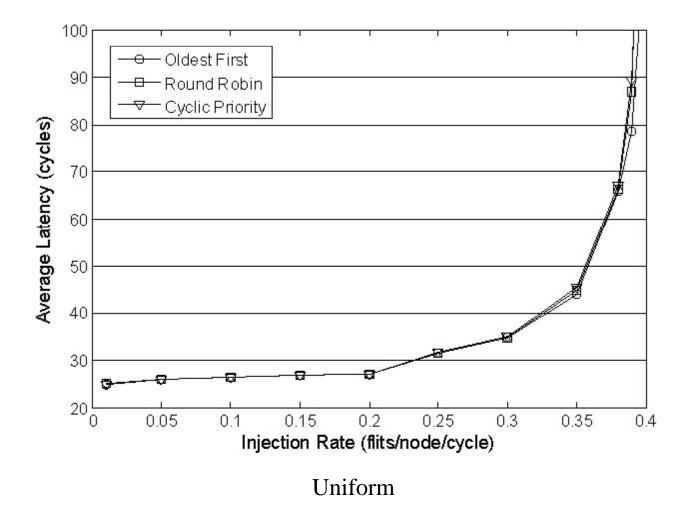

**Experiment set up** Topology: 4x4x2 Mesh Buffer: 2VC x 8flits per port Router: Two-staged Pipeline Routing: DOR (XYZ)

#### **Arbitration Analysis**

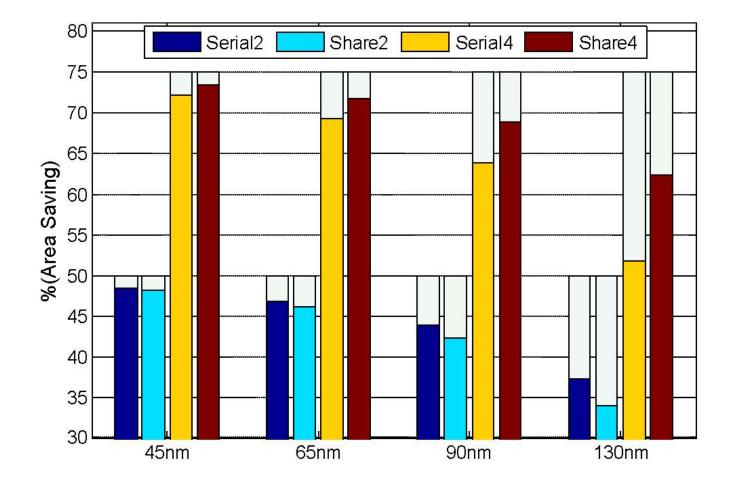

#### **Area Overhead**

## Conclusion

- Propose a TSV squeezing scheme according to the observation of TSV utilization

- Save more than 60% TSV footprint

- Less performance penalty including network latency especially zero-load latency, throughput compared with previous work

## **Questions?**

# **Thank You!**