### A Physical-Location-Aware Fault Redistribution for Maximum IR-Drop Reduction

Fu-Wei Chen, Shih-Liang Chen, Yung-Sheng Lin and TingTing Hwang

> National Tsing Hua University Department of Computer Science

# Outline

- Introduction

- Motivation

- Design Flow

- Experimental Results

- Conclusion

# Outline

#### Introduction

- Motivation

- Design Flow

- Experimental Results

- Conclusion

### Introduction

- IR-drop effect increases up to 16% during atspeed test as compared normal mode [N. Ahmed, ICCAD'06]

- Test vector designed to generate switching

- Test vector compression

- IR-drop  $\rightarrow$  Long path delay  $\rightarrow$  Delay fault

### **Previous Work**

- X-filling to reduce IR-drop [4,11,14,15]

- Reduce IR-drop effect in at-speed testing

- Depend on the number and characteristic of X-bit distribution

- Sensitization paths propagate through the same hot region

- X-identification to redistribute X-bit [10]

- Redistribute X-bits evenly in test vector

- Reduce IR-drop effect after X-filling

# Outline

- Introduction

- Motivation

- Design Flow

- Experimental Results

- Conclusion

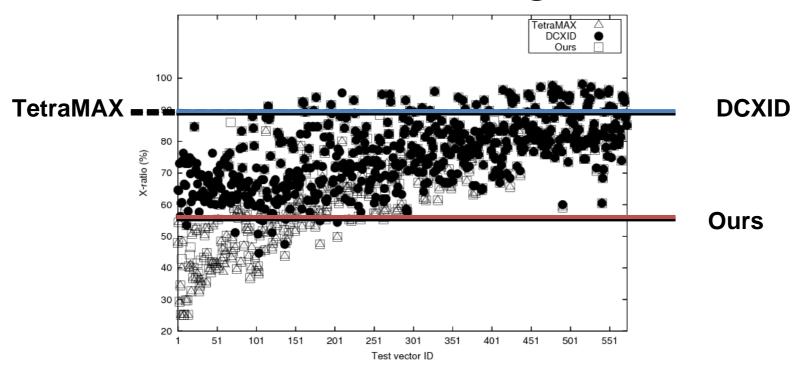

### Motivation: Even Distribution of X-Bit Is Not Enough

#### DCXID: Set *X*-bits evenly in all test vectors Ours: Set *X*-bits in hot region

# Outline

- Introduction

- Motivation

- Design Flow

- Experimental Results

- Conclusion

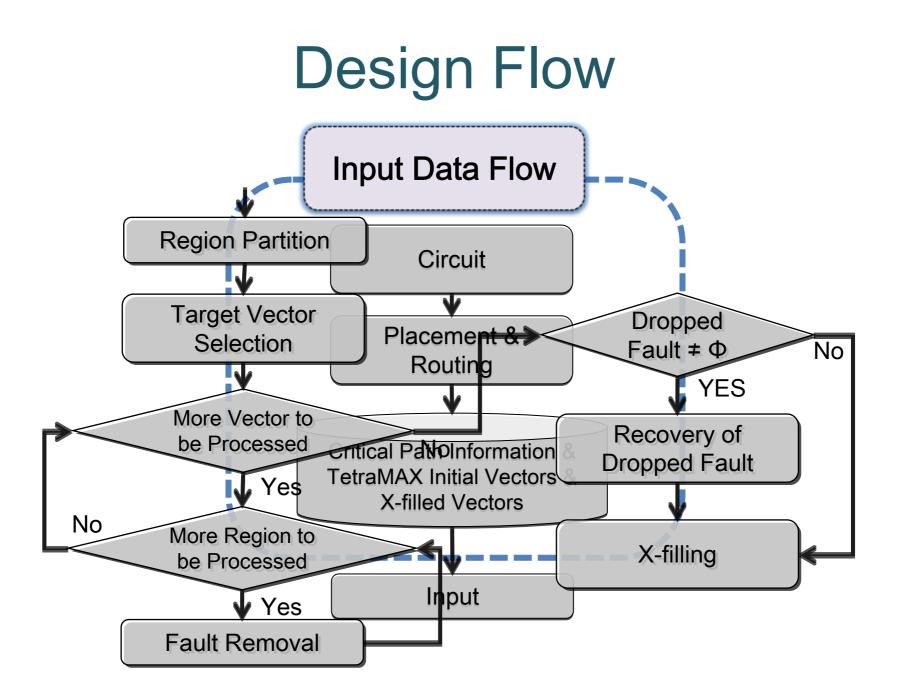

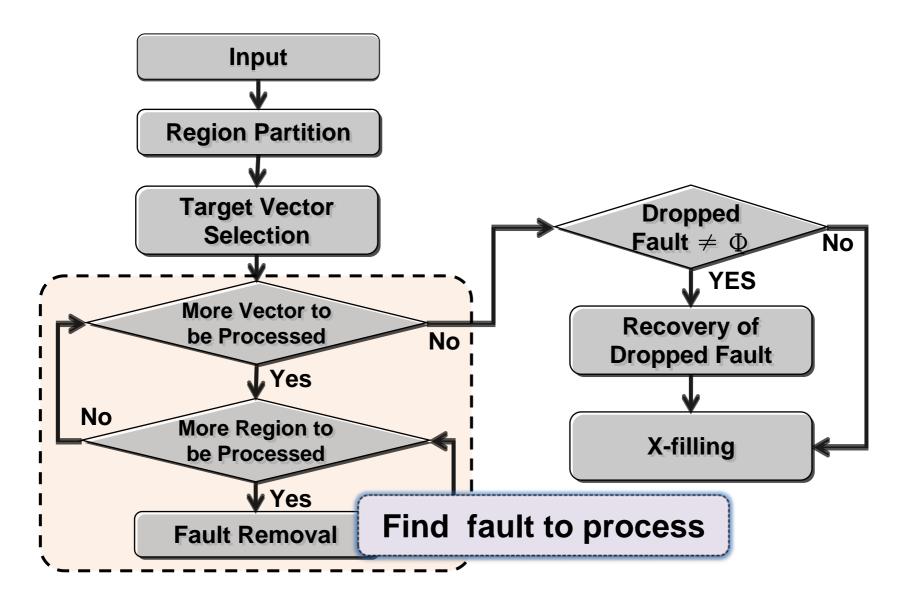

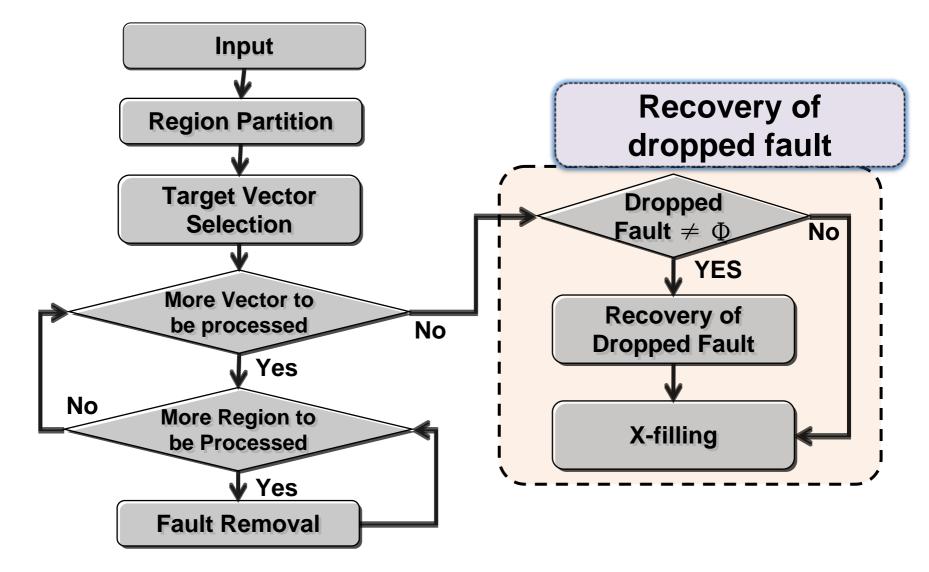

### **Design Flow**

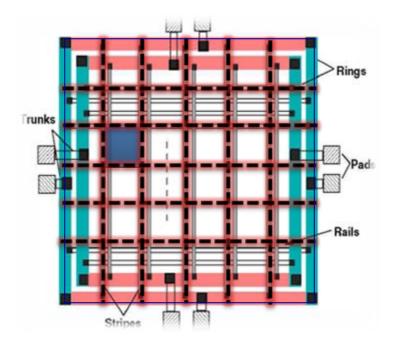

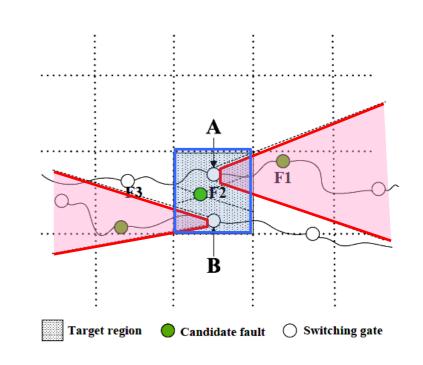

### **Region Partition**

- All components assigned to region

- Each region surrounded by stripes and rails

- The power rings placed around the core chip.

- Four VDD and VSS pads inserted to the respective rings

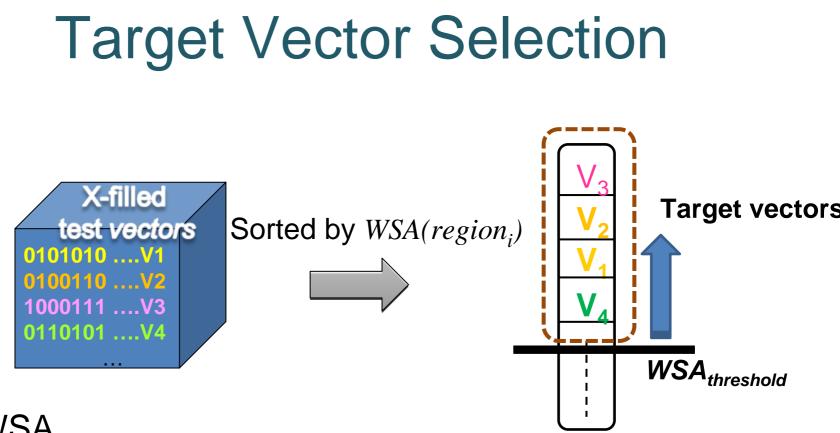

- WSA

- $WSA(region_i)$  represents **IR-drop effect** of each region

- $WSA(region_i) \propto Switching activity impact$

- $WSA(region_i)$  of target region is equal or larger than  $WSA_{threshold}$

### **Design Flow**

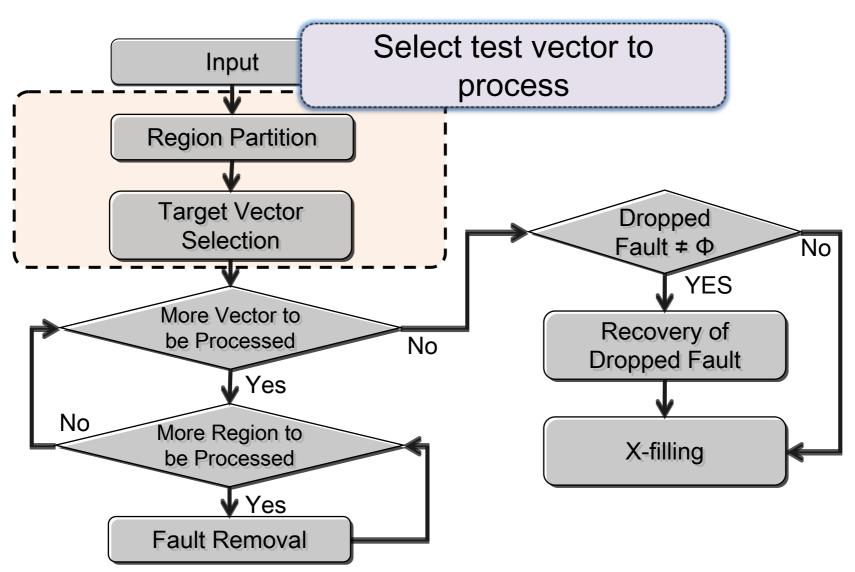

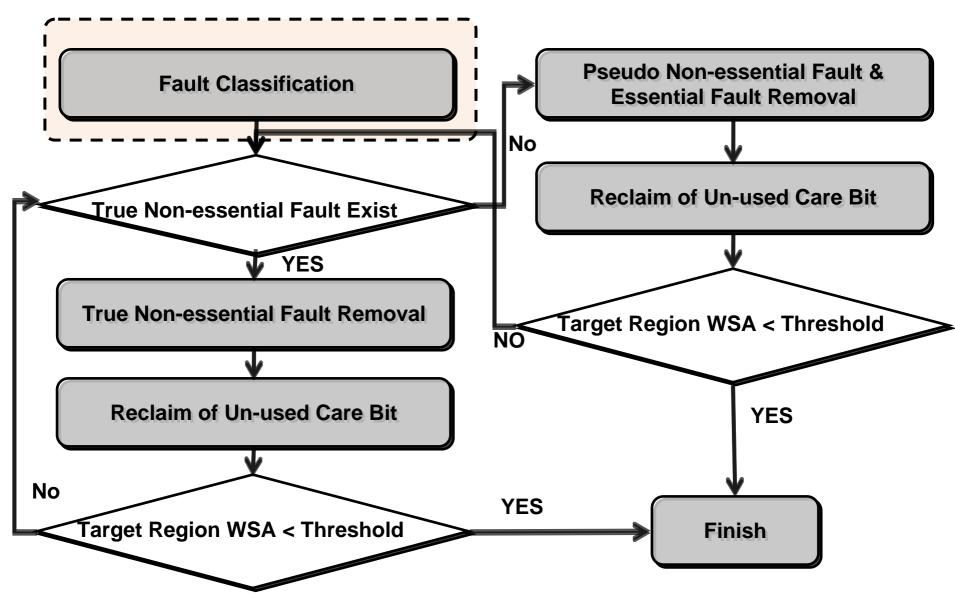

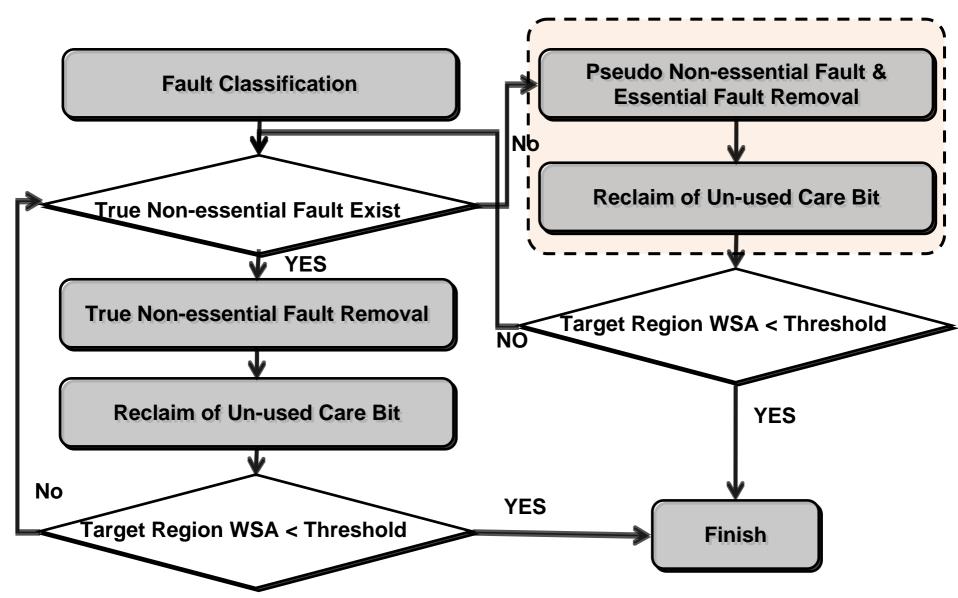

### **Fault Removal Flow**

### **Fault Removal Flow**

### Fault Removal

- Candidate fault

- Be in target region or propagate through target region (based on physical-location information)

- Impact of IR-drop

- WSA in target region

- Fault coverage

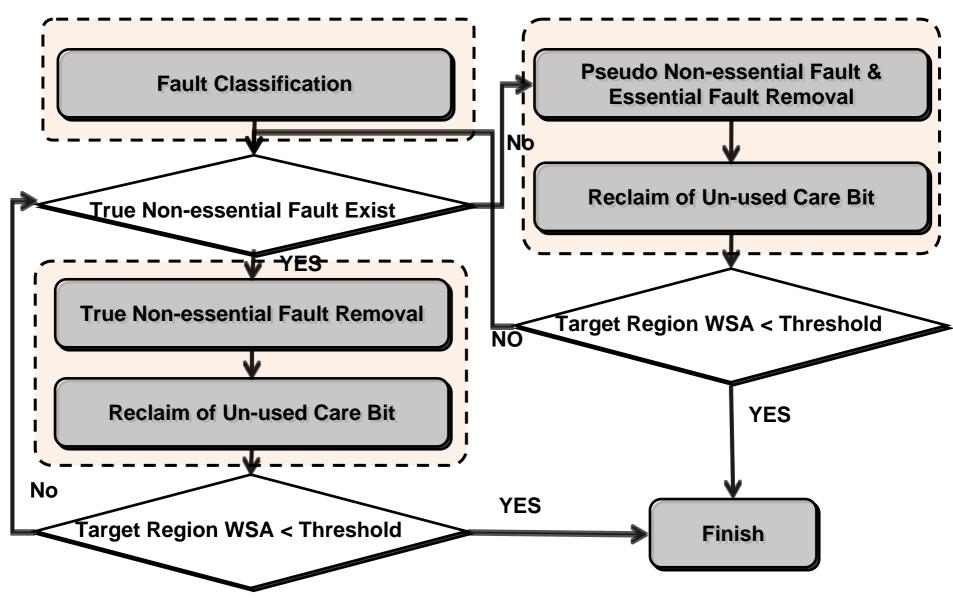

### Fault Classification

- Candidate fault classification

- Essential fault

- Fault coverage issue Covered by only one test vector

- Non-essential fault

- Covered by more than one test vector

### **Fault Classification**

### Candidate fault classification

- Essential fault

- Covered by only one test vector

- Non-essential fault

- Covered by more than one test vector

- True non-essential fault

- No other essential faults are on the propagation path

- Pseudo non-essential fault

- Essential fault is on the propagation path

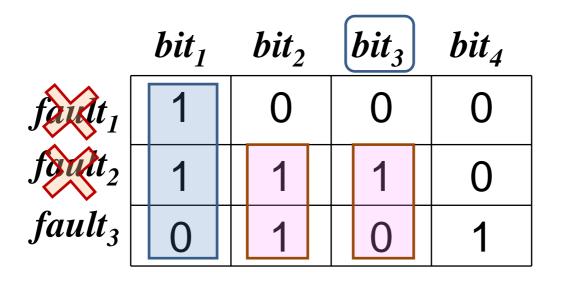

### Example of Non-essential Fault Classification

• Construct fault table for each test vector

|                    | bit <sub>1</sub> | bit <sub>2</sub> | bit <sub>3</sub> | bit <sub>4</sub> |                                    |

|--------------------|------------------|------------------|------------------|------------------|------------------------------------|

| fault <sub>1</sub> | 1                | 0                | 1                | 0                | care-bits <sub>1</sub> :{ 1, 3}    |

| fault <sub>2</sub> | 1                | 1                | 1                | 0                | care-bits <sub>2</sub> :{ 1, 2, 3} |

| fault <sub>3</sub> | 0                | 1                | 0                | 1                | care-bits <sub>3</sub> :{ 2, 4}    |

essential fault : fault<sub>1</sub> non-essential fault : fault<sub>2</sub> and fault<sub>3</sub>

$care - bit_3 \cap care - bit_1 = \Phi$   $care - bit_2 \cap care - bit_1 = \{1\} \neq \Phi$  Frue non-essential fault Frue non-essential fault

### **Fault Removal Flow**

### **True Non-essential Fault Removal**

- Remove true non-essential fault to reduce WSA

- Removal\_gain(target fault) = R\_WSA x #detectable\_vector

- *R\_WSA*: the reduction of *WSA* in region after removal *target fault*

- #detectable\_vector: the number of test vector that covers this target fault

- Remove *target fault* with maximum *Removal\_gain* until no true non-essential fault or *WSA* is less than threshold

### **Reclaim Un-used Care Bit**

$fault_1$  is to be removed  $\implies fault_2$  will be removed

Reclaim un-used care-bit  $bit_3$  to X-bit

### **Fault Removal Flow**

### Pseudo Non-essential Fault & Essential Fault Removal

• Reduction of *WSA* by setting care-bit to *X*

- Gain function:

$$bit\_gain(cb) = \frac{R\_WSA}{\# fault}$$

- *R\_WSA* : the reduction of *WSA* in region after setting the care-bit, *cb*, to *X*

- #fault : the number of removed fault if cb sets to X

- Set one care-bit to X-bit with maximum bit\_gain

### **Design Flow**

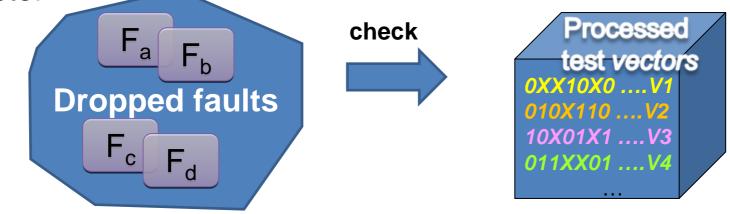

# **Recovery of Dropped Fault**

- After essential & pseudo non-essential fault removal is performed

- Dropped fault  $\rightarrow$  Fault coverage

- Check if any test vector can cover a dropped fault without violating IR-drop constraint

- Care-bits of the dropped fault are consistent with test vector

# Outline

- Introduction

- Motivation

- Design Flow

- Experimental Results

- Conclusion

### **Experimental Setup**

- Benchmark: ITC'99

- Technology library: TSMC 90 nm

- Synthesis tool: Synopsys Design Compiler

- APR tool: SoC Encounter(SoCE)

- ATPG tool: TetraMAX

- IR-drop Simulator: RedHawk

### **Results of X-filling**

|   | Circuit | Random-filled |        | PB-based X-filling[4] |       |        |       |  |

|---|---------|---------------|--------|-----------------------|-------|--------|-------|--|

|   | Name    | MAX.          | Avg.   | MAX.                  | (%)   | Avg.   | (%)   |  |

| C | b14     | 5.66          | 0.798  | 5.66                  | 0.00  | 0.6805 | 14.72 |  |

|   | b15     | 3.17          | 0.12   | 2.87                  | 9.30  | 0.1078 | 10.14 |  |

|   | b17     | 4.32          | 0.1158 | 3.88                  | 10.24 | 0.1039 | 10.24 |  |

|   | b18     | 4.1           | 0.1151 | 3.67                  | 11.82 | 0.1023 | 12.50 |  |

|   | b19     | 3.81          | 0.1208 | 3.52                  | 10.08 | 0.1048 | 15.27 |  |

| ( | b20     | 5.13          | 0.5132 | 4.98                  | 3.01  | 0.4581 | 10.75 |  |

|   | b21     | 7.81          | 0.4389 | 7.71                  | 1.29  | 0.3907 | 10.99 |  |

|   | b22     | 5.49          | 0.699  | 5.45                  | 0.72  | 0.6157 | 11.92 |  |

- Improvements of MAX. WSA are not significant (at most 3.01%)

- Select b14, b20, b21 and b22 as difficult circuits

### Comparison of Maximum WSA for Difficult Circuits

| Circuit | MA       | X. WSA |      | Improvement(%) |       | Overhead |

|---------|----------|--------|------|----------------|-------|----------|

| Name    | TetraMAX | DCXID  | Ours | DCXID          | Ours  | #DF(%)   |

| b14     | 5.66     | 5.66   | 5.08 | 0.00           | 10.40 | 64(0.24) |

| b20     | 4.98     | 4.85   | 4.42 | 2.51           | 11.18 | 11(0.02) |

| b21     | 7.71     | 7.71   | 6.75 | 0.00           | 12.38 | 15(0.02) |

| b22     | 5.45     | 5.35   | 4.98 | 1.97           | 8.73  | 18(0.01) |

|         |          |        |      | 1.12           | 10.67 |          |

- Comparison for maximum for each difficult circuit

- Maximum *WSA* reduction of our method is better than DCXID in difficult circuits

- #DF: the number of dropped faults

### Comparison of Maximum IR-drop for Difficult Circuits

| Circuit | MAX      | K. IR-drop ( | Improvement (%) |       |       |

|---------|----------|--------------|-----------------|-------|-------|

| Name    | TetraMAX | DCXID        | Ours            | DCXID | Ours  |

| b14     | 314.3    | 312.7        | 284.3           | 0.5   | 9.56  |

| b20     | 156.1    | 152.2        | 139.6           | 2.5   | 10.60 |

| b21     | 110.6    | 109.0        | 97.4            | 1.45  | 11.89 |

| b22     | 209.3    | 205.8        | 191.7           | 1.68  | 8.46  |

| avg.    |          |              |                 | 1.53  | 10.07 |

- Our method as compared with TetraMAX are 10.07% and 1.53%, respectively.

# Outline

- Introduction

- Motivation

- Design Flow

- Experimental Results

- Conclusion

### Conclusion

- A physical-location-aware X-identification method to redistribute faults

- An average of 8.54% more reduction of maximum IR-drop as compared to a previous work

### Thank you