FPGA Prototyping using Behavioral Synthesis for Improving Video Processing Algorithm and FHD TV SoC Design

### Masaru Takahashi

SoC Software Platform Division,

**Renesas Electronics Corporation**

January 28, 2011

# Outline

- Background and Issues

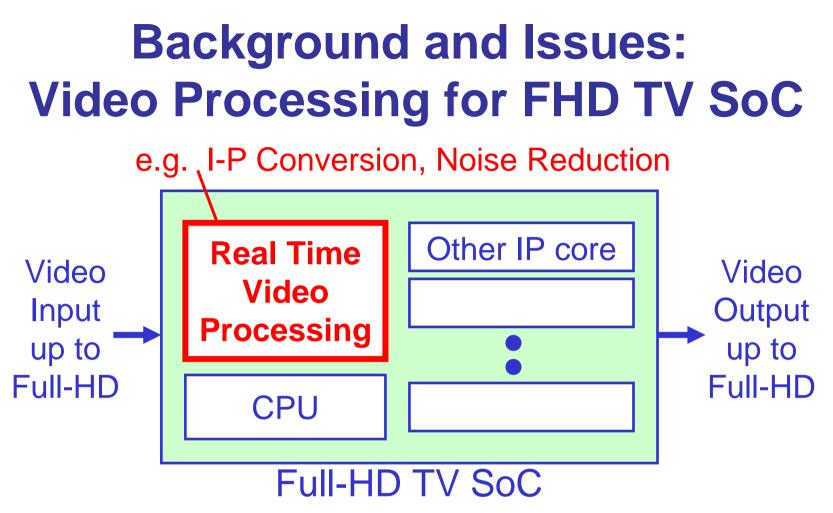

- Video Processing for FHD TV SoC

- Estimation System

- Conventional Design Flow

- Proposal Design Flow

- SystemC Description

- Results of Development

- Conclusion

- Picture Quality of SoC is affected by Video

Processing Algorithm

- Estimation and Improvement are necessary before Implementation

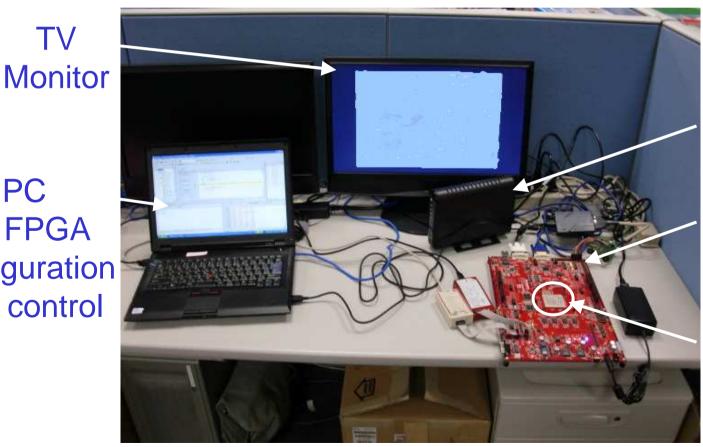

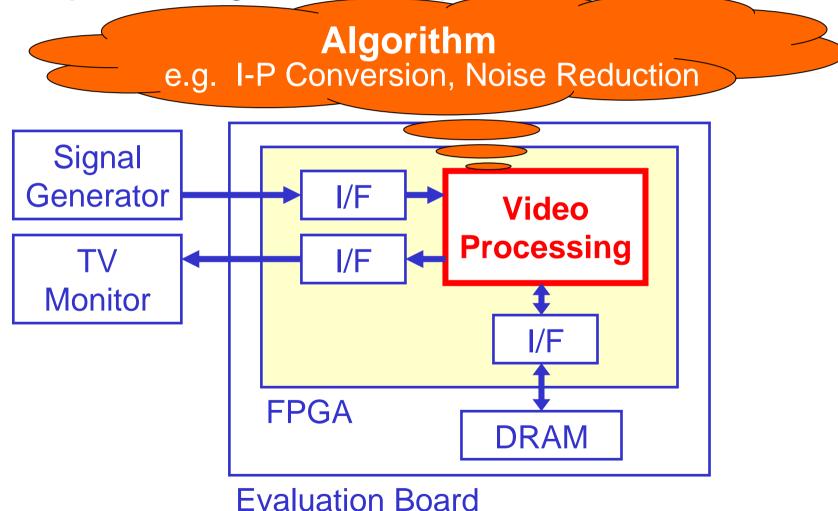

### **Background and Issues: Estimation System**

#### Example of Estimation System

Real Time Estimation by FPGA Prototyping

PC for FPGA configuration and control

TV

Signal Generator (HDD recorder)

**Evaluation Board**

**FPGA**

### Background and Issues: Estimation System

Improved Algorithm is implemented on FPGA

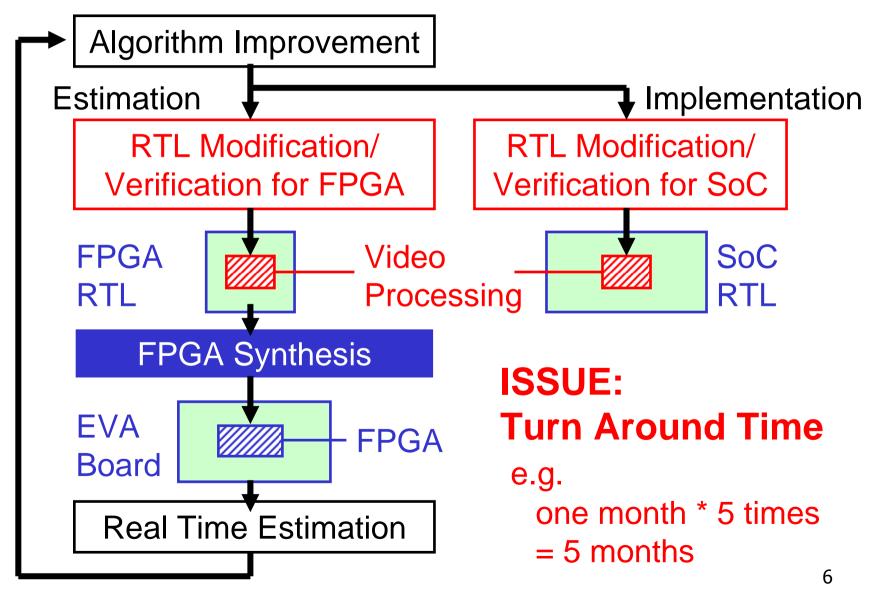

# Background and Issues: Conventional Design Flow

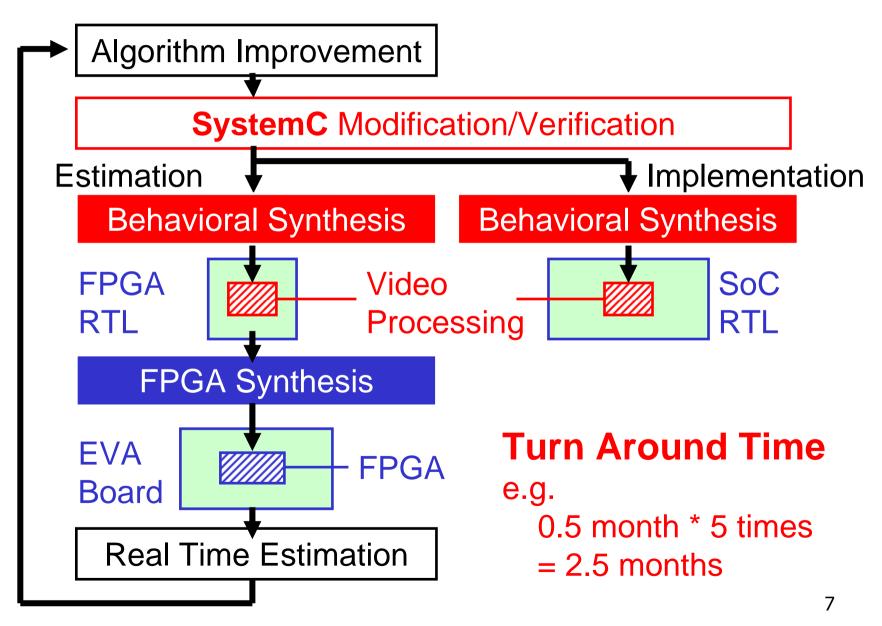

# **Proposal Design Flow**

# Proposal Design Flow: Summary

- Short Turn Around Time for Estimation

- SystemC and Behavioral Synthesis

- Updating FPGA is easy

- About half as long as without Behavioral Synthesis

- Easy to Implement on SoC

- Same SystemC, different Behavioral Synthesis

### Next: How to Describe **SystemC Description**

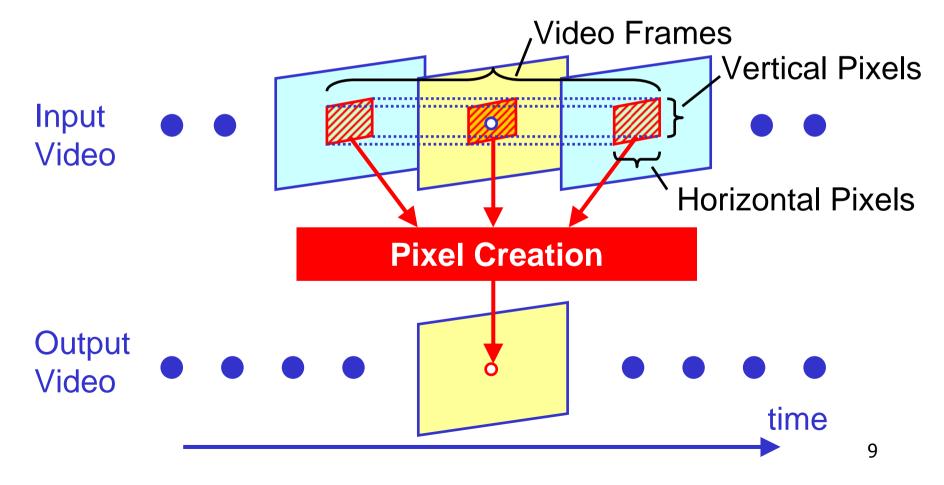

# SystemC Description: What kind of Processing?

For a pixel of Output Video, Spatiotemporally neighbor pixels of Input Video are referred.

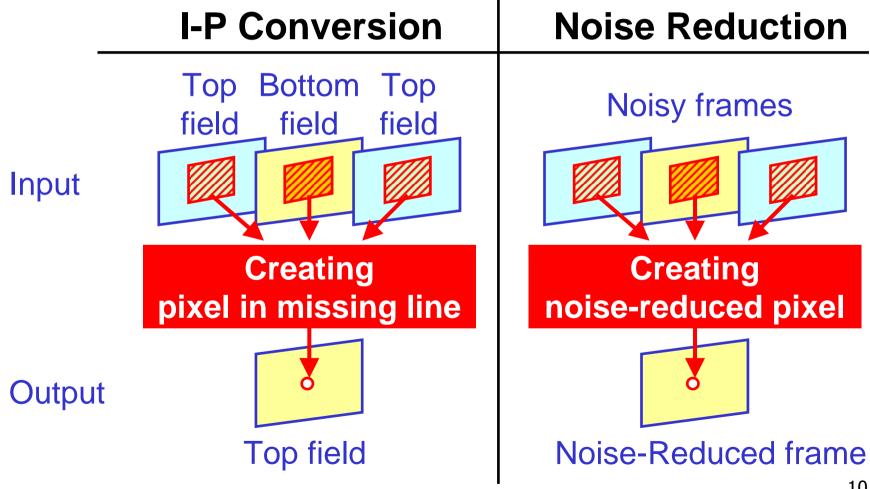

# SystemC Description: What kind of Processing?

#### Examples: Different Algorithm, Similar Interface

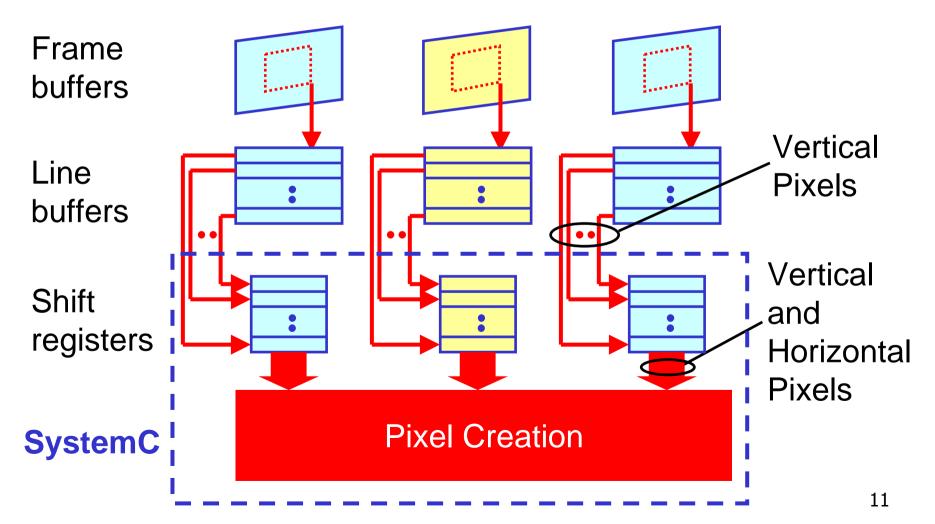

## SystemC Description: Data Input

Raster scan order

# SystemC Description : Example

Pipeline Synthesis is available

```

while(1){

for( f=0; f<3; f++ ){

for( y=0; y<H; y++ ){

for( x=W-1; x>0; x-- ){

Shift

shiftreg[f][y][x] = shiftreg[f][y][x-1];

Registers

shiftreg[f][y][0] = indata[f][y].read();

}

outsig = output_pixel( shiftreg ); //function - Main Algorithm

(Pipeline Synthesis)

outdata.write( outsig );

1 cycle per pixel

wait();

```

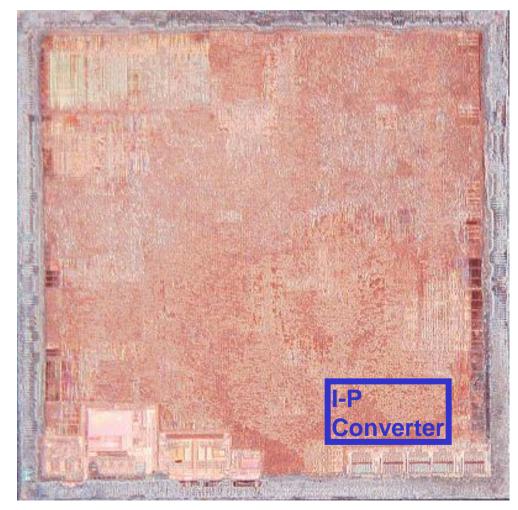

### Results of Development: Example of SoC

#### Interlace-Progressive Converter on FHD TV SoC

## Results of Development: Developed IP lists

#### Three designs have been developed

| Function                               | SystemC<br>Code | Development Period            |                        |               |                      |

|----------------------------------------|-----------------|-------------------------------|------------------------|---------------|----------------------|

|                                        |                 | Algorithm<br>Improve-<br>ment | IP<br>Develop-<br>ment | Gate<br>Count | SoC                  |

| Interlace-<br>Progressive<br>Converter | 13.5 klines     | 3 Months                      | 6 Months               | 785 kGates    | SH-Mobile MT1        |

| Cinema<br>Detection                    | 3.6 klines      | 3 Months                      | 4 Months               | 35 kGates     | Under<br>development |

| MPEG Block<br>Boundary<br>Detection    | 4.1 klines      | 3 Months                      | 1 Month                | 135 kGates    | Under<br>development |

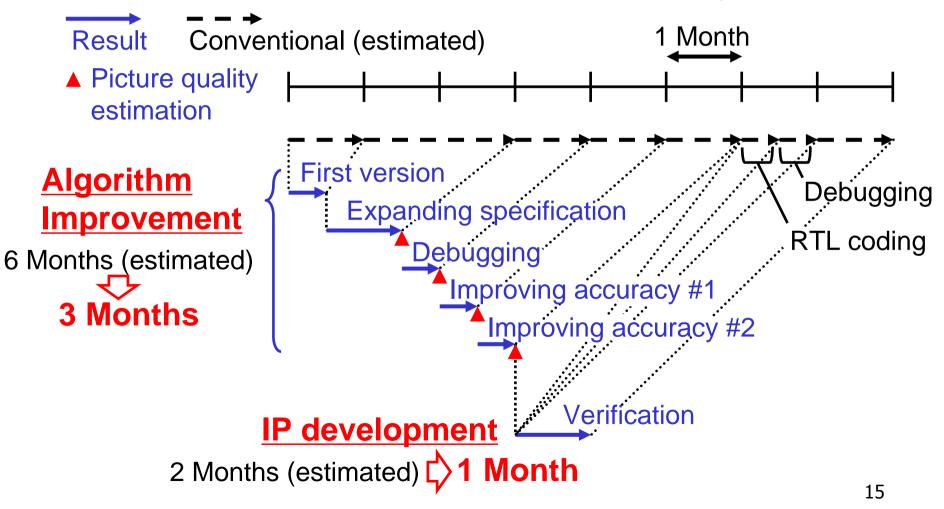

## Results of Development: Development Period

#### Detail schedule of MPEG block boundary detection

### Conclusion

- We provide New Design Flow of Video Processing Algorithm using Behavioral Synthesis.

- Turn Around Time is about half as long as that without Behavioral Synthesis

- Three designs have been developed using New Design Flow