# Optimizing Dynamic Mapping Techniques for On-Line NoC Test

Qiong Wu

University of Electronic Science and Technology of China

- Background

- Problem definition

- Testing-aware mapping algorithm(TAMA)

- Evaluation

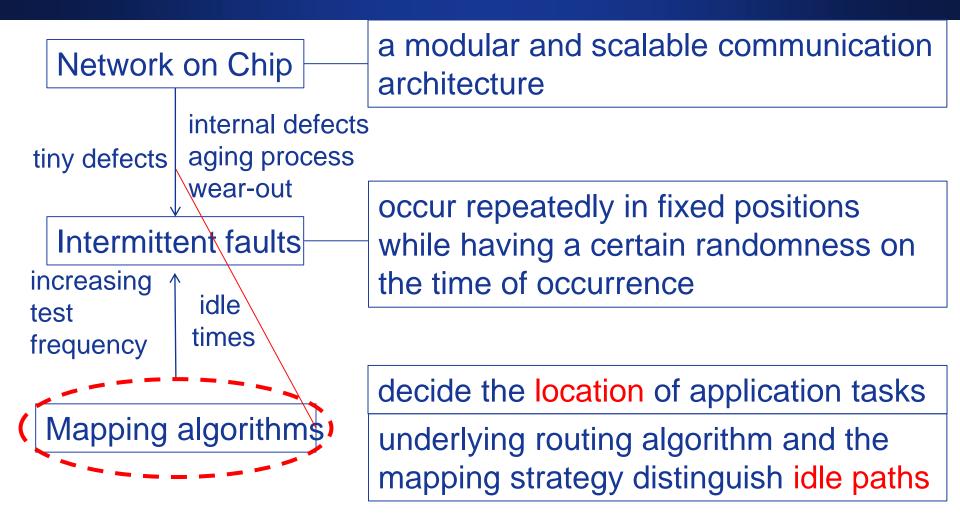

# **Background**

- Background

- Problem definition

- Testing-aware mapping algorithm(TAMA)

- Evaluation

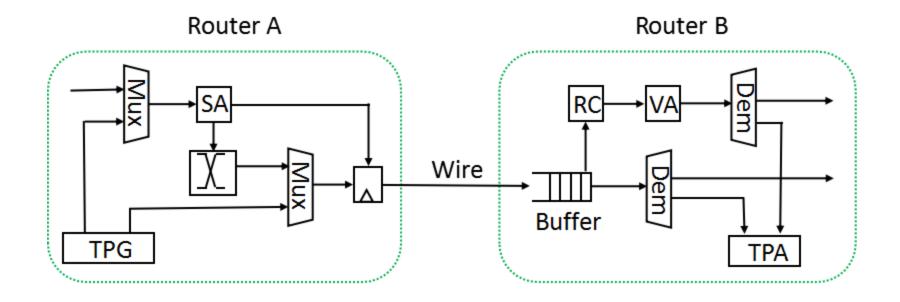

### **BIST Strucure**

#### A link/path test:

testing all the components between the TPG unit of one router to the TPA unit of the next router

## **Testing the Paths**

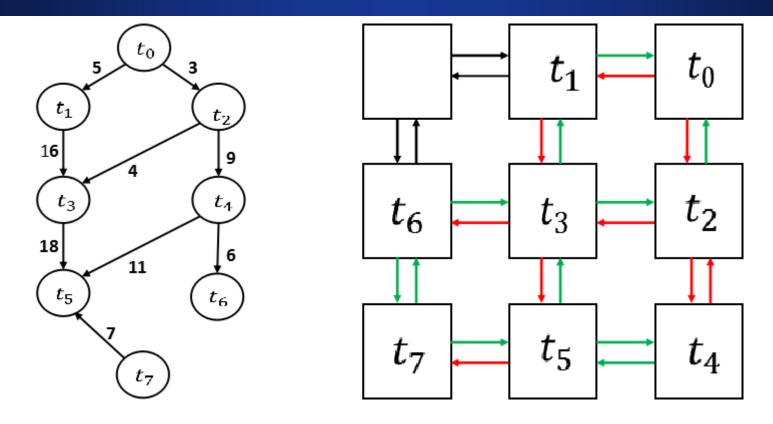

An application with 8 tasks and 9 edges running on NoC. We use the underlying XY routing to show the result of free (green) and occupied (red) paths.

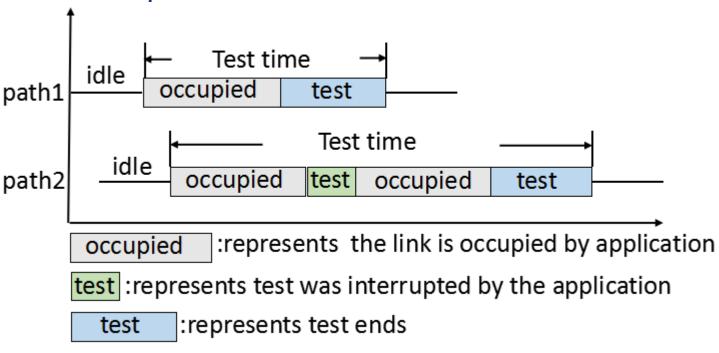

## On-the-field test strategy

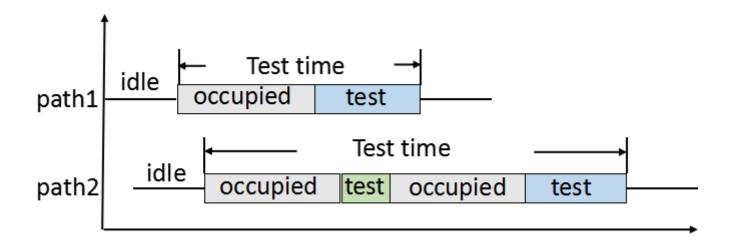

The path test time under two conditions.

The test start time; Identifying and testing the free paths; Handling the conflicting situation of test and mapping

# Reliability evaluation metrics

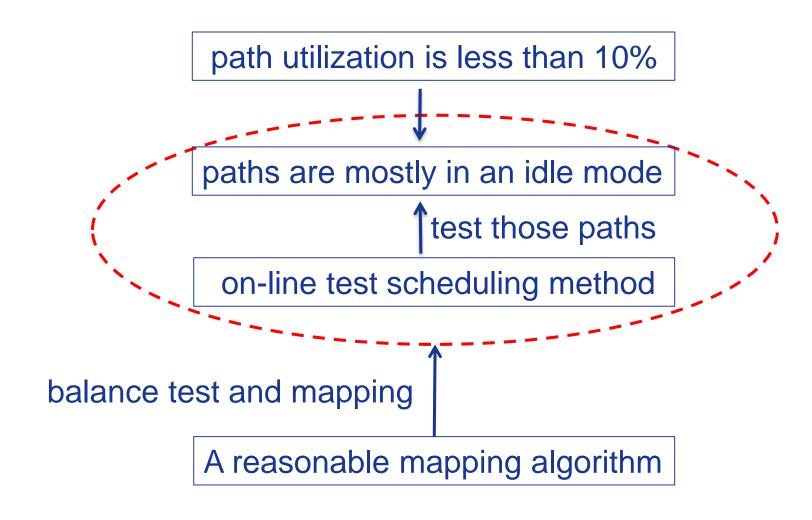

Define a reliability evaluation: average test time

Lower average test time means higher test frequency intermittent faults

- Background

- Problem definition

- Testing-aware mapping algorithm(TAMA)

- Evaluation

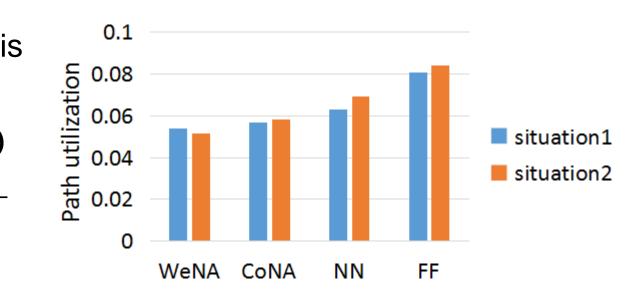

The link utilization is defined:

$$L_{utilization} = rac{\displaystyle\sum_{T_s}^{T_s} N_c(t)}{N_l * T_s}$$

$N_c$ : the number of utilized paths at each simulation cycle;

$N_l$ : the number of paths in the network;

$T_{\rm s}$ : the total simulation cycles.

there is a quest for a testing-aware mapping algorithm

mapping application

detecting intermittent faults

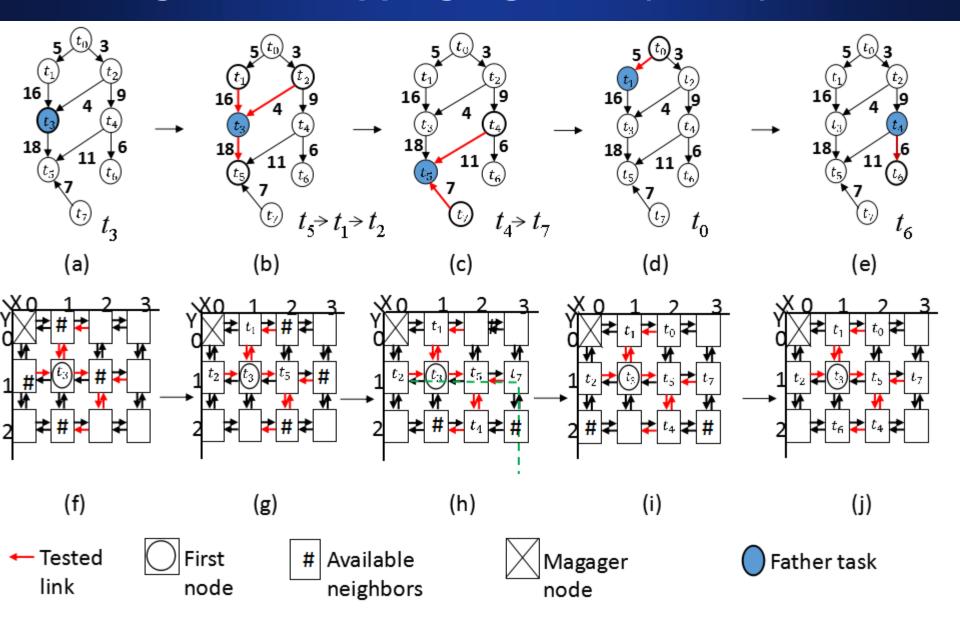

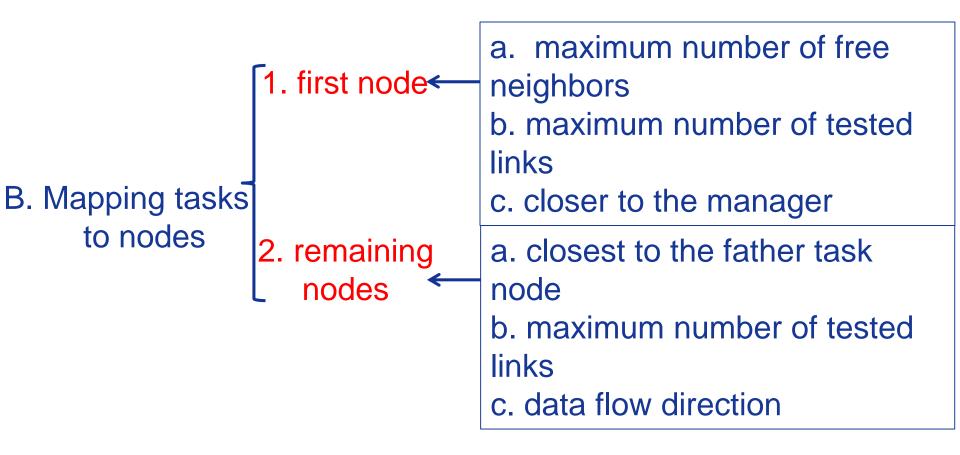

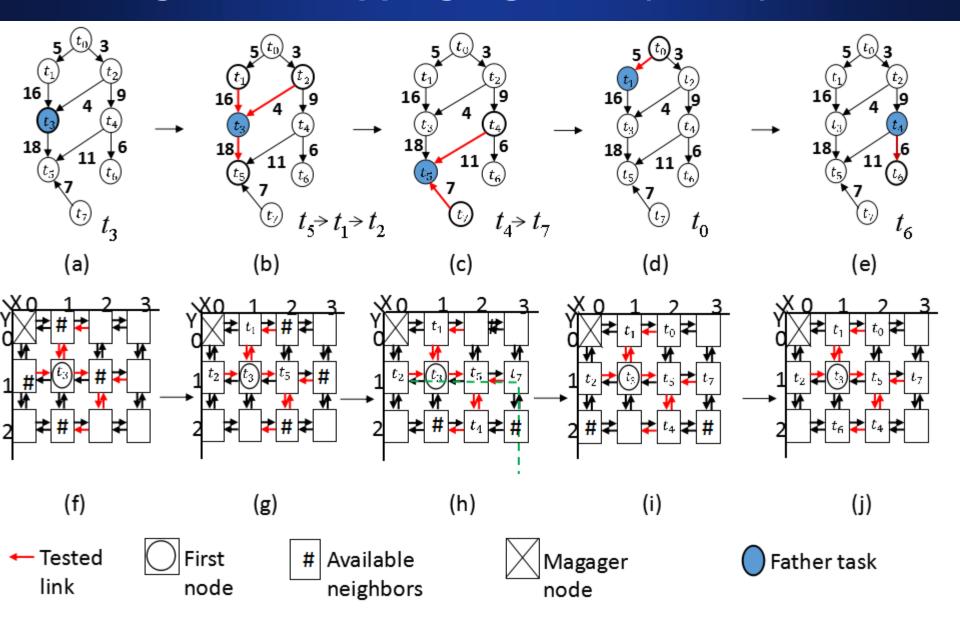

A. Sorting tasks

1: first task 🗲

the largest number of edges and communication volume

2: remaining tasks

the breadth-first traversal technique

- Background

- Problem definition

- Testing-aware mapping algorithm(TAMA)

- Evaluation

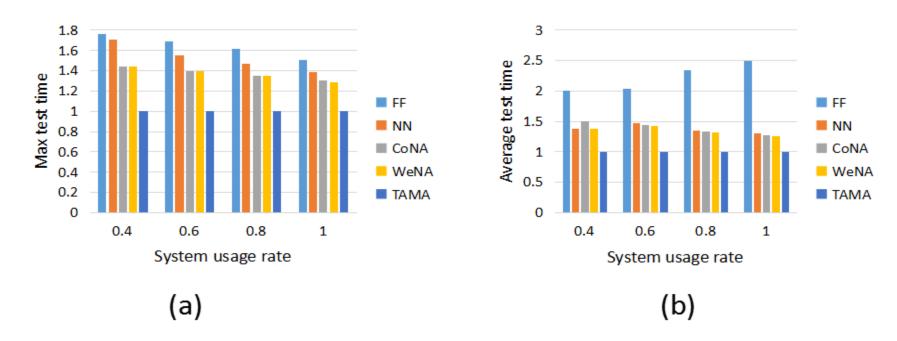

## **Maximum Test Time and Average Test Time**

Obviously decreases the maximum test time and average test time. The benefit of TAMA is more significant in lower usage rates

Testing paths at idle times

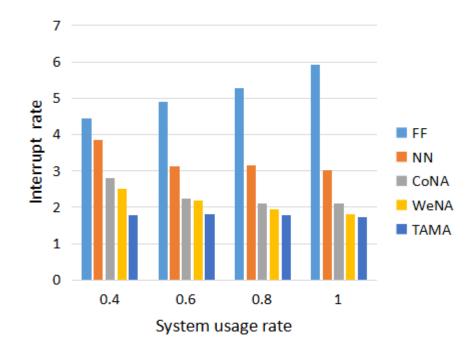

## Interrupted Test Rate

Interrupted test rate defined as:

$$T_{\mathrm{interrupted}} = \frac{T_c + T_{ic}}{T_c}$$

- The interrupted test rate is lowested in TAMA

- The fact that TAMA identifies the idle paths

$T_c$ : the total number of test path during the application mapping

$T_{ic}$ : the number of test that are interrupted due to the request of mapping

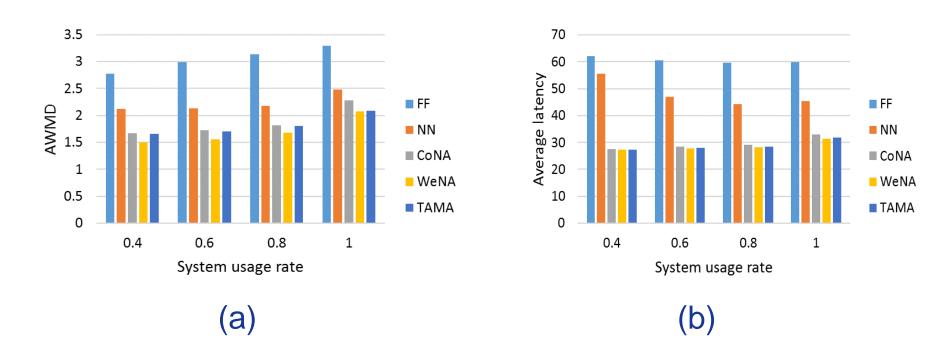

## **AWMD** and Average Latency

The AWMA of TAMA is always lower than the other methods. The average latency follows the same trend.

- Background

- Problem definition

- Testing-aware mapping algorithm(TAMA)

- Evaluation

# Conclusion

- ✓ A mapping algorithm to map application and detect intermittent faults over the NoC platform

- ✓ Experimental results showed that our mapping algorithm leads to improvements on the maximum test time, average test time and interrupt rate at no comprise of AWMD and average latency

# Thank You!

**ESYSim Tool QQ Group**