Department of Electrical Engineering, National Central University Electronic Design Automation Laboratory (EDA LAB)

### Performance-Preserved Analog Routing Methodology via Wire Load Reduction

Hao-Yu Chi<sup>1</sup>, Hwa-Yi Tseng<sup>1</sup>, Chien-Nan Jimmy Liu<sup>1</sup>, Hung-Ming Chen<sup>2</sup>

Dept. of Electrical Engineering, National Central University, Tao-Yuan City, Taiwan, ROC<sup>1</sup> Institute of Electronics, National Chiao Tung University, Hsin Chu, Taiwan, ROC<sup>2</sup>

- Introduction

- Problem Formulation

- Algorithm

- Experimental Results

- Conclusion

- Introduction

- Problem Formulation

- Algorithm

- Experimental Results

- Conclusion

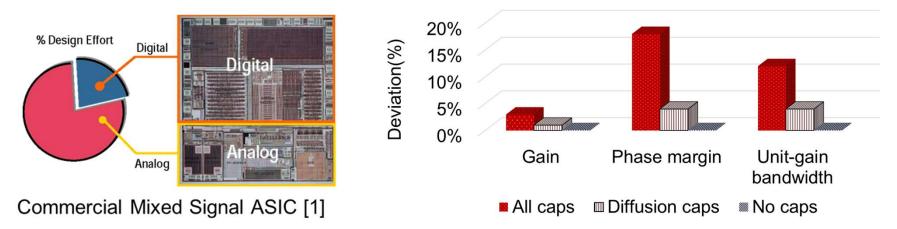

### Analog Design Flow

- Advance process makes analog components more sensitive

- Layout effects impact circuit performance [2]

#### Analog EDA tools need to be enhanced to deal with non-ideal effects

[1] R.A Rutenbar, "Design Automation for Analog: The Next Generation of Tool Challenges" 1<sup>st</sup> IBM Academy Conference on Analog Design, Technology, Modeling and Tools, IBM T.J. Waston Research Labs 2006

[2] A. Agatwal, et al., "Fast and accurate parasitic capacitance models for layout aware synthesis of analog circuits", in Proceedings DATE, 2000.

#### Analog Layout Design

- Impact circuit performance significantly

- Topology constraints

- Parasitic effects

- How to keep the performance during layout

- Placement

Topology constraint (ex. symmetry, proximity)

➢Routing

Parasitic effects(ex. wire length, via numbers)

Topology constraint (ex. symmetry)

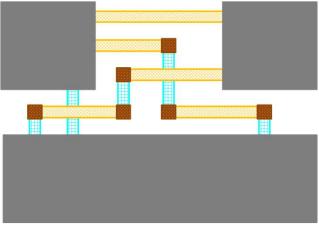

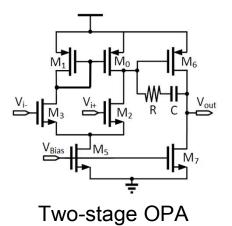

#### **Traditional Routing Methodology**

- Suitable for analog circuits?

Have lots of via in a single net

More via, more resistance

- Routing Method Comparison

- Post-layout result fails to meet the spec

□Two-stage OPA in 0.18µm

|          | Spec | Pre-sim | HV   | This work |

|----------|------|---------|------|-----------|

| Gain(dB) | >80  | 81.8    | 77.7 | 80.5      |

| GB(MHz)  | >20  | 22.2    | 19.8 | 21        |

ΗV

#### Contribution

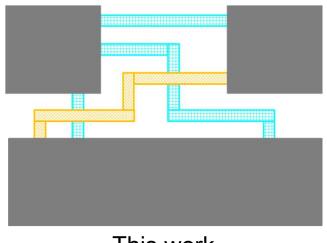

- Present an analog routing method with wire resistance consideration

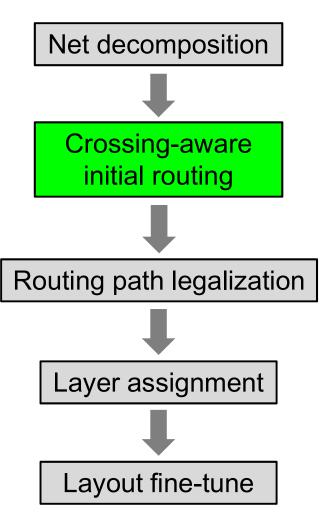

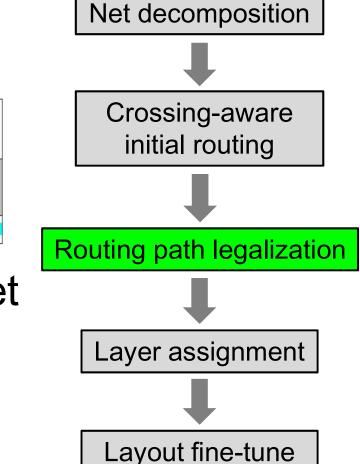

- Propose a crossing-aware initial routing

- Propose an analog routing algorithm considering wire load as well as wire length

- Propose a resistance minimization method in layer assignment stage

- Post-layout performance is improved to HV result

- Introduction

- Problem Formulation

- Algorithm

- Experimental Results

- Conclusion

#### **Problem Formulation**

- Introduction

- Problem Formulation

- Algorithm

- Experimental Results

- Conclusion

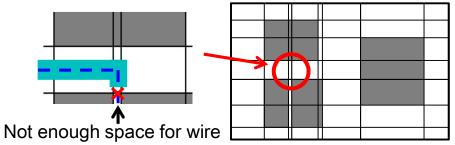

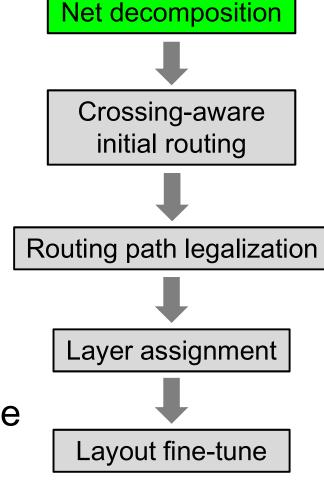

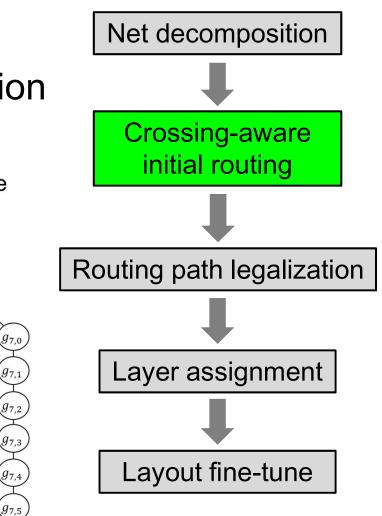

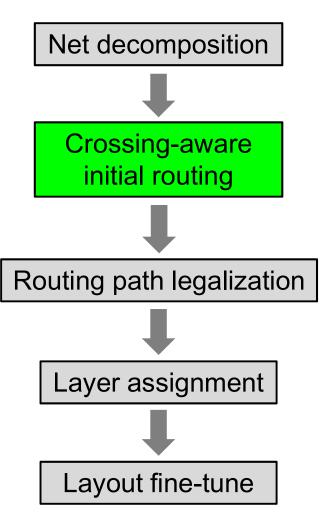

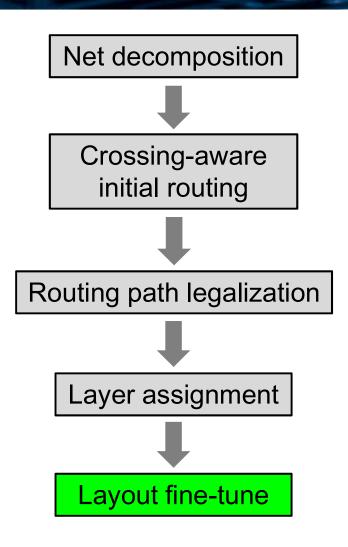

# Net Decomposition

- Routing Graph Construction

- > Build G by obstacle boundaries

- >Analyze  $g_{i,j}$  width and length

• Break multi-terminal into 2 pins

>Use FLUTE[4] generate Steiner tree

> Move Steiner points out of obs.

[4] C. Chu and Y. C.Wong, "FLUTE: Fast Lookup Table-based Rectilinear Steiner Minimal Tree Algorithm for VLSI Design," IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems, 2008.

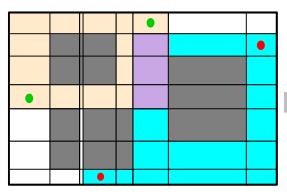

### Crossing-Aware Initial Routing (1/2)

g<sub>7,2</sub>

g<sub>7,3</sub>

g<sub>7,4</sub>

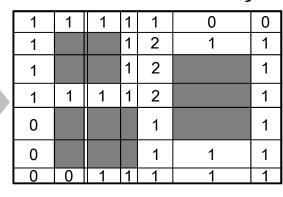

- Weighted Lee Algorithm

- Search all possible routing solution

| 15 | 14        | 12 | 11 | 10 | 6  | 2   | <i>g</i> <sub>7,5</sub> |

|----|-----------|----|----|----|----|-----|-------------------------|

| 16 |           |    | 10 | 9  | 5  | • * | 107,5                   |

|    |           |    | 11 | 10 |    | 2   |                         |

| 16 | 15        | 13 | 12 | 11 |    | 3   |                         |

|    |           |    |    | 12 |    | 4   |                         |

|    |           |    |    | 13 | 9  | 5   |                         |

|    |           | 7  | 15 | 14 | 10 | 6   |                         |

|    | $g_{3,0}$ | /  |    |    |    |     |                         |

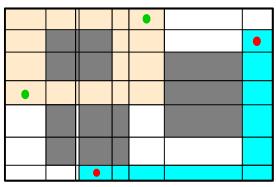

# Crossing-Aware Initial Routing (2/2)

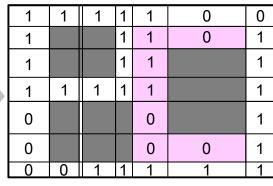

Calculate Routing Occupancy

$\geq$  How many nets will pass this  $g_{i,j}$

- Crossing consideration

- Smaller occupancy, less crossing

- > Route the net with  $\sum g_{i,j}$  (occup.)

- Update occupancy in routing region

# Crossing-Aware Initial Routing (2/2)

Calculate Routing Occupancy

$\geq$  How many nets will pass this  $g_{i,j}$

- Crossing consideration

- Smaller occupancy, less crossing

- > Route the net with  $\sum g_{i,j}$  (occup.)

- Update occupancy in routing region

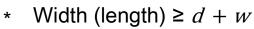

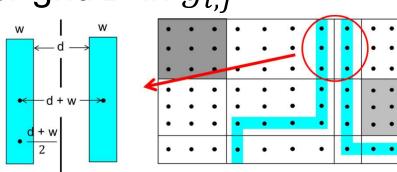

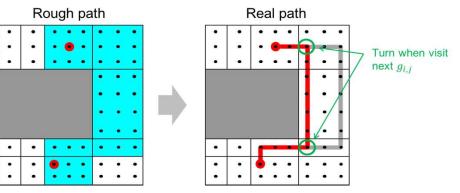

#### **Routing Path Legalization**

Construct the routing graph

$\succ$  More finer grid *D* in  $g_{i,j}$

\* D to  $D \ge d + w$

• Route the real path for each net

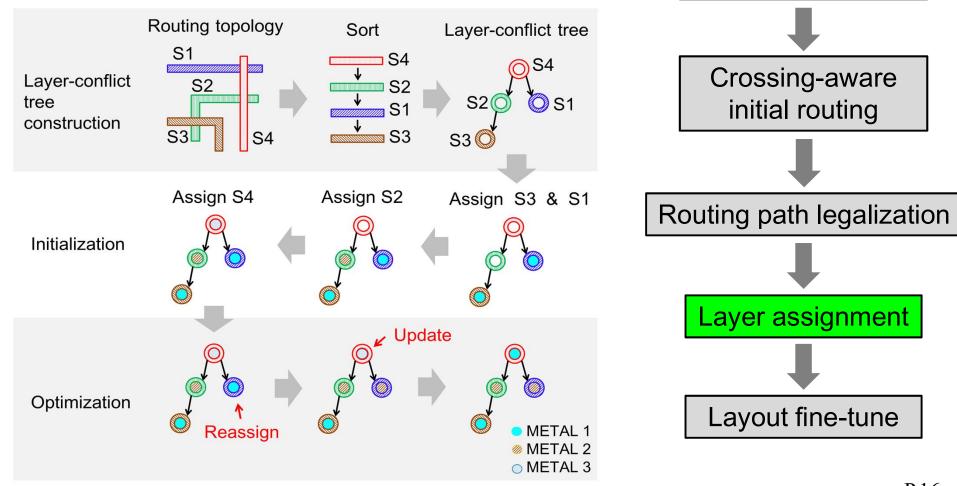

#### Layer Assignment

• Assign layer with minimal layers

Net decomposition

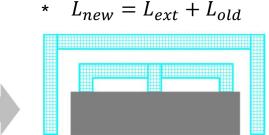

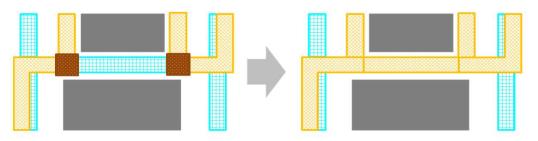

#### Layout Fine-Tune

- Wire load consideration

- Reroute multilayer nets

- \*  $L_{ext} = n_{via} * R_{via}/R_{wire}$

Reassign layer to reduce via

- Introduction

- Problem Formulation

- Algorithm

- Experimental Results

- Conclusion

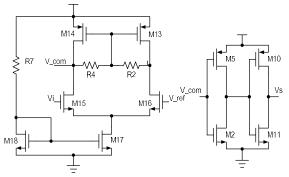

#### **Environment and Test Circuits**

Programming language, Processor & Memory

C++, Intel Xeon 3.5GHz and 64GB memory

Test case with 0.18µm process

➤Two-stage OPA, comparator

| Circuit name     | # of<br>blocks | # of<br>nets | # of pins | Total area<br>(μm²) |  |

|------------------|----------------|--------------|-----------|---------------------|--|

| Two-stage<br>OPA | 17             | 5            | 26        | 521.13              |  |

| Comparator       | 13             | 9            | 65        | 1318.94             |  |

Comparator

# Two-stage OPA

| Spec.                    | Pre-sim | Post-sim |       |      | Comparison |        |       |

|--------------------------|---------|----------|-------|------|------------|--------|-------|

|                          |         | Manual   | HV    | This | Manual     | HV     | This  |

| Gain≥<br>80(dB)          | 82      | 81.5     | 79.2  | 81.3 | -0.6%      | -3.4%  | -0.8% |

| GB ≥<br>40(MHz)          | 45      | 43       | 39.3  | 43   | -4.4%      | -12.6% | -4.4% |

| PM ≥<br>60 (°)           | 60      | 65       | 62    | 65   | +8.3%      | +3.3%  | +8.3% |

| SR ≥<br>40(V/µs)         | 40.2    | 42       | 41.5  | 42   | +4.4%      | +4.1%  | +4.4% |

| Total wire<br>length(µm) | -       | 67.6     | 81.8  | 78.9 | 1          | 1.21   | 1.17  |

| *Via Usage               | -       | 36       | 55    | 31   | 1          | 1.52   | 0.86  |

| Total wire resistance    | -       | 44.2     | 136.4 | 48.9 | 1          | 2.08   | 1.11  |

\* The double vias at the same location are counted only once

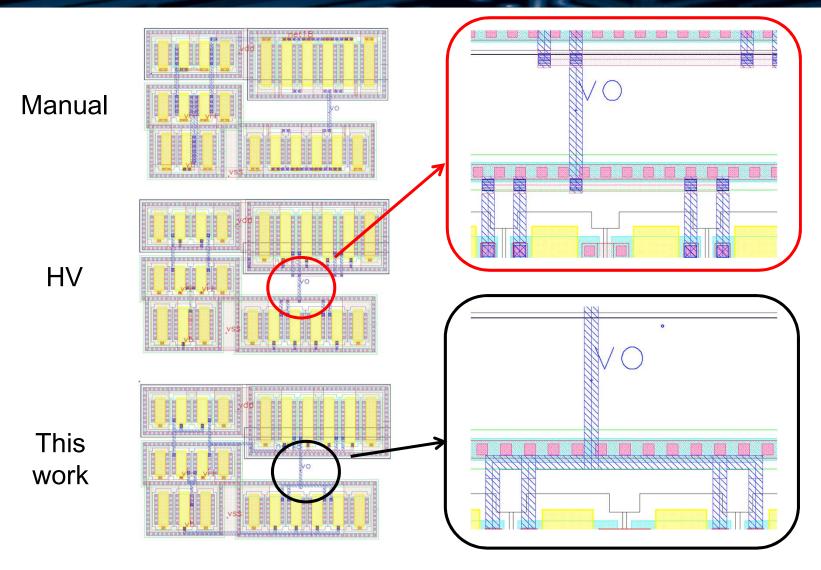

#### Layout Comparison (OPA)

P.21

### Comparator

| Spec                     | Pre-sim |        | Post-sim |        | Comparison |       |       |

|--------------------------|---------|--------|----------|--------|------------|-------|-------|

|                          |         | Manual | HV       | This   | Manual     | HV    | This  |

| Gain≥<br>30(dB)          | 30.8    | 30.9   | 30.8     | 30.9   | +0.3%      | 0%    | +0.3% |

| GB ≥<br>70(MHz)          | 70.8    | 72.4   | 71.1     | 73.2   | 2.2%       | 1.4%  | 3.3%  |

| PM ≥<br>60 (°)           | 60      | 60     | 60       | 60     | 0%         | 0%    | 0%    |

| Power ≤<br>0.25(mW)      | 0.23    | 0.21   | 0.21     | 0.21   | -8.7%      | -8.7% | -8.7% |

| Total wire<br>length(µm) | -       | 272.94 | 273.85   | 268.55 | 1          | 1.003 | 0.984 |

| *Via Usage               | -       | 57     | 117      | 44     | 1          | 2.05  | 0.77  |

| Total wire resistance    | -       | 89.7   | 172.4    | 70.6   | 1          | 1.92  | 0.78  |

\* The double vias at the same location are counted only once

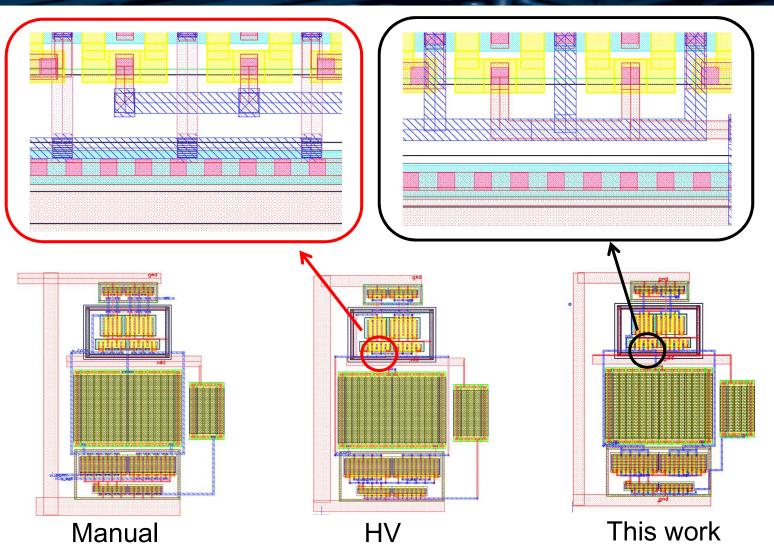

### Layout Comparison (Comparator)

- Introduction

- Problem Formulation

- Algorithm

- Experimental Results

- Conclusion

#### Conclusion

- Propose a routing algorithm that tries to minimize wire load instead of wire length

- Reduce crossing in initial routing stage

- Reduce the via usage and wire load in the layer assignment stage

- The performance loss after layout is significantly reduced with the proposed routing approach

#### Thanks for your listening