Designers' Forum

- Date: January 20-21, 2021

- Designers' Forum Co-chairs:

- Koichiro Yamashita (Fujitsu R&D Center, Japan)

- Noriyuki Miura (Osaka University, Japan)

- Designers' Forum Members:

- Koyo Nitta (NTT, Japan)

- Masaki Sakakibara (Sony Semiconductor Solutions, Japan)

- Takayuki Kawahito (Renesas Electronics, Japan)

- Chihiro Yoshimura (Hitachi, Japan)

- Takatsugu Ono (Kyushu University, Japan)

- Yuji Ishikawa (Toshiba Device & Storage, Japan)

| Date/ Time (Live Q&A chat) |

Title | |

| 5A | January 20, 15:30 - 16:00 | Oral Session: New-Principle Computer |

| 6A | January 20, 16:00 - 16:30 | Oral Session: Advanced Sensing Technology and Automotive Application |

| 8A | January 21, 15:30 - 16:00 | Oral Session: Emerging Open Design Platform |

| 9A | January 21, 16:00 - 16:30 | Oral Session: Technological Utilization in COVID-19 Pandemic |

Session 5A: (Live Q&A chat: Wednesday, January 20, 15:30 - 16:00)

Oral Session: New-Principle Computer

| Organizers: |

Chihiro Yoshimura (Hitachi, Ltd., Japan) Noriyuki Miura (Osaka University, Japan) |

| Session Chair: | Chihiro Yoshimura (Hitachi, Ltd., Japan) |

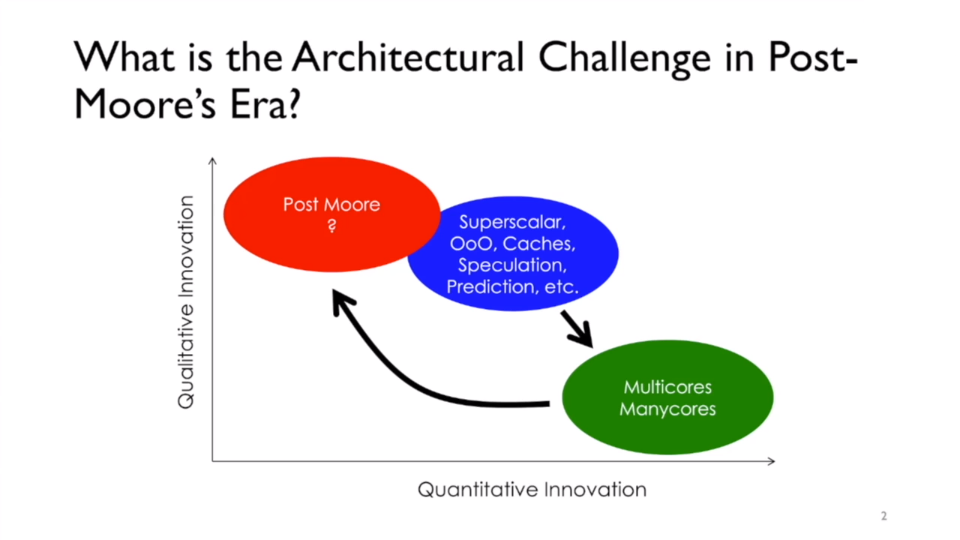

- 1: Challenges in Ultra-High-Performance Low-Power Computing towards the Post Moore Era ~ A Computer Architecture Perspective ~

Koji Inoue (Kyushu University, Japan)

Since the development of the world’s first single-chip processors in the early 1970s, advances in computer technology have taken place at an ever-increasing rate, with semiconductor integration densities increasing fourfold approximately every three years. However, this trend (known as Moore’s Law) is finally coming to an end. In other words, the quantitative approach to processor development based on increasing the integration density of transistors will no longer be practically viable (marking the beginning of the so-called post-Moore era). To challenge this critical issue, we need to bring a paradigm shift from the “quantitative approach” to a “qualitative approach” based on creating and using novel devices. This talk attempts to explore the trend in next-generation computing technologies with emerging devices and introduces two examples of research activities regarding superconductor computing and nano-photonic computing.

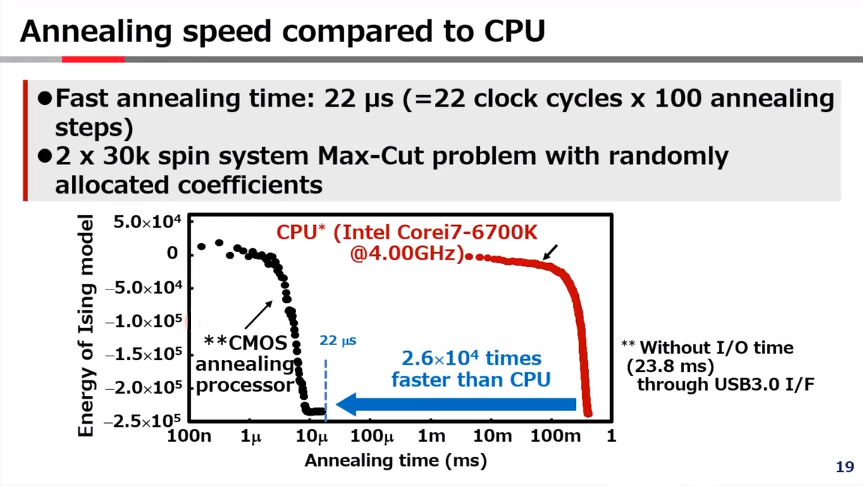

- 2: CMOS Annealing Machine for Combinatorial Optimization Problems

Masanao Yamaoka (Hitachi Ltd., Japan)

A domain-specific computing architecture is promising beyond the scaling limit in the post-Moore era. A real-time control in many fields are the most important tasks of computers in the IoT era. A new computing architecture, an annealing machine, which is specialized to solve combinatorial optimization problems, is proposed. The annealing machine maps optimization problems to an Ising model and solves the optimization problems in an instant by its own convergence property. We proposed a CMOS annealing machine, CMOS implementation of the annealing machine, which is a type of an in-memory computing architecture. The card-size prototype supports 60kbit problems. The CMOS annealing machines are expected to achieve high performance both in the cloud and at the edge. We are working on specific studies of applications toward the practical stage. For example, we have been conducting proof-of-concept experiments for a portfolio optimization in financial products.

- 3: Massively Parallel Noisy Intermediate Scale Quantum Computer

Ryuta Tsuchiya (Hitachi Ltd., Japan)

Quantum computers are expected as a new generation of computing technology that solves problems exponentially faster than conventional processors. The major challenge in quantum computer is to build a large-scale integrated system. This difficulty comes the total number of external control signals when it comes to integrating millions of qubits on one chip. Here, we propose a silicon-based quantum bit (qubit) array structure. In this array, multiple qubits are controlled in a two-dimensional array by using orthogonal word lines/bit lines like DRAM and FLASH memory cells. By sharing the signal wiring, large-scale integration of qubits is possible while suppressing an increase in the number of wirings. The fabricated array shows to have an allowable large operating voltage window to control the number of qubits. The proposed structure has a potential to pave the way for massively parallel noisy intermediate scale quantum computer.

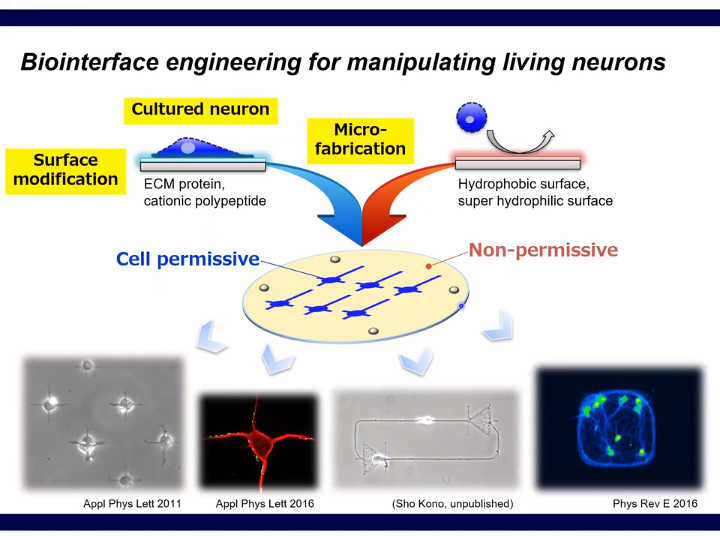

- 4: Designing Functional Neuronal Networks with Living Cells

Hideaki Yamamoto, Ayumi Hirano-Iwata, Shigeo Sato (Tohoku University, Japan)

How does a complex network of biological elements realize robust and energy-efficient computation in the brain? We approach this question by integrating semiconductor microfabrication, cell-culture technology, and numerical simulations. More precisely, we prepare micropatterns of cell-adhesion proteins on coverslips, which serve as guidance cues for the growth of cultured neurons into structured networks. Their dynamics are then recorded by fluorescence imaging, allowing us to study of how network topology sculpts multicellular dynamics. Such bottom-up analysis of living neuronal networks provides a unique approach for investigating how neurons form structured networks, generate high-dimensional dynamics, and realize information processing.

Session 6A: (Live Q&A chat: Wednesday, January 20, 16:00 - 16:30)

Advanced Sensing Technology and Automotive Application

| Organizers: |

Masaki Sakakibara (Sony Semiconductor Solutions Corporation, Japan) Yuji Ishikawa (Toshiba Corporation, Japan) |

| Session Chair: | Masaki Sakakibara (Sony Semiconductor Solutions Corporation, Japan) |

- 1: A 32x32-Pixel Global Shutter CMOS THz Imager with VCO-Based ADC

Yuri Kanazawa (Hokkaido University, Japan)

Terahertz imaging has attracted attention because of its many useful characteristics. A low-cost terahertz detector would further improve its desirability. Antenna-type CMOS terahertz imagers are low-cost and enable high-speed image capturing. However, its performance depends on its readout architecture. In this work, taking advantage of pixel parallel ADC architecture, our real-time terahertz imager achieves following features: global shutter function and digital CDS using VCO-Based ADC, noise suppression for OOK modulated signal employing the CDS. Additionally, we achieve high responsivity (218kV/W@0.93THz) with low power consumption using a MOSFET amplifier-based detector fabricated in low-cost 180nm Si-CMOS process.

- 2: Design Strategies of a Vertical Avalanche Photodiode (VAPD), Photon Count Equalizer (PCE) and Subrange Codes (SRC) for an Ultra-long Range (>250 m) Direct-/indirect Mixed Time-of-Flight (TOF) System with Reconfigurable Resolution

T. Okino, M. Ishii, Y. Sakata, S. Yamada, A. Inoue, S. Kasuga, M. Takemoto, M. Tamaru, H. Koshida, M. Usuda, T. Kunikyo, Y. Yuasa, T. Kabe, S. Saito, Y. Sugiura, K. Nakanishi, N. Torazawa, T. Shirono, Y. Nose, S. Koyama, M. Mori, Y. Hirose, M. Sawada, A. Odagawa, T. Tanaka (Panasonic Corporation, Japan)

We present design strategies of our recently developed direct-/indirect mixed time-of-flight (TOF) system based on a 6 μm□, 1200×900 pixels, Geiger-mode operated vertical avalanche photodiodes (VAPD) CMOS image sensor. The device is capable of ranging up to 250 m full range with 10 cm lateral resolution by the direct TOF mode. For short ranges (< 20 m), with assist of the indirect TOF mode, depth resolution of 10 cm is demonstrated. Full range images are output in real time (30 fps) with a 450 fps capture speed of each subrange image. We focus on three key elements; (i) a pixel design based on VAPD with a capacitive selfquenching free from after-pulse. (ii) a photon count equalizer (PCE) that enables clear separation of photon count peaks. (iii) subrange- coding (SRC)/synthesis (SRS) architectures configurable for various applications and scenes. Major tradeoffs such as SRC vs. pulse counts and external light vs. range are discussed.

- 3: A 240×192-Pixel 225m-Range Automotive LiDAR SoC Using a 40ch Voltage/Time Dual-Data-Converter-Based AFE

Satoshi Kondo (Toshiba Corporation, Japan)

A safe and reliable self-driving system is a key enabling technology for a society without traffic jams or accidents; LiDAR plays an essential role for such systems. To ensure higher levels of safety and comfort, early detection of small objects (e.g., debris/children) is crucial. To achieve this, state-of-the-art LiDARs must attain even more finely scaled pixel resolution. However, hybrid LiDAR systems require a pair of TDC/ADC AFEs per pixel to obtain both precise short-range distance measurement (DM) and 200m long-range DM. Scaling the pixel resolution will significantly enlarge the SoC area and explode its cost. We report a dual-data converter (DDC) that consolidates the functions of ADC and TDC into a single circuit; as such, a significant reduction in the area of the Hybrid LiDAR AFE is achieved. The DDC acquires both high-precision time and voltage data from the input: although it achieves 5× smaller AFE area than prior arts. This innovation leads to a 40-channel AFE integration of the SoC without increasing cost. Moreover, owing to the high ADC performance of DDCs, DM under 70klux sunlight was 12% longer, achieving 225m.

- 4: ViscontiTM: Edge AI Processor for Automotive Application

Yutaka Yamada (Toshiba Corporation, Japan)

In this presentation, we introduce our image recognition SoC for advanced driver assistance system (ADAS). Vehicles with ADAS contribute to reduce traffic accidents and are widely available today. Image recognition SoCs are essential devices for ADAS application including many image recognition functions. ADAS application needs high performance SoCs that execute the functions such as raw image capture, several image filters, object recognitions, and sending alerts. On the other hand, these SoCs have tight constraint of power consumption due to high temperature inside the vehicle and the limited cooling system. Our SoC provides all the functions that ADAS application needs by several power-efficient and programmable hardware acceleration.

Session 8A: (Live Q&A chat: Thursday, January 21, 15:30 - 16:00)

Oral Session: Emerging Open Design Platform

| Organizers: |

Yuji Ishikawa (Toshiba Corporation, Japan) Noriyuki Miura (Osaka University, Japan) |

| Session Chair: | Yuji Ishikawa (Toshiba Corporation, Japan) |

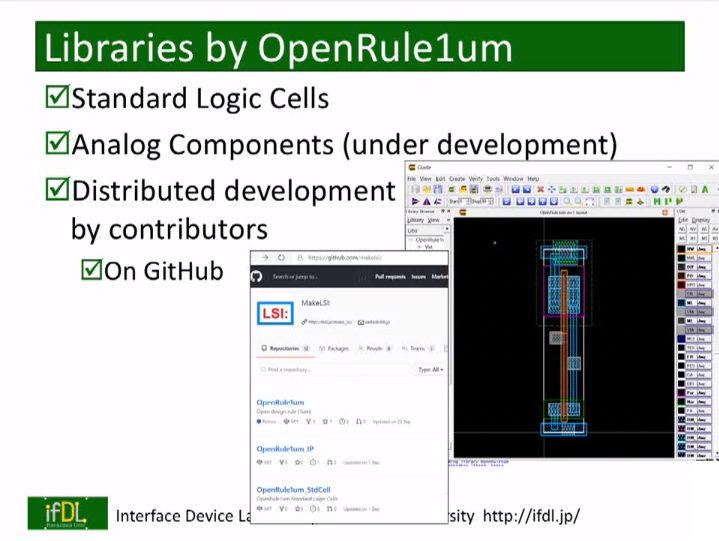

- 1: Impact of Open Source and NDA-free on LSI Design and Fabrication

Junichi Akita (Kanazawa University, Japan)

The continuous development of LSI technologies has been realizing the more sophisticated society based advanced technologies such as AI and IoT, and it also has been making demands on more complicated and large scale LSI chip that integrates the whole computing systems into a single chip, as well as the more complicated EDA tools. There also have been continuous development on the open-source EDA tools in each layer of LSI design from the process simulation to the high level synthesis, and there some tools that we can use for the practical LSI designs. It is also notable the development of LSI technologies also requires us the NDA for obtaining the process design kit including the libraries, since the process technologies are high level confidential information. This NDA also has been restricting the potential applications and the users of LSI technologies, while there are some recent activities using the open source, NDA-free technologies to form the emerging ecosystem of LSI industries. In this talk, I introduce the history and the recent trend of the open-source, NDA-free LSI design tools and practices.

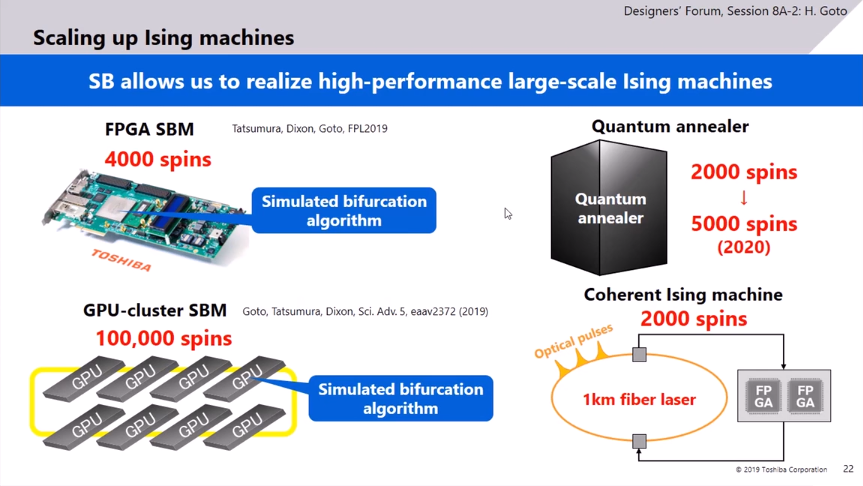

- 2: Simulated Bifurcation Algorithm for Large-scale Combinatorial Optimization

Hayato Goto (Toshiba Corporation, Japan)

Combinatorial optimization problems appear in various situations, including circuit design. However, such problems are extremely hard because of exponential increase in the number of solution candidates depending on problem sizes. For this reason, quantum computing is expected to be useful for combinatorial optimization. In 2019, we proposed a new quantum-inspired classical algorithm for combinatorial optimization, which we call “simulated bifurcation (SB).” Exploiting the high parallelizability of SB, our SB-based machine implemented with a FPGA or GPUs demonstrated high performance for large-scale problems. This result opens the possibility for the acceleration of combinatorial optimization by many-core processors.

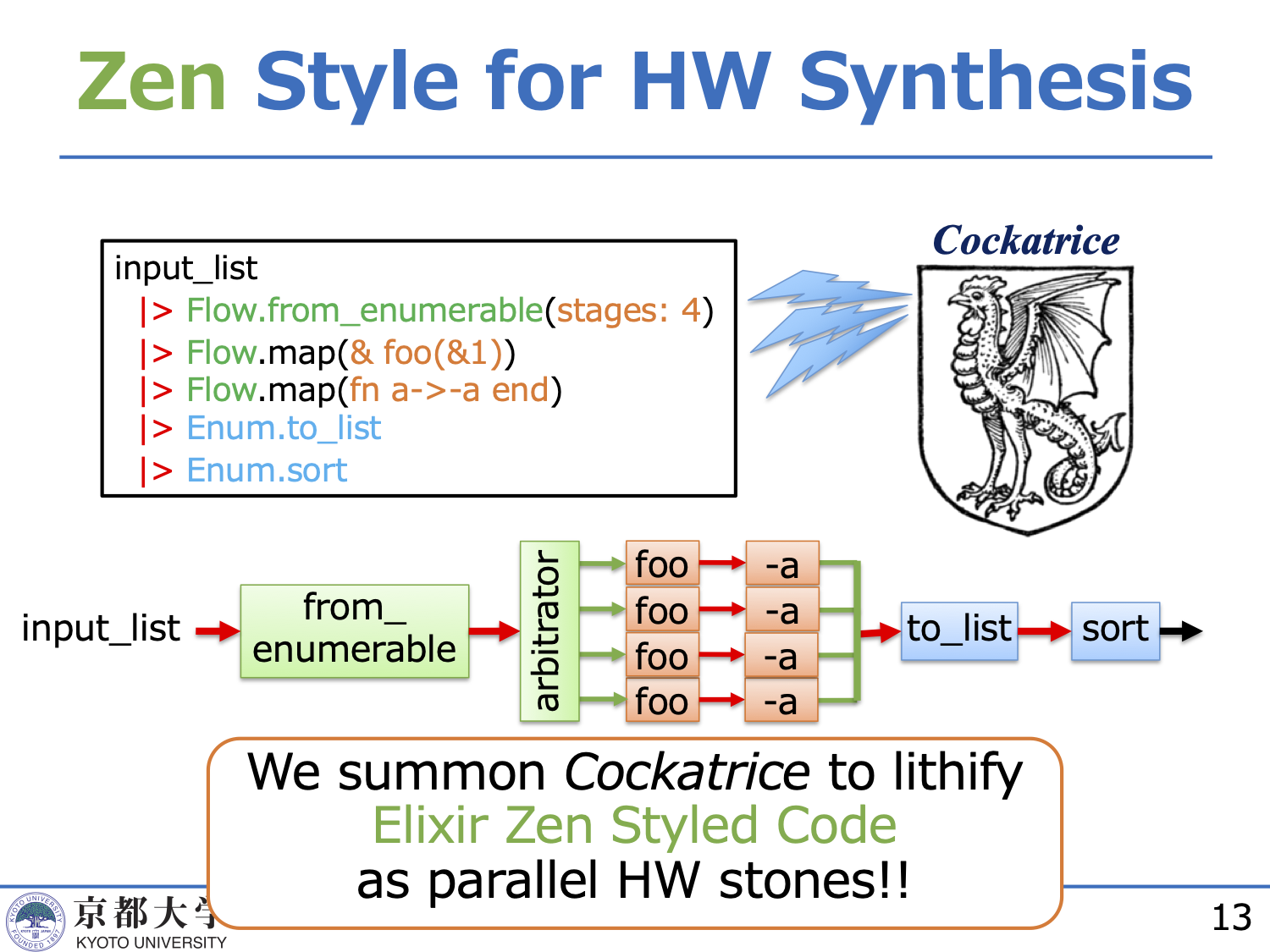

- 3: Towards a Hardware Synthesis Environment from the Functional Language Elixir

Hideki Takase (Kyoto University/JST PRESTO, Japan)

Elixir is a functional language that runs on the Erlang VM. We suggest that the Elixir description has the affinity with the data flow hardware architecture. This talk presents a hardware synthesis method from the Elixir description. We propose a synthesis flow for the data flow architecture on the FPGA from the design description written by Elixir. Our method can synthesize the functional equivalence circuit from the libraries for direct manipulation and parallel processing of data collection in Elixir. Data flow is directly constructed base on the pipe operator that connects the processing relations of the function in the data processing order. Our method can contribute to performance and power efficiency in the server that reconfigure its hardware as required by Elixir applications.

Session 9A: (Live Q&A chat: Thursday, January 21, 16:00 - 16:30)

Oral Session: Technological Utilization in COVID-19 Pandemic

| Organizer: | Koichiro Yamashita (Fujitsu R&D Center Co., LTD., Japan) |

| Session Chair: | Koichiro Yamashita (Fujitsu R&D Center Co., LTD., Japan) |

- 1: ToF 3D Object Detection: Crowd Status Monitoring with Protected Privacy

Wang Weihang, Ge Hao (Data Miracle Intelligent Technology Co.,Ltd., China), Liu Peilin (Shanghai Jiao Tong University, China)

To ensure the safety of the public in the outbreak of COVID-19, it is necessary to monitor the crowd density and distribution in real-time with ToF cameras. They are employed to achieve intelligent sensing and computing with protected privacy, such as the number of people in an area of interest, crowd density distribution, distance between people, and so on. In this report, some researches and applications of head detection, people counting, and crowd density estimation by using the ToF camera are introduced.

- 2: Smartphone App to Support Team Communication in Remote Work

Satomi Tsuji (Hitachi Ltd., Japan)

Due to COVID-19, Hitachi Ltd. has introduced remote working across the company from April 2020. The concern there was the lack of spontaneous communication, especially chit-chat, which reduced teamwork, decision-making speed and creativity, and increased stress risk of employees. We have conducted research on the utility of face-to-face communication and have confirmed that short conversations and being spoken in an even distribution is effective in improving team productivity. Based on these findings, we created a smartphone app that includes a communication supporting and evaluation system. In this presentation, we will introduce approach and results of our PoC with hundreds of employees called "Remote work together".

- 3: Re-ID Technology: Chase of the Contact Person with Protected Privacy

Chang Zhigang, Zheng Shibao (Shanghai Jiao Tong University, China)

Person Re-ID plays an important role in multi-camera tracking, by matching paired person images crossing non-overlapping views. It is more privacy protected than face recognition, with more comprehensive factors considered than face feature, such as body shape, clothes, poses, and gaits etc. In this report, the research of feature extraction, metric learning, solution for difficulties in Re-ID, and Semi-supervised/unsupervised Re-ID methods are introduced. Meanwhile, the application of tracking contact person in epidemic of COVID-19 is also discussed.

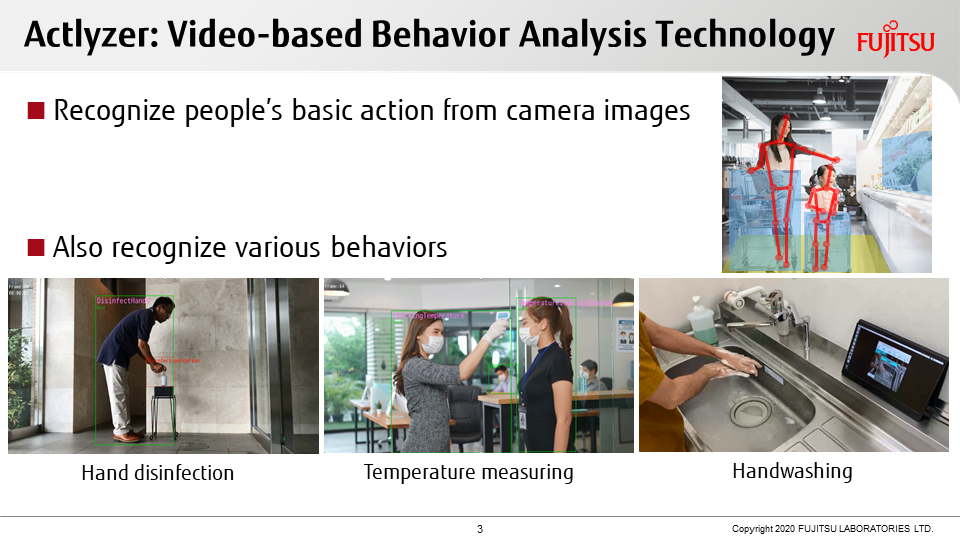

- 4: Actlyzer :Video-based Behavior Analysis Technology

Toshiaki Wakama (Fujitsu Laboratories LTD., Japan)

New behaviors, such as social distancing and frequent hand washing, are required for prevention of spread of COVID-19. We developed "Actlyzer", a novel video-based behavioral analysis technology, which makes it possible to alert behaviors with high-risk of infection and record properly performed hygiene management behaviors. Actlyzer can detect almost 100 human’s basic actions and this enables it to recognize more complex behaviors by defining them as combination of the basic actions. For example, it is possible to detect two people facing each other for long time and body-touching such as hug and handshaking. Moreover, Actlyzer can also recognize hand actions and it can be used to judge if hand washing is correctly performed or not. Even unfamiliar people can properly wash their hands since it provides real-time guidance depending on their actions. We will make use of Actlyzer to support the more effective measures against COVID-19 at medical sites, event sites, and restaurants.