# Thermal-Aware Layout Optimization and Mapping Methods for Resistive Neuromorphic Engines

Chengrui Zhang, Yu Ma, and Pingqiang Zhou

- Background

- Spiking Neural Networks (SNNs)

- Memristor Crossbar Array (MCA) based Accelerators

- Problem Formulation

信息科学与技术学院 School of Information Science and Technology

- Proposed Techniques

- Thermal-Aware Layout Design

- Input-sensitive Cross-Array Mapping

- Experimental Results

- Summary

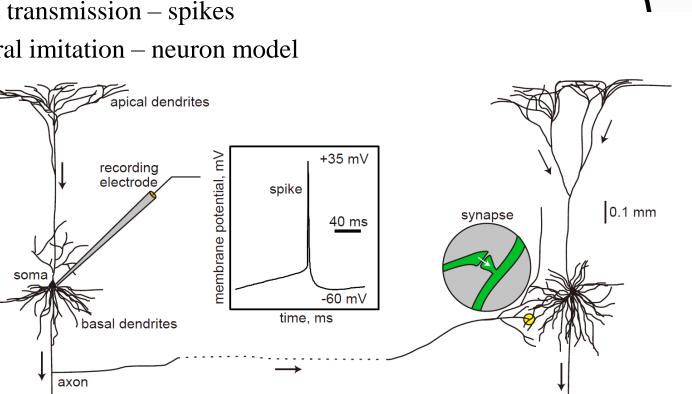

# Spiking Neural Networks (SNNs)

- The **third** generation of artificial neural networks (ANN)

- Simulation of biological neurons

- Data transmission spikes

- Neural imitation neuron model

E. M. Izhikevich, Dynamical systems in neuroscience : the geometry of excitability and bursting, 2007.

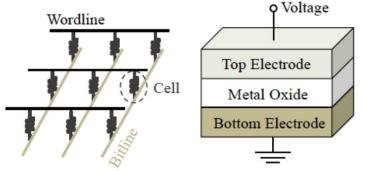

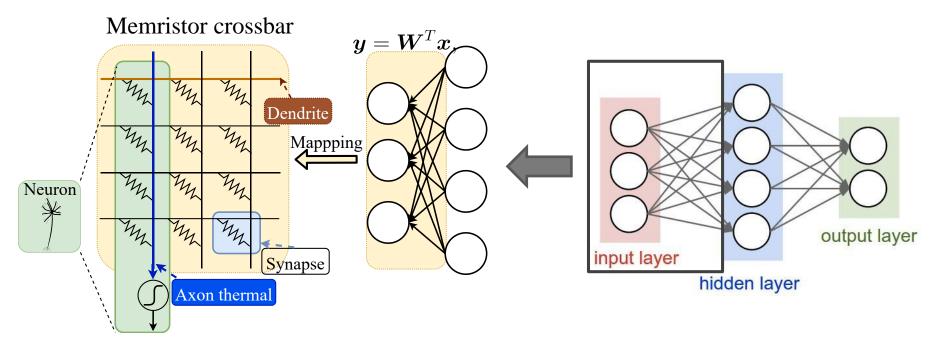

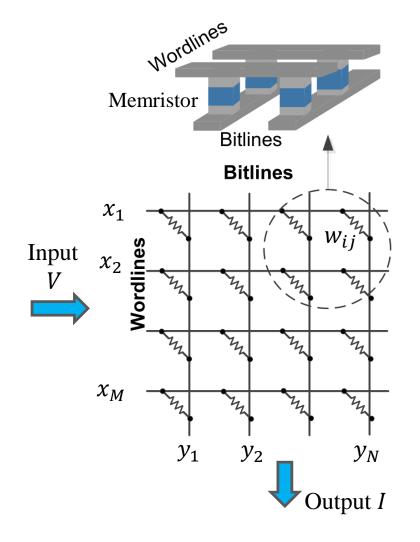

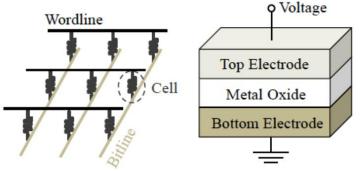

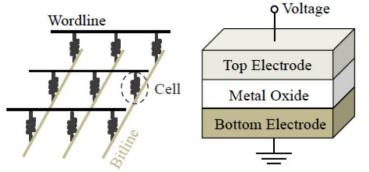

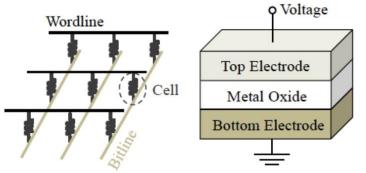

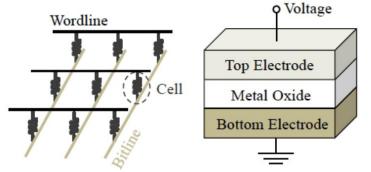

## Memristor-based Neural Network Accelerators

- Promising accelerator architecture for deep learning applications

- Weights stored in Memristor crossbar

- "Process in memory" manner

- Less data movements

- High density computation: Multiply Accumulate with time complexity O(1)

#### Memristor-based Neural Network Accelerators

$$oldsymbol{y} = oldsymbol{W}^T oldsymbol{x}, \ W \in R^{M imes N}, x \in R^M, y \in R^N$$

$I_n = \sum_{m=1}^M G_{m,n} V_{in,m} \quad G \in R^{M imes N}, V \in R^M$

| Input vector          | x |

|-----------------------|---|

| Weight matrix         | W |

| Output vector         | у |

| Input voltage vector  | V |

| Conductance matrix    | G |

| Output current vector | Ι |

- Background

- Spiking Neural Networks (SNNs)

- Memristor Crossbar Array (MCA) based Accelerators

- Problem Formulation

信息科学与技术学院 School of Information Science and Technology

- Proposed Techniques

- Thermal-Aware Layout Design

- Input-sensitive Cross-Array Mapping

- Experimental Results

- Summary

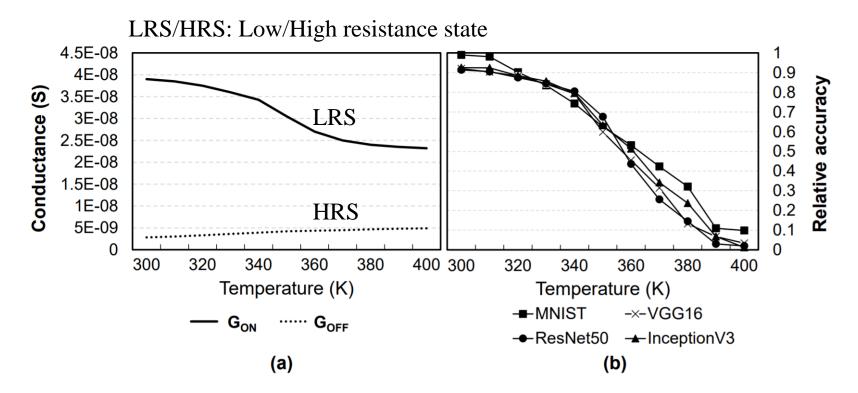

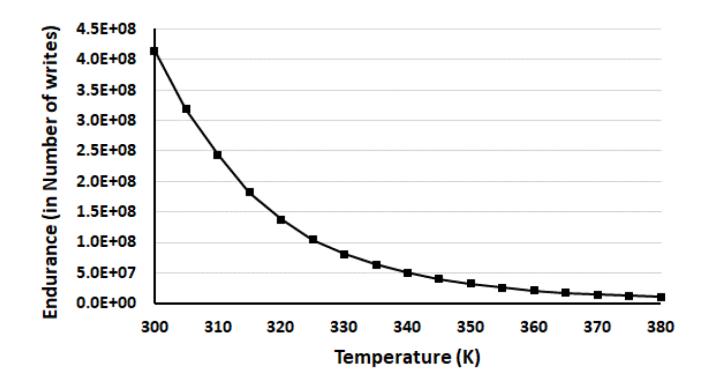

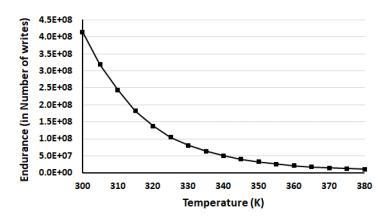

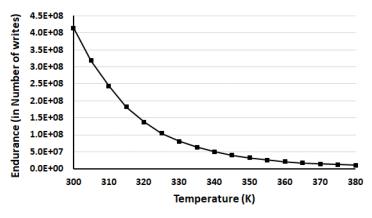

# Reliability Challenge: Thermal Effect

- Conductance changes as temperature changes

- Accuracy & endurance degradation

X. Liu, M. Zhou, T. S. Rosing and J. Zhao, "HR3AM: A Heat Resilient Design for RRAM-based Neuromorphic Computing," ISLPED, 2019.

## Reliability Challenge: Thermal Effect

- Conductance changes as temperature changes

- Accuracy & endurance degradation

Valad Beigi and M., Memik G, "Thor: Thermal-aware optimizations for extending ReRAM lifetime", IPDPS, 2018.

## **Related Works**

- Compensate conductance decrease [X. Liu, ISLPED 2019]

- Weight training [S. Zhang, DATE 2019]

- Reduce the total weight value to reduce total conductance

- Thermal-aware mapping [H. Shin, ICCAD 2020]

- Even the power distribution to reduce the maximum temperature

- Background

- Spiking Neural Networks (SNNs)

- Memristor Crossbar Array (MCA) based Accelerators

- Problem Formulation

- Proposed Techniques

- Thermal-Aware Layout Design

- Input-sensitive Cross-Array Mapping

- Experimental Results

#### Summary

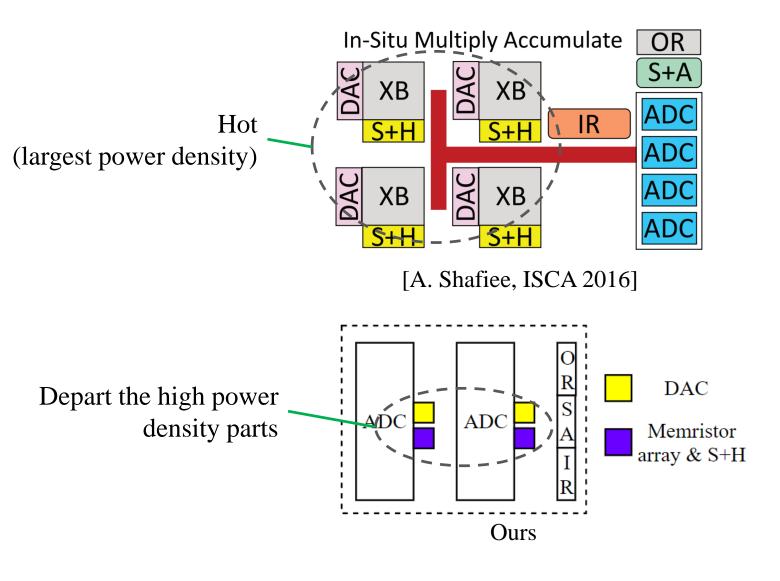

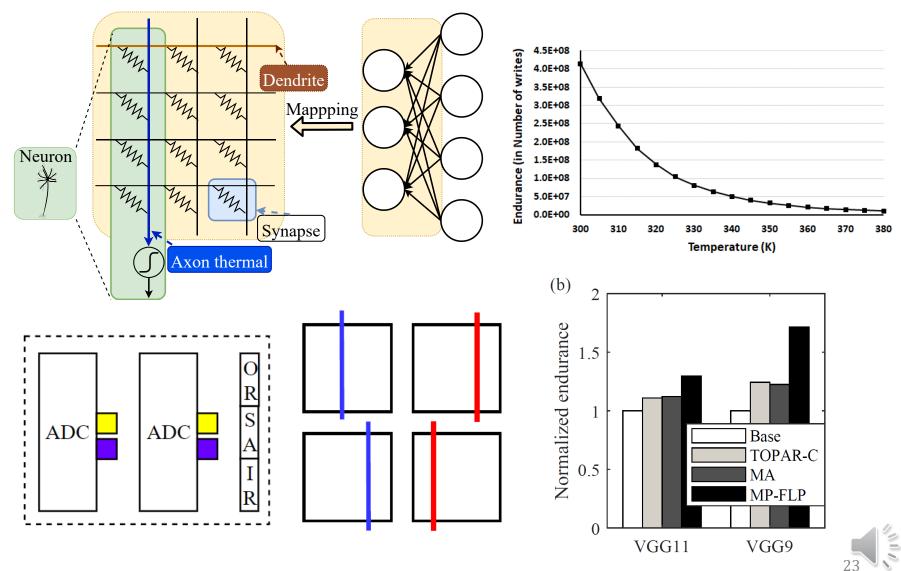

#### Thermal-Aware Layout Design

#### Thermal-Aware Layout Design

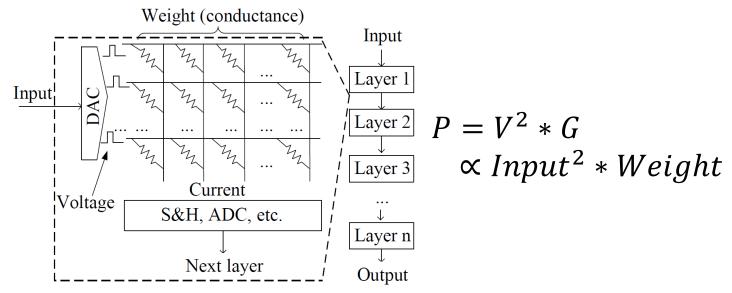

## Thermal-Aware Layout Design

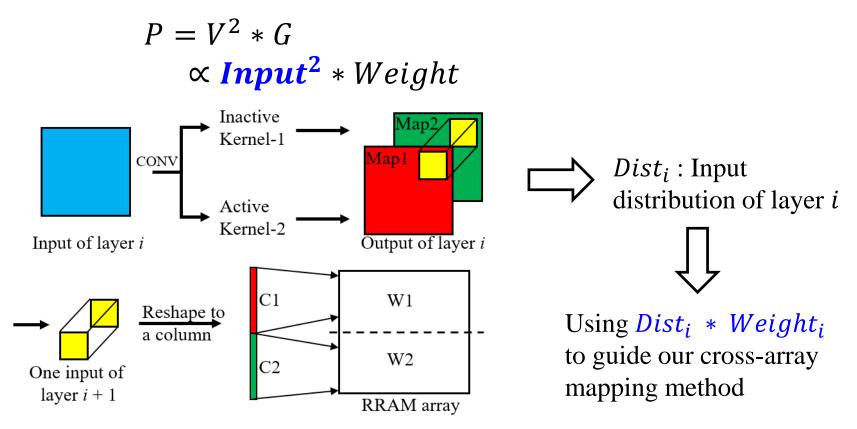

One inference step in SNN from layer *i* to layer i + 1

$$P = V^2 * G$$

$$\propto Input^2 * Weight$$

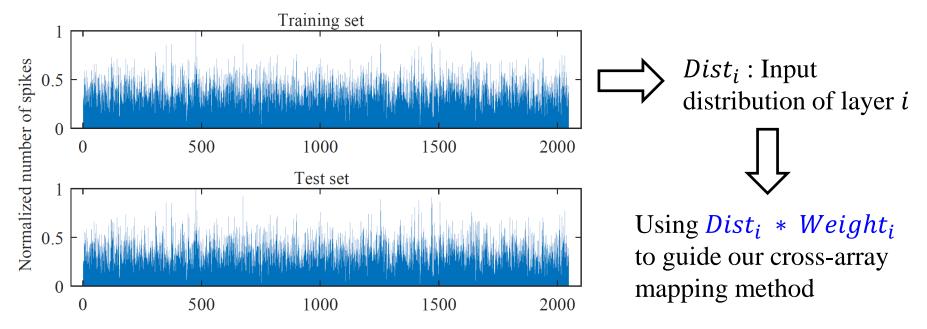

The normalized input distribution of the second fully-connected layer of VGG11 in training set and test set

$P = V^2 * G$  $\propto Input^2 * Weight$

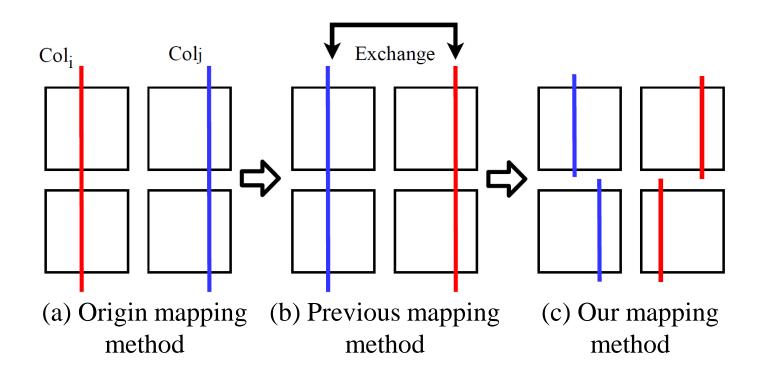

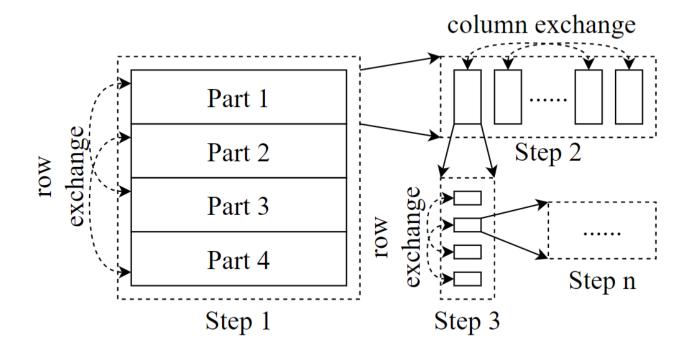

$\min(\max P - \min P)$ s.t.every row (or column) in w<sub>i</sub> must be in the same row (or column) of origin weight

Illustration of proposed re-ordering method.

- Background

- Spiking Neural Networks (SNNs)

- Memristor Crossbar Array (MCA) based Accelerators

- Problem Formulation

信息科学与技术学院 School of Information Science and Technology

- Proposed Techniques

- Thermal-Aware Layout Design

- Input-sensitive Cross-Array Mapping

- Experimental Results

- Summary

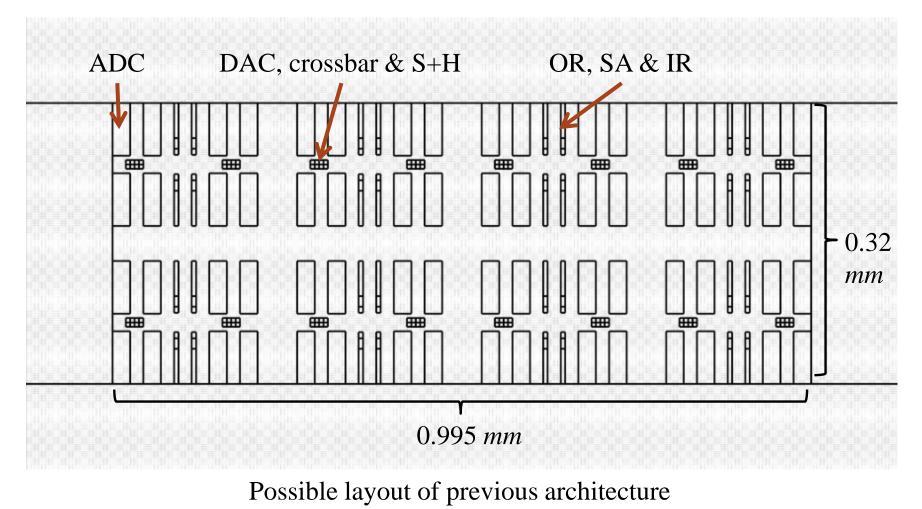

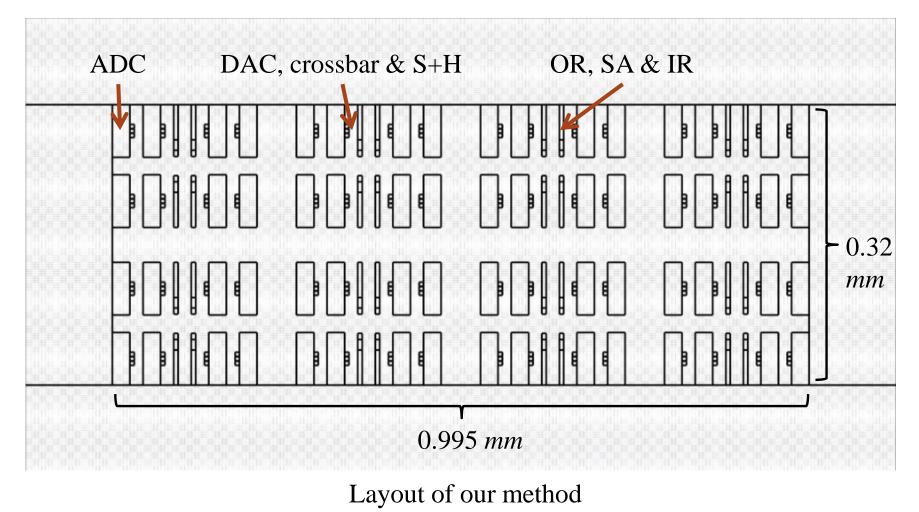

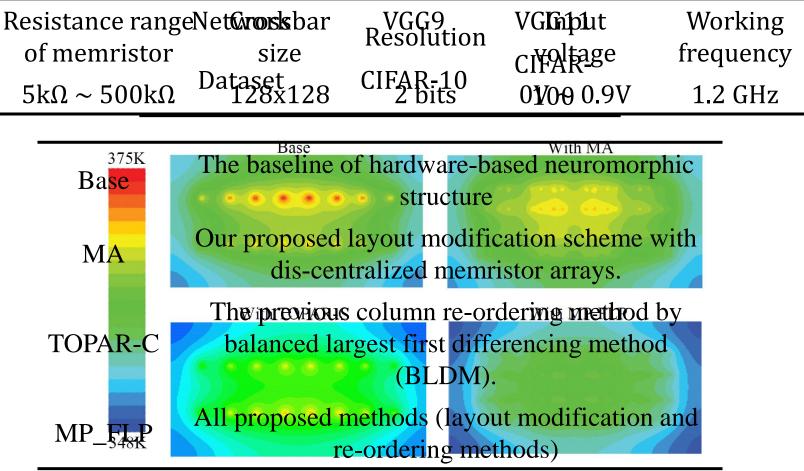

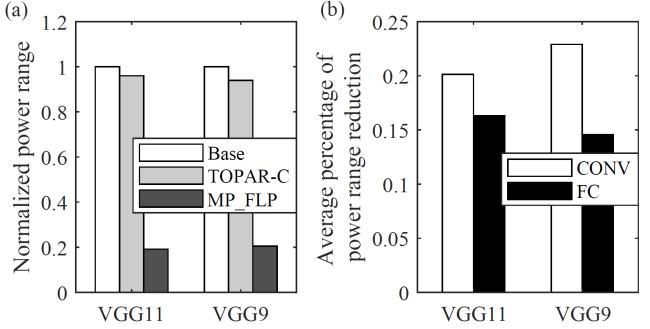

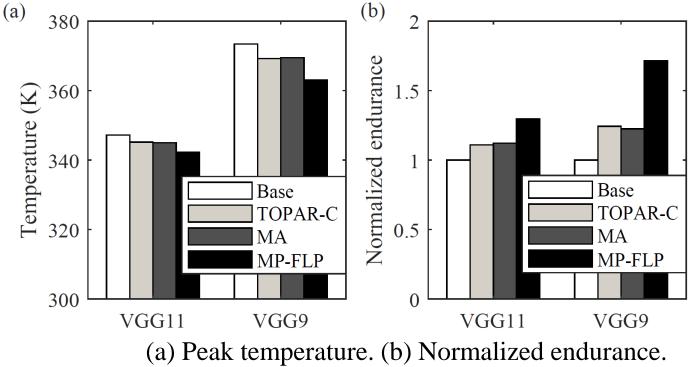

## **Experimental Results**

The temperature distribution of the hottest tile in the third fullyconnected layer of VGG9.

## **Experimental Results**

- Peak temperature reduction: 10.4K

- Endurance improvement: 72%

(a) The normalized power range. (b) The average percentage of power range reduction.

## **Experimental Results**

- Peak temperature reduction: 10.4K

- Endurance improvement: 72%

- Background

- Spiking Neural Networks (SNNs)

- Memristor Crossbar Array (MCA) based Accelerators

- Problem Formulation

信息科学与技术学院 School of Information Science and Technology

- Proposed Techniques

- Thermal-Aware Layout Design

- Input-sensitive Cross-Array Mapping

- Experimental Results

#### Summary

# Summary

# **Thanks!**

zhangchr@shanghaitech.edu.cn