## Supply-Variation-Tolerant Transimpedance Amplifier Using Non-Inverting Amplifier in 180-nm CMOS

Tomofumi Tsuchida, Akira Tsuchiya, Toshiyuki Inoue, and Keiji Kishine Department of Electronic Systems Engineering, The University of Shiga Prefecture

- Background

- Comparing the reference TIA and the proposed TIA

- Design of the proposed TIA

- Measurement result

- Conclusion

- Background

- Comparing the reference TIA and the proposed TIA

- Design of the proposed TIA

- Measurement result

- Conclusion

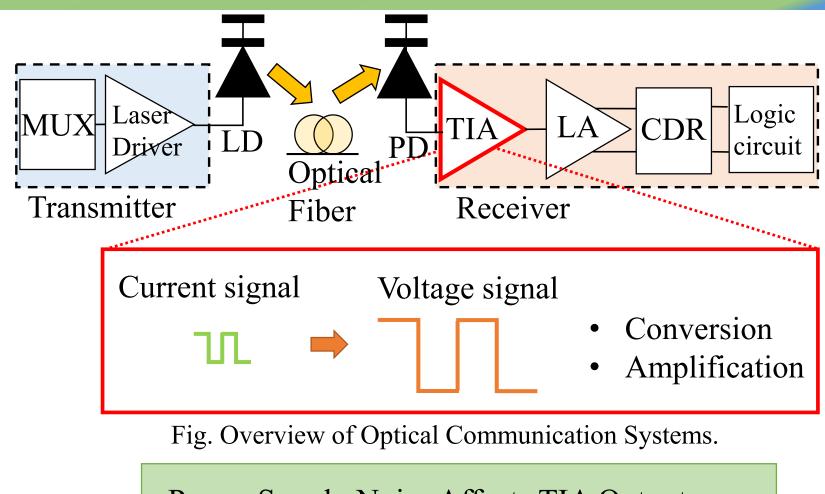

## Overview of Optical Communication Systems

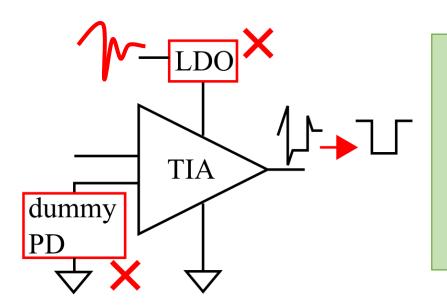

Power Supply Noise Affects TIA Output.

The bit error rate increases.

Commonly, power supply noise reduction uses extra circuits.

High performance extra circuits increase the costs.

- Power consumption

- Area

- Another power supply

# We realize Supply-noise-tolerant TIA without extra circuits.

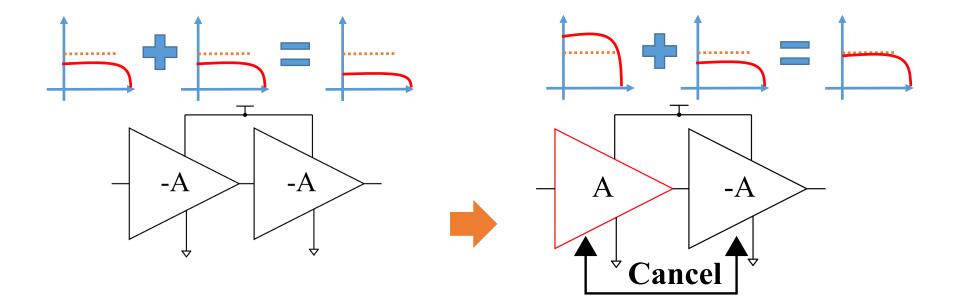

## Our key idea

#### Invert the characteristic of circuit.

### How we invert the characteristic of TIA?

- Background

- Comparing the reference TIA and the proposed TIA

- Design of the proposed TIA

- Measurement result

- Conclusion

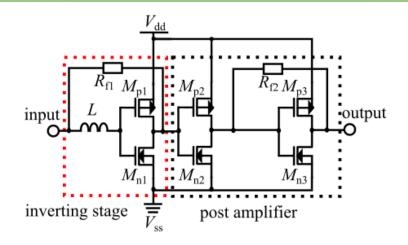

## The reference TIA

Fig. Schematic of the reference TIA.

A combination of a inverting stage and post amplifier

The gain of the inverting stage

The supply voltage drops and the current through the MOS decreases. The gain of the inverting stage and post amplifier decrease.

# The combination of a circuit that increases gain when the current decreases.

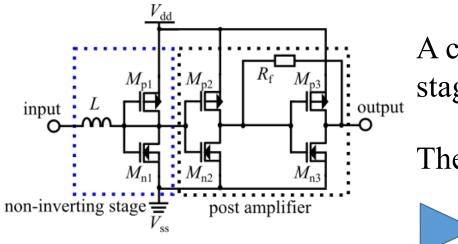

## The proposed TIA

Fig. Schematic of the proposed TIA.

A combination of a non-inverting stage and post amplifier

The gain of the non-inverting stage

By supply voltage drop

- The gain of the non-inverting stage increases.

- The gain of post amplifier decreases.

Cancel out the effects of power supply voltage drop

- Background

- Comparing the reference TIA and the proposed TIA

- Design of the proposed TIA

- Measurement result

- Conclusion

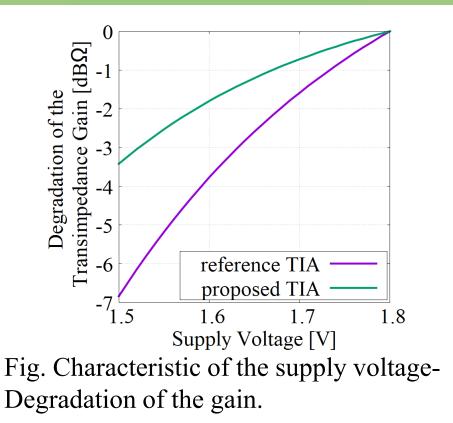

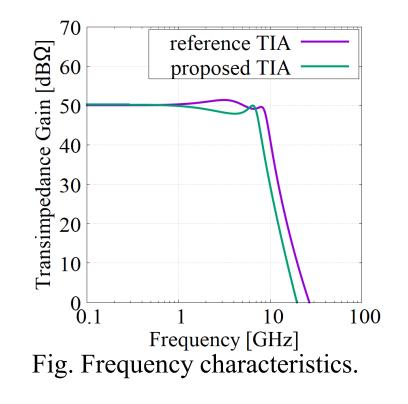

## Evaluation in simulation

Merit : Tolerance to power supply variationsDemerit : Degradation of bandwidth

Eye diagram of proposed TIA at 1.5V is good.

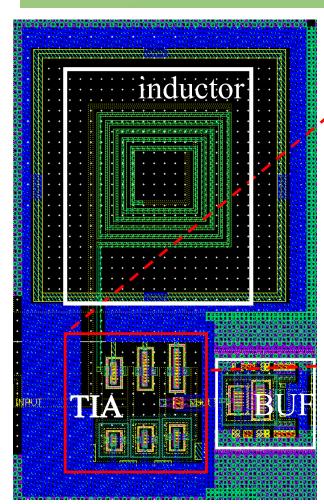

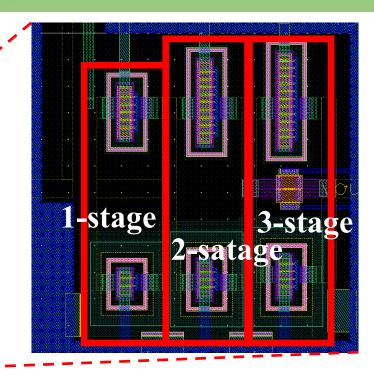

## Design of the proposed TIA

The drain and gate terminals of the first stage are shorted.

Bandwidth extension using series peaking

Fig. Layout view of the proposed TIA and the output buffer.

## Design parameters

| Design parameters | (reference TIA) |

|-------------------|-----------------|

|-------------------|-----------------|

| Mn1   | Mp1   | Mn2   | Mp2   | Mn3   | Mp3   |

|-------|-------|-------|-------|-------|-------|

| 10 µm | 36 µm | 10 µm | 28 µm | 12 µm | 34 µm |

| resistance Rf1, Rf2 | inductance L |

|---------------------|--------------|

| 350 Ω               | 4 nH         |

Performance (reference TIA)

Power consumption : 6 mWGain :  $50 \text{ dB}\Omega$ Bandwidth : 9.0 GHz

Design parameters (proposed TIA)

| Mn1  | Mp1   | Mn2   | Mp2   | Mn3   | Mp3   |

|------|-------|-------|-------|-------|-------|

| 6 µm | 20 µm | 12 µm | 36 µm | 14 µm | 42 µm |

| resistance Rf | inductance L |

|---------------|--------------|

| 300 Ω         | 7 nH         |

Performance (proposed TIA)

Power consumption : 6 mWGain :  $50 \text{ dB}\Omega$ Bandwidth : 7.3 GHz

#### Constraints : 50 dB $\Omega$ , 6 mW

**Designed for high power supply variation tolerance.**

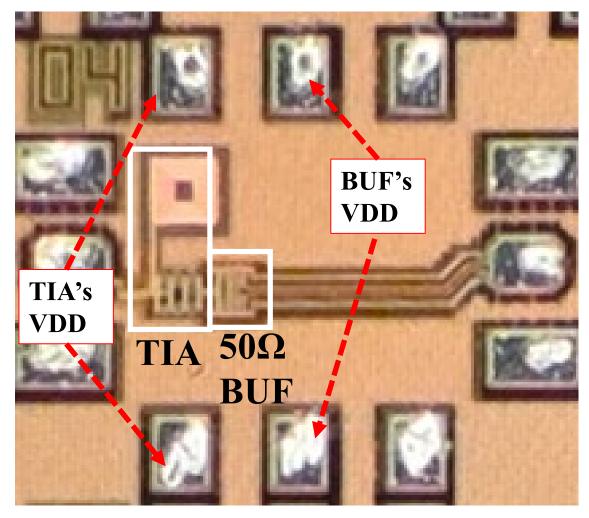

## Overview of the chip design

• 180-nm CMOS

• On-wafer probing

Fig. Chip microphotograph of TIA and output buffer.

- Background

- Comparing the reference TIA and the proposed TIA

- Design of the proposed TIA

- Measurement result

- Conclusion

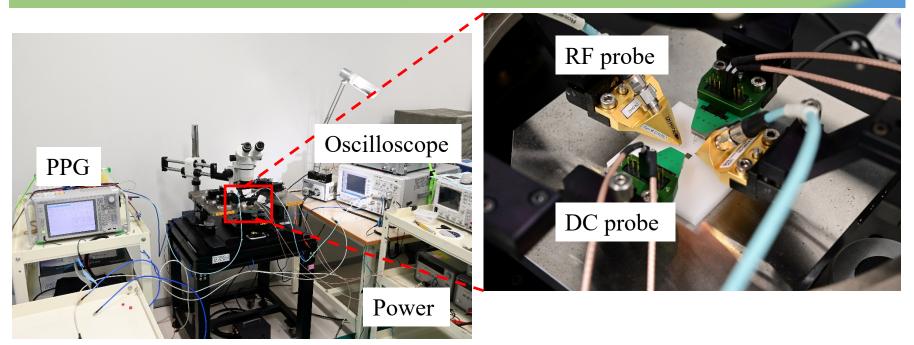

## Measurement set up (1)

Fig. Photo of the measurement system.

- Generate PRBS with Pulse Pattern Generator (PPG)

- Measure eye diagram with oscilloscope

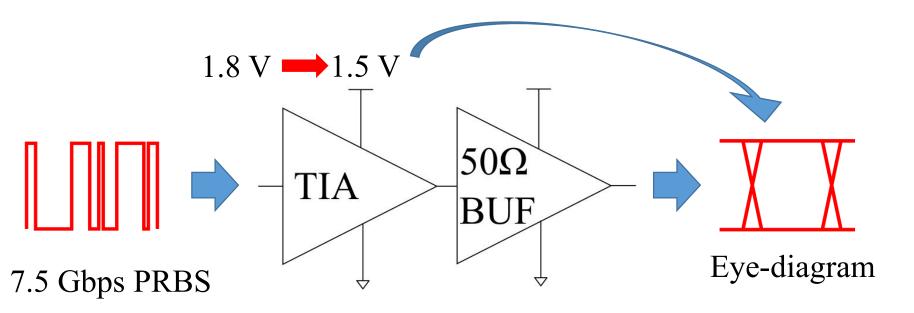

## Measurement set up (2)

- Standard voltage is 1.8 V.

- TIA's power supply considers voltage drop by noise.

- TIA and BUF power supplies are separated.

Measure the effect of TIA supply voltage drop on the eye diagram.

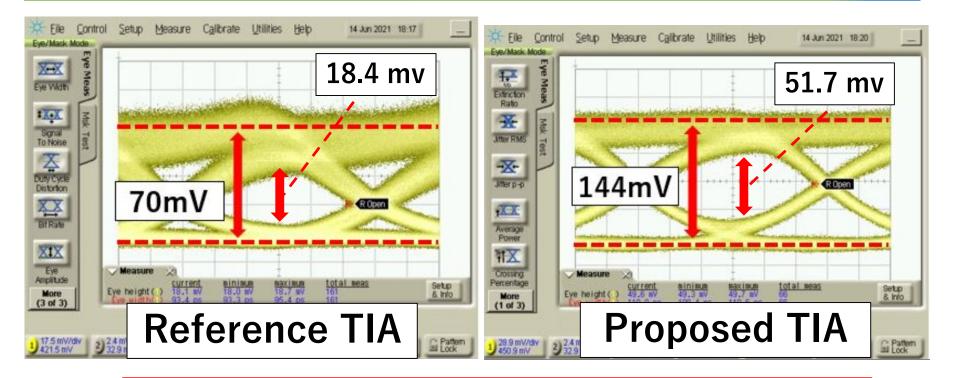

### Measurement result

Amplitude (Low level-Hi level) : Improved 2 times Eye-opening voltage : Improved 3 times

## Proposed TIA is good eye diagram.

- Background

- Comparing the reference TIA and the proposed TIA

- Design of the proposed TIA

- Measurement result

- Conclusion

## Conclusion

#### Our key idea :

- Combining the non-inverting and the inverting amplifier circuits.

- Cancel the effect of power supply variation.

- 180-nm CMOS process

- On-wafer probing

- TIA's supply voltage drops to 1.5 V from 1.8 V.

- Input signal is 7.5 Gbps PRBS.

#### **Measurement result :**

- Amplitude (Low level-Hi level) : Improved 2 times

- Eye-opening voltage : Improved 3 times

## Thank you for listening