Erick Chao, Sr. Software Architect

## EDA Enables AI/ML Designs

**IP and Subsystems**

Implementation

**Board and Package**

Systems

IP Selection "Reuse the right building blocks" DSPs, Interfaces, Analog

#### **HW/SW** Verification

**"Is it functionally correct?"** Hardware/Software, Power, Architecture, Safety, Security

Chip Implementation "Optimized, advanced-node implementation" Performance, Power, Cost

#### Packaging PCB Integration

"Silicon into packages and parts into PCBs and 3D-IC heterogeneous integration"

#### System Analysis "Does it work when put together?"

Electromagnetic, Thermal, Low Power, Computational Fluid Dynamics Optimized flows to enable AI/ML chips and systems (for users)

## AI/ML is **Enabling EDA** too!

IP Selection "Reuse the right building blocks" DSPs. Interfaces inalog

**HW/SW Verification**

**Development productivity**

# Using Al/ML to increase productivity of EDA flows

"Silicon into packages and parts into PCBs and 3D-IC heterogeneous integration"

System Analysis "Does it work when put together?" Electromagnetic, Thermal, Low Power, Computational Fluid Dynamics Optimized **flows** to **enable Al/ML** chips and systems

Systems

Boa

IP and Su

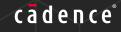

## ML in Electronic Design Automation

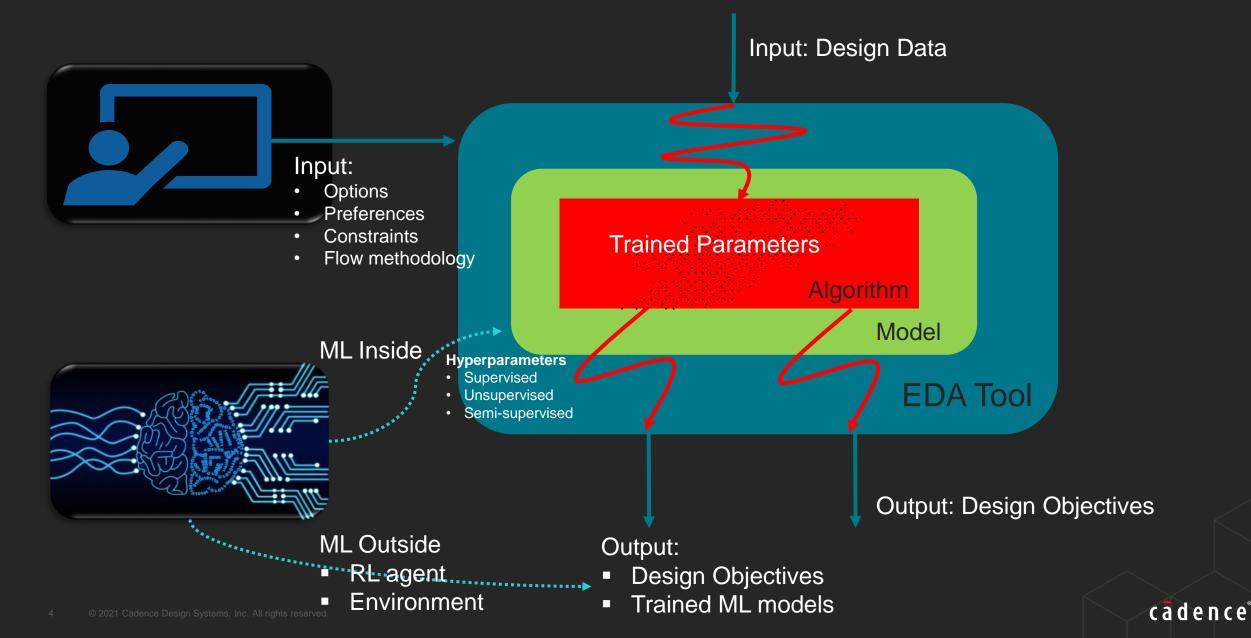

## ML Inside: Enhanced Delay Prediction

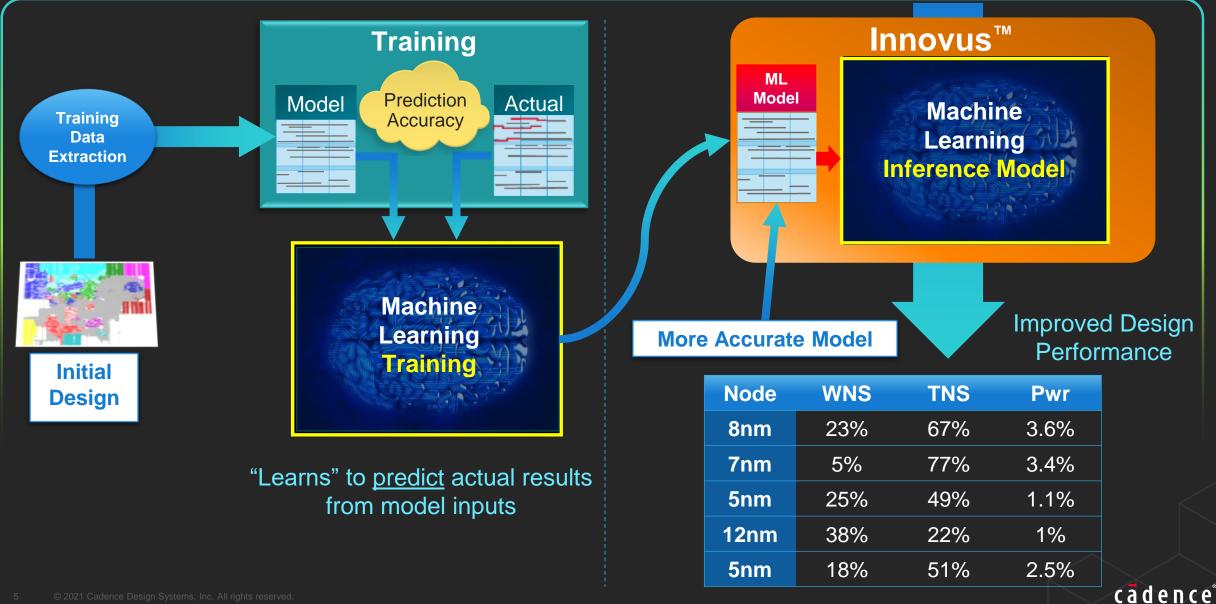

## ML Outside Objective: Improve the PPA/Productivity Curve

Engineering Effort

#### 6 © 2021 Cadence Design Systems, Inc. All rights reserved

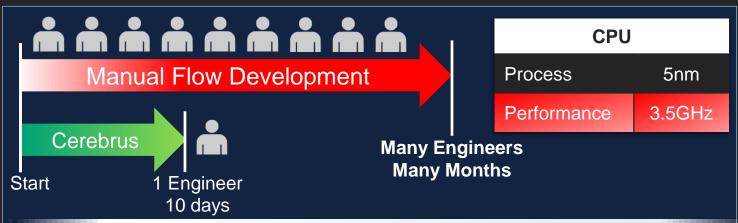

## Cadence Cerebrus: ML for Better PPA and Full Flow Productivity

#### Cadence Cerebrus<sup>™</sup> Flow Design Input (Spec) Genus™ **RTL Synthesis** Knowledge Reinforcement Learning Graph Innovus™ Implementation $\nabla \times \frac{1}{\alpha} \nabla + j \sigma B - \omega^2 \varepsilon B = -j j$ **System** X(t) = f X , u t $X(t) = \frac{\partial f}{\partial t} X + \frac{\partial f}{\partial t} u$ Tempus™ **Signoff STA** Machine Learning-**Driven Flow Automation** Result **Optimized PPA**

Cerebrus automatically improved PPA of 5nm mobile CPU, using 30 parallel jobs Within 10 days, converged on improved flow

### **Cerebrus Improvements vs Baseline**

| Parameter     | Improvement | Percent |

|---------------|-------------|---------|

| Performance   | 420MHz      | 14%     |

| Leakage power | 26mW        | 7%      |

| Total power   | 62mW        | 3%      |

| Density       |             | 5%      |

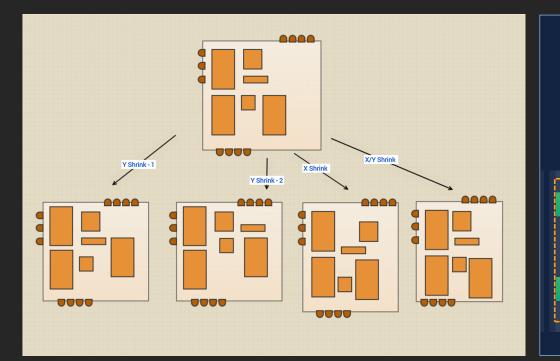

## Cadence Cerebrus: ML for Automated Floorplan Optimization

|                                                                      | Design – CPU Core |      |  |

|----------------------------------------------------------------------|-------------------|------|--|

|                                                                      | Process           | 12nm |  |

|                                                                      | Performance       | 2GHz |  |

|                                                                      |                   |      |  |

| Customer wanted to achieve 2GHz<br>on latest CPU implementation      |                   |      |  |

| Cerebrus optimized floorplan and<br>implementation flow concurrently |                   |      |  |

- Floorplan can be automatically resized in any direction

- Innovus<sup>™</sup> mixed placer used to find optimal macro location in resized floorplan

### **Cerebrus Improvements vs Baseline**

| Parameter            | Improvement |

|----------------------|-------------|

| Performance          | +200MHz     |

| Total failing timing | 83%         |

| Leakage power        | 17%         |

## cādence°

#### RENESAS

To efficiently maximize the performance of new products that use emerging process nodes, digital implementation flows used by our engineering team need to be continuously updated. **Automated design flow optimization is critical for realizing product development at a much higher throughput.** Cerebrus, with its innovative ML capabilities, and the Cadence RTL-to-signoff tools have provided automated flow optimization and floorplan exploration, improving design performance by more than 10%. Following this success, the new approach will be adopted in the development of our latest design projects.

Satoshi Shibatani, director, Digital Design Technology Department, Shared R&D EDA Division, Renesas

## Summary

## AI/ML Productivity Improvements - Some Examples

**Functional Verification**

**Digital Implementation**

**Library Characterization**

**Custom IC Implementation**

**Design for Manufacturing**

**PCB** Synthesis

**System Design and Analysis**

Up to **5X reduction in simulation cycles (**same coverage) Up to **4X** (2X avg.) **better out-of-the-box proofs**

Up 20% better PPA, up to 10X productivity

Accelerated library development Example: 47% of libs interpolated 98%+ pass rate

Accurate **response surface model** of the device or block Layout group prediction

> Hotspot prediction In-design detection and fixing

> > Faster design closure Routability

**Reduction in simulation time**

# cadence®

© 2021 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <a href="https://www.cadence.com/go/trademarks">https://www.cadence.com/go/trademarks</a> are trademarks or registered trademarks of Cadence logo, and the other Cadence marks found at <a href="https://www.cadence.com/go/trademarks">https://www.cadence.com/go/trademarks</a> are trademarks or registered trademarks of Cadence logo, and the other Cadence marks found at <a href="https://www.cadence.com/go/trademarks">https://www.cadence.com/go/trademarks</a> are trademarks of Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All MIPI specifications are registered trademarks or trademarks of PCI-SIG. All other trademarks are the property of their respective owners.