## A 1.2nJ/Classification Fully Synthesized All-Digital Asynchronous Wired-Logic Processor Using Quantized Non-linear Function Blocks in 0.18µm CMOS

Department of Electrical Engineering and Information System, The University of Tokyo

<u>Rei Sumikawa</u>, Kota Shiba, Atsutake Kosuge, Mototsugu Hamada, Tadahiro Kuroda

Rei Sumikawa (1/6)

### **Reduction of Energy Consumption of DNN Chip**

- Challenge of DNN chip is large energy consumption

- Wired-logic architecture saves energy by eliminating memory accesses

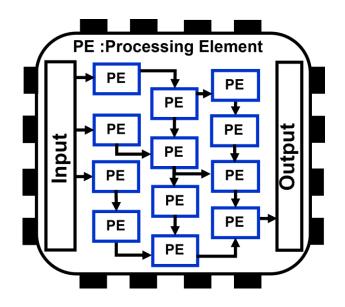

Implement plenty of processing elements

Chip size is an issue for wired-logic architecture

To implement in 1 chip

- •Reduction of the number of PE

- Improvement of area efficiency of PE

**Both are required!**

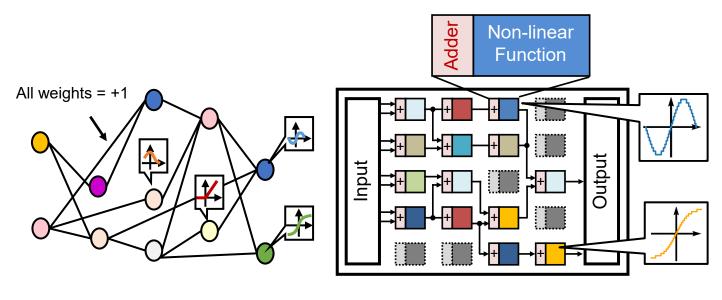

- NNN reduces the number of neurons and synapses

Activation function is optimized for each neuron

- Most hardware is used in non-linear function blocks

Minimization of this part is important

**Overview of NNN**

Wired-logic NNN chip

#### **Logically Compressed Non-Linear Function Blocks**

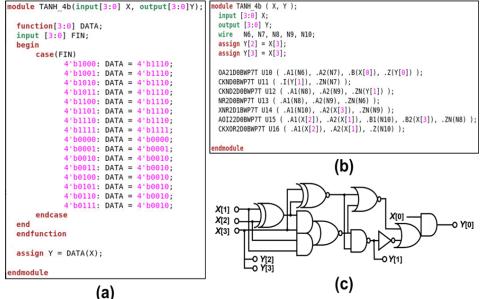

- Non-linear functions are coarsely quantized

Degradation of accuracy by quantization is small

- 8b functions are described by HDL and synthesized

Realized blocks with minimum amount of digital circuits

#### **Circuit area of Tanh function**

|            | LUT(SRAM) | LC-NLF(8b) |

|------------|-----------|------------|

| Area (µm²) | >10,000   | 717.8      |

| FoM        | 1         | 1/13.9     |

HDL of Tanh function (a) before synthesis, (b) after synthesis and its (c) schematic

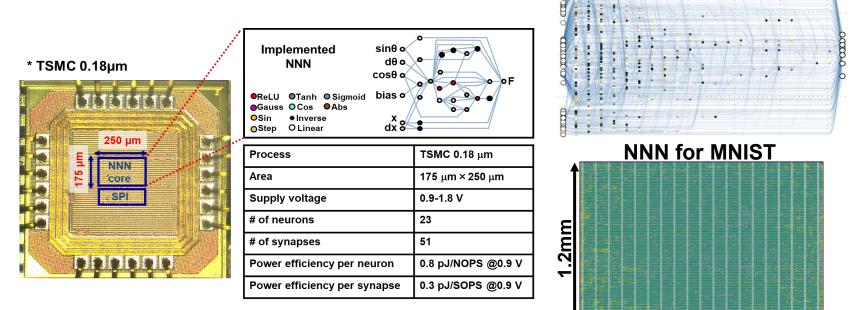

- Prototyped the proposed wired-logic processor

- Estimated energy consumption of MNIST task by scaleup simulation

- Predicted 1.2 nJ/classification, 2.6x improvement compared with ReRAM based wired-logic CiM chip

**Prototyped Chip**

# Please come and listen to my poster presentation!

Rei Sumikawa (6/6)