# FormalFuzzer: Formal Verification Assisted Fuzz Testing for SoC Vulnerability Detection

#### ASP-DAC 2024

Nusrat Farzana Dipu, Muhammad Monir Hossain Kimia Zamiri Azar, Farimah Farahmandi, and <u>Mark Tehranipoor</u>

University of Florida, USA Florida Institute for Cybersecurity Research Department of Electrical and Computer Engineering

### Outline

- Background

- Proposed Framework

- Framework Implementation

- Experimental Setup

- Result Analysis

- Conclusion and Future Work

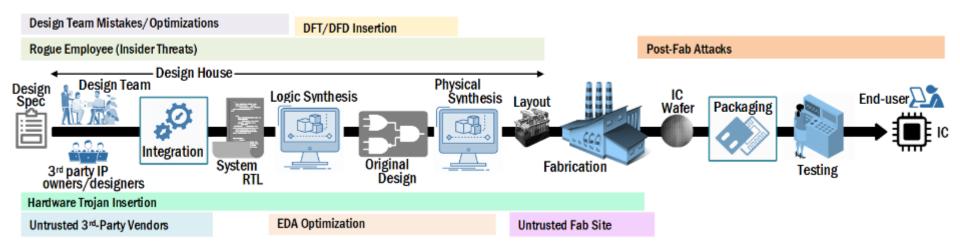

## Background: Security & Trust Issues in SoC Design Cycle

- Diversified sources of security vulnerabilities in SoC design life-cycle

- Attacker's Goal: To extract/get access to the security assets

- Attackers utilize underlying security vul.  $\rightarrow$  security asset leakage

- Security assets leakage → Critically compromised security of SoC applications

Potential sources of security vulnerabilities in modern SoC design flow

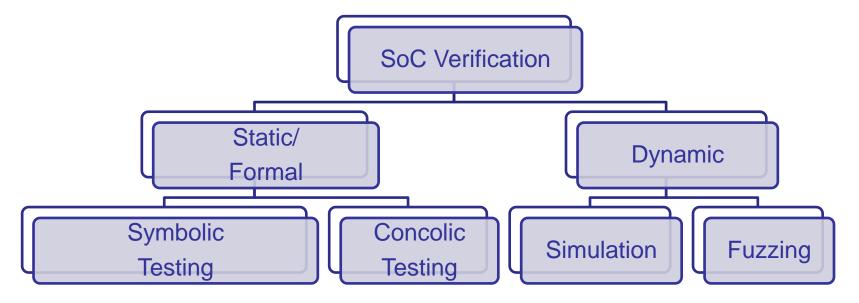

# **Existing SoC Verification Approaches**

#### Static/Formal Verification

- Check design meets requirements by inspecting the code before it run.

- Verify properties consistency with design constraints and specs.

#### Dynamic Verification

- Performed during the execution of the program

- Run-time checks of malicious program behavior/asset leakage

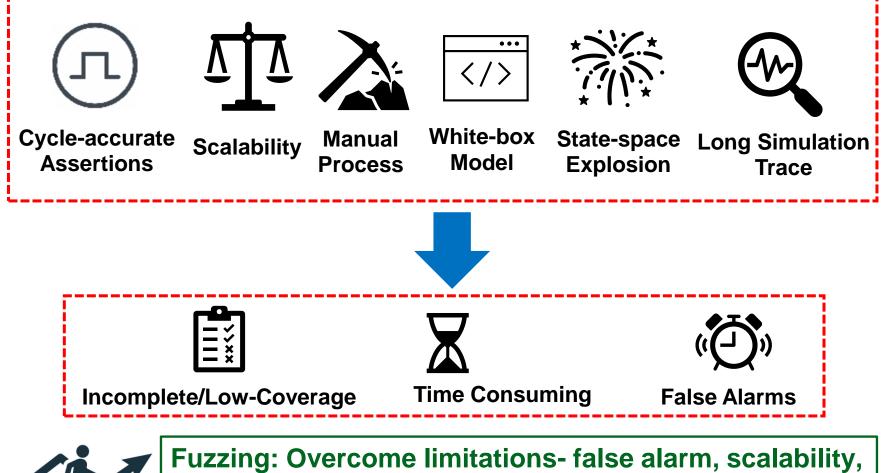

# Challenges in Existing Verification Approaches

white-box design requirement, automation!

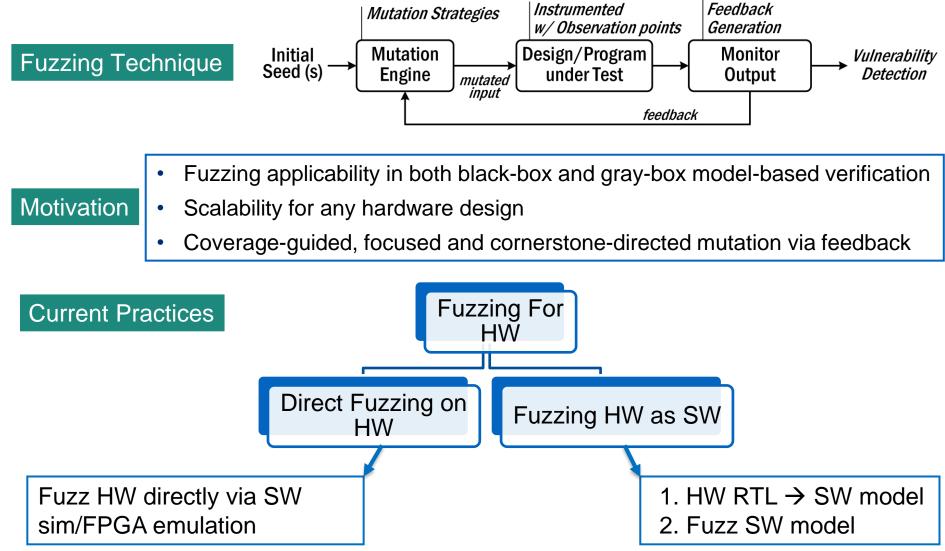

# **Fuzzing for SoC Verification**

# **Challenges in Current Fuzzing Practices**

Reliance on traditional SW-based code coverage (lacking map to HW design)

More randomness in mutations and increased input space (irrelevant to DUT)

Lacking security driven mutation and dynamic feedback

Mostly applicable to white-box (full access to the design) model

Proposed Framework to mitigate existing challenges in SoC Verification!

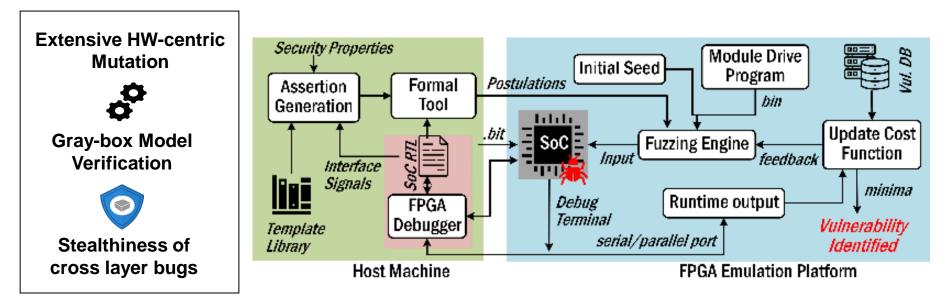

## Proposed Fuzzing Framework: FormalFuzzer

#### FormalFuzzer?

SoC Security Verification using Formal assisted Fuzzing

- Automated framework assisted by formal verification for SoC security verification

- Leverage property-driven formal verification for reducing input space significantly for Fuzzer

- Leverage counter-example/cover traces generated by formal tool for deriving postulation to identify cross layer bugs

- Utilizing cost function and feedback for runtime update of mutation strategies

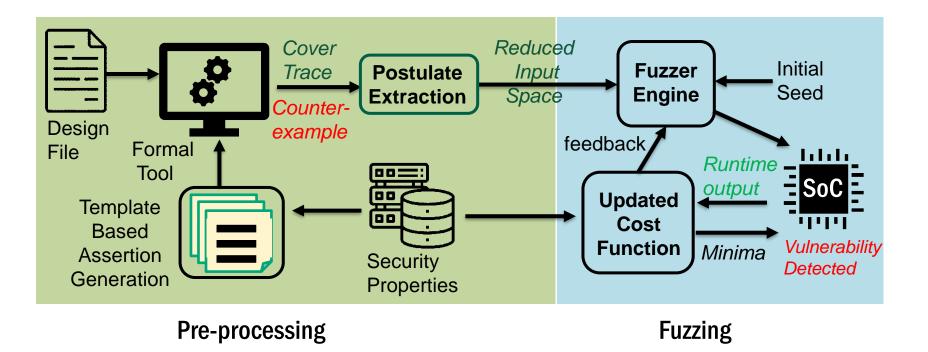

# Formal Verification Assisted Preprocessing

- Property-driven formal verification is used for pre-processing to generate postulates

- **Objective:** To reduce input space for the fuzzer engine

- To generate HW-centric test patterns for SoC vulnerability detection

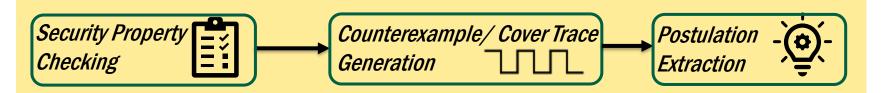

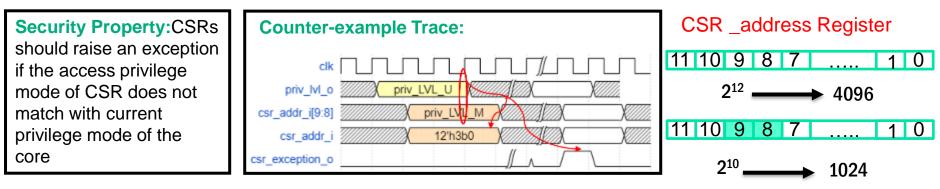

## Postulate Extraction from Formal Verification

- **Postulation:** A set of constraints for effective test generation

- Guides the fuzzer engine in tuning the mutation strategy

#### **Example**

**Postulation:** Fix 9<sup>th</sup> and 8<sup>th</sup> bit

Reduced input space (RIS) =  $\frac{(4096 - 1024)}{4096}$  = 75%

csr\_address[9:8] = 2'b11=Machine mode

10

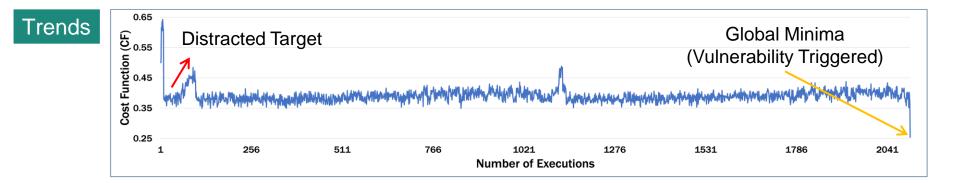

## **FormalFuzzer** Cost Function

- Objective: guides fuzzing to generate smarter-than-random test inputs

- Evaluate run-time fuzzing performance and security properties

- Evaluate the quality of mutated inputs

- Estimate the chances of hitting a potential malicious behavior

- Fuzzing objective: minimizing cost function (global minima → vulnerability triggered)

- $\downarrow$  Cost Function  $\rightarrow$  better fuzzing  $\rightarrow$  faster vulnerability trigger (global minima)

Mathematical Formula

$$F_{c} = 1 - \frac{1}{n} \left[ \left\{ 1 - \frac{2}{r(r-1)} \sum_{j=1}^{r-1} \sum_{k=j+1}^{r} \frac{h(i_{j}, i_{k})}{l_{i}} \right\} + \frac{u_{i}}{2^{N-d}} + \frac{\sigma}{\sum_{j=1}^{z} l_{z}} \sum_{k=1}^{z} (h(o_{r-1,k}, o_{r,k})) + \frac{1}{m} \sum_{k=1}^{m} (o_{r,k} == o_{t,k}) \right]$$

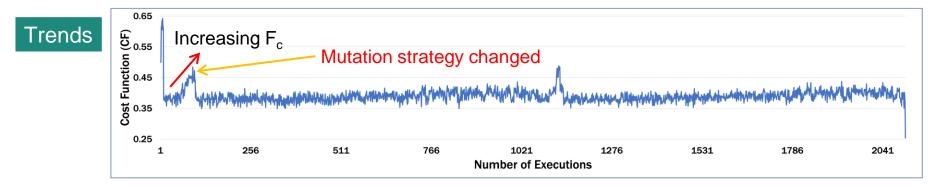

### FormalFuzzer Feedback

- Cost function improvement rate (CFIR) evaluates runtime performance of fuzzing

- Positive CFIR → better fuzzing by mutating smart inputs → global minima

- Continue mutation w/ the same mutation strategy

- Negative CFIR → Mutation against objective → increasing cost function

- Change the mutation strategy

- Objective: keep CFIR always high positive

- CFIR estimated after each frequency of feedback evaluation  $(f_f)$  iterations

Mathematical Formula

$$CFIR = -\frac{\delta F_c}{\delta r} = -\frac{F_{c2} - F_{c1}}{r_2 - r_1}$$

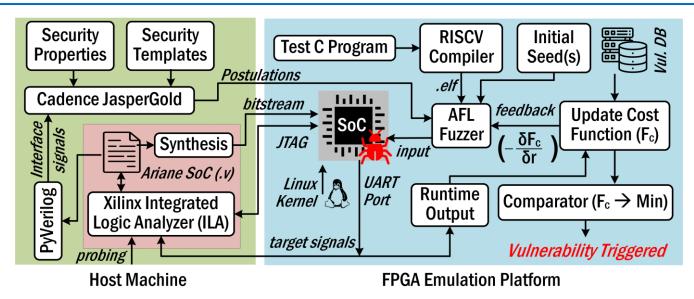

## FormalFuzzer Implementation

- SoC: RISC-V-based 64-bit Ariane SoC

- HW debugging: Xilinx Integrated Logic Analyzer (ILA)

- Pre-processing: PyVerilog, Cadence JasperGold (Jasper)

- Emulation: Genesys 2 Kintex-7 FPGA Development Board

- Linux kernel mounted on SoC via SD card on FPGA board

- American Fuzzy Lob (AFL) instrumented for-

- Utilizing postulations to mutate from targeted input space

- Computing F<sub>c</sub>, CFIR and utilize feedback to change the mutation technique

### **Experimental Setup**

#### Vulnerabilities in Ariane SoCs

| Index | Vulnerability                                                     | Location             | Triggering Condition               | Reference     |

|-------|-------------------------------------------------------------------|----------------------|------------------------------------|---------------|

| SV1   | Access to <i>mstatus</i> CSR from<br>lower privilege level        | CPU (dec)            | Unauthorized read to CSR           | CWE-1262      |

| SV2   | Allow executing <i>mret</i> machine-<br>level ins. from user-mode | CPU (dec)            | Unauthorized instruction execution | CWE-1242      |

| SV3   | Incorrect logic to decode<br>FENCE.I ins.                         | CPU (dec)            | imm ≠ 0 & rs1 ≠ 0                  | CWE-440       |

| SV4   | Leaking AES key through SoC<br>common bus (ciphertext)            | Encryption<br>Module | Specific Plaintext                 | CVE-2018-8922 |

| SV5   | A Trojan delays cipher conversion in the AES module               | Encryption<br>Module | Specific Plaintext                 | AES-T500      |

| SV6   | Unauthorized memory access<br>via MMU                             | CPU(LSU)             | Illegal memory access              | CWE-269       |

### **Result Analysis**

#### Reduced Input Space (RIS) for Fuzzing in Ariane SoCs

| Index/<br>Module       | Security Property                                                                                                                                                                                                                                                       | Assertion                                                                                                                  | Postulation                                                                                                      | RIS    |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------|

| SM1/<br>CSR file       | SP11: CSRs should raise an exception if the access privilege mode of CSR does not match with current privilege mode of the core;                                                                                                                                        | <pre>SA11: (csr addr i[9 : 8]! = priv lvl o → ##[1 : \$](csr exception o.valid == 1′b1);</pre>                             | P11: User's privilege<br>escalation to Machine-<br>mode CSRs;                                                    | 65-73% |

|                        | <b>SP12</b> : CSRs should raise an exception if a wrong access request is made to CSRs                                                                                                                                                                                  | SA12: (csr addr i[11 : 10]! = csr op i)<br> →<br>##[1 : \$](csr exception o.valid == 1′b1                                  | P12: Write request to<br>readonly CSRs                                                                           |        |

| SM2/<br>CPU<br>decoder | SP21: If privilege level changes, the corresponding instruction should also change to avoid an instruction specified for one privilege level, to be executed in another privilege level                                                                                 | SA21: ~ \$stable(priv lvl i)  →<br>##[1 : \$] ~ \$stable(instr o)                                                          | P21: Machine-level<br>instruction from user<br>mode;<br>P22: Mutate specific bits<br>(31:7) of instruction field | 21%    |

| SM3/<br>AES            | <ul> <li>SP31: Encryption key should not be leaked through cipher text output port;</li> <li>SP32: After receiving plain text and encryption key as inputs, the encryption result should be available at the output after a specified number of clock cycles</li> </ul> | <pre>SA31: encryption key! =encryption</pre>                                                                               | P31: Check (mutate) first<br>byte of plain text                                                                  | 93%    |

| SM4/<br>MMU            | SP41: MMU should raise an exception when<br>physical<br>memory access is operated in U/S mode                                                                                                                                                                           | SA41: (priv lvl i! = P RIV LV L M)&&<br>(icache areq i.fetch req == 1'b1)<br> → (icache areq o.fetch exception ==<br>1'b1) | P41: Access physical<br>memory in user mode                                                                      | 50%    |

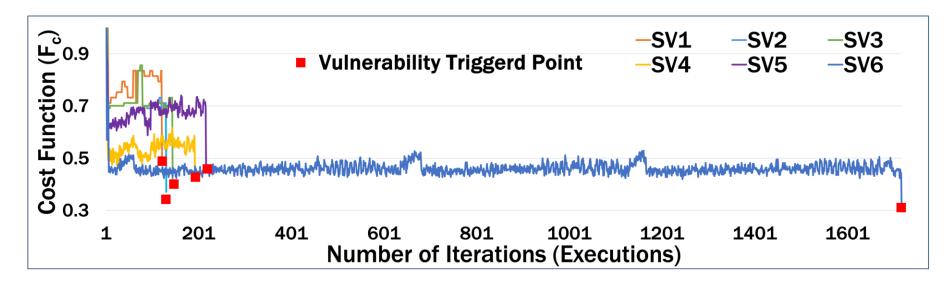

### **Results Analysis**

Identification of known vulnerabilities by analyzing cost function and feedback

#### Cost function of detected known vulnerabilities by FormalFuzzer

#### **Results Analysis**

FormalFuzzer also detected few unknown vulnerabilities in the Ariane SoC

| Index | Vulnerability                                         | Location             | Triggering Condition | Reference |

|-------|-------------------------------------------------------|----------------------|----------------------|-----------|

| UV1   | Retrieve last ciphertext in AES module (Trojan)       | Encryption<br>Module | Specific plaintext   | CWE-401   |

| UV2   | CSR read access to undefined<br>HPC                   | CSR file             | No exception         | CWE1281   |

| UV3   | UV3 No exception raised for<br>illegal format of MULH | CPU (dec)            | rd ∈ {rs1, rs2}      | CWE1262   |

## **Results Analysis**

#### Summary Results: Vulnerability Detection

Save 55% of verification time compared to system w/o proposed pre-processing and feedback

Save 19% compared to SoCFuzzer lacking proposed pre-processing

| Index | Freq. of                                 | No. of Executions (Avg) |                        |              | Speed Up |        |  |

|-------|------------------------------------------|-------------------------|------------------------|--------------|----------|--------|--|

|       | Feedback<br>Evaluation (f <sub>f</sub> ) | F <sub>NPNF</sub>       | SoCFuzzer <sup>1</sup> | FormalFuzzer | S1       | S2     |  |

| SV1   | 6                                        | 868                     | 541                    | 201          | 76.84%   | 62.85% |  |

| SV2   | 5                                        | 421                     | 165                    | 133          | 68.41%   | 19.39% |  |

| SV3   | 5                                        | 361                     | 208                    | 161          | 55.90%   | 22.60% |  |

| SV4   | 5                                        | 15254                   | 6687                   | 187          | 98.77%   | 97.2%  |  |

| SV5   | 5                                        | 12896                   | 5210                   | 204          | 98.42%   | 96.08% |  |

| SV6   | 6                                        | 5331                    | 2592                   | 1937         | 63.67%   | 25.27% |  |

| UV1   | 5                                        | N/A                     | N/A                    | 7389         | N/A      | N/A    |  |

| UV2   | 6                                        | N/A                     | N/A                    | 758          | N/A      | N/A    |  |

| UV3   | 5                                        | N/A                     | N/A                    | 737          | N/A      | N/A    |  |

F<sub>NPNF</sub>: Fuzzing w/o proposed pre-processing and cost-function-based feedback. S1: FormalFuzzer speedup w.r.t. F<sub>NPNF</sub> and S2: Speedup w.r.t. SoCFuzzer.

#### Reference

[1] Hossain, Muhammad Monir, Arash Vafaei, Kimia Zamiri Azar, Fahim Rahman, Farimah Farahmandi, and Mark Tehranipoor. "SoCFuzzer: SoC Vulnerability Detection using Cost Function enabled Fuzz Testing." In 2023 Design, Automation & Test in Europe Conference & Exhibition (DATE), pp. 1-6. IEEE, 2023.

# **Comparison w/ HW Fuzzing Approaches**

- FormalFuzzer's strengths →

- Independence from golden model and white-box model

- Formal assisted pre-processing reducing input space and target oriented fuzzing

| Framework                     | Target<br>Design | Approach | Feedback/Coverage | Automation | Gray-<br>box | Golden<br>Model |

|-------------------------------|------------------|----------|-------------------|------------|--------------|-----------------|

| HyPFuzz <sup>1</sup>          | CPU              | HDL Sim  | Branch            | No         | No           | Yes             |

| TheHuzz <sup>2</sup>          | CPU              | HDL Sim  | FSM, Statement    | No         | No           | Yes             |

| HyperFuzzing <sup>3</sup>     | SoC              | SW Sim   | NoC, Bitflip      | No         | Yes          | Yes             |

| DifuzztRTL <sup>4</sup>       | CPU              | FPGA Emu | Control-register  | No         | No           | Yes             |

| RFUZZ <sup>5</sup>            | IP               | FPGA Emu | MUX               | No         | No           | Yes             |

| Fuzzing HW as SW <sup>6</sup> | SoC              | SW Sim   | Branch/Code       | Yes        | No           | Yes             |

| FormalFuzzer                  | SoC              | FPGA Emu | Cost Function     | Yes        | Yes          | No              |

#### References

[1] Chen, Chen, et al. "HyPFuzz: Formal-Assisted Processor Fuzzing." arXiv preprint arXiv:2304.02485 (2023).

[2] R. Kande et al., "Thehuzz: Instruction fuzzing of processors using golden-reference models for finding software-exploitable vulnerabilities," USENIX, 2022.

[3] S. K. Muduli et al., "Hyperfuzzing for soc security validation," in International Conference on CAD (ICCAD), 2020, pp. 1–9.

[4] S. Canakci et al., "Directfuzz: Automated test generation for rtl designs using directed graybox fuzzing," in DAC, 2021, pp. 529–534.

[5] K. Laeufer et al., "Rfuzz: Coverage-directed fuzz testing of rtl on fpgas," in International Conference on CAD (ICCAD), 2018, pp. 1–8.

[6] T. Trippel et al., "Fuzzing hardware like software," in 31st USENIX Security Symposium (USENIX Security 22), 2022, pp. 3237–3254.

# **Conclusion and Future Work**

#### Conclusion

- Developed FormalFuzzer, a fuzzing framework for SoC security verification

- Integrated formal verification strategies for reducing input space and efficient mutation

- Utilized cost function concept targeting vul. and develop feedback for smart mutation

- Experiments proved FormalFuzzer's capability in detecting vul. within reasonable time

#### Future Works

- Integration of Artificial Intelligence (AI) in generating smart seeds and efficient mutation

- Improvement of cost function to target more unknown vulnerabilities

### **Questions?**

Contact: Dr. Nusrat Farzana Dipu at <u>ndipu@ufl.edu</u> Muhammad Monir Hossain at <u>hossainm@ufl.edu</u> Dr. Mark Tehranipoor at <u>tehranipoor@ece.ufl.edu</u>