# **Towards Automated Testing of Multiplexers in Fully Programmable Valve Array Biochips**

Genggeng Liu<sup>1</sup>, **Yuqin Zeng<sup>1</sup>**, Yuhan Zhu<sup>1</sup>, Huayang Cai<sup>1</sup>, Wenzhong Guo<sup>1</sup>, Zipeng Li<sup>2</sup>, Tsung-Yi Ho<sup>3</sup>, Xing Huang<sup>4,\*</sup>

#### <sup>1</sup>Fuzhou University, China;

<sup>2</sup>Apple Inc, Cupertino, USA;

<sup>3</sup>The Chinese University of Hong Kong, Hong Kong;

<sup>4</sup>Northwestern Polytechnical University, China.

Speaker: Yuqin Zeng

Email: zengyq996@gmail.com

#### Background and Motivation

- Preliminary and Problem Formulation

- Structure of Multiplexer

- Manufacturing Defects in FPVA Biochips

- Fault Model

- Single-Fault-Type Assumption

- Problem Model

- Details of the Proposed Automated Fault Test Method

- ILP-based ATPG Algorithm

- Test Strategy

- Simulation Results

- Conclusion

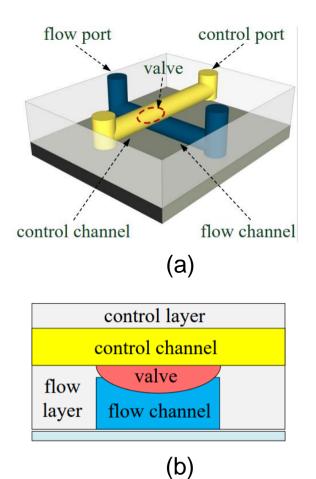

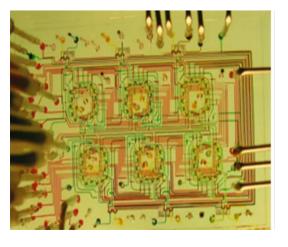

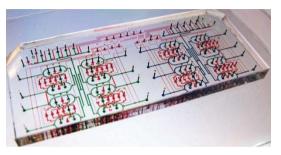

# **Continuous-Flow Microfluidic Biochips**

- Fundamental component: valves.

- Increasing integration level of valves.

(C)

# Fully Programmable Valve Array(FPVA) Biochips

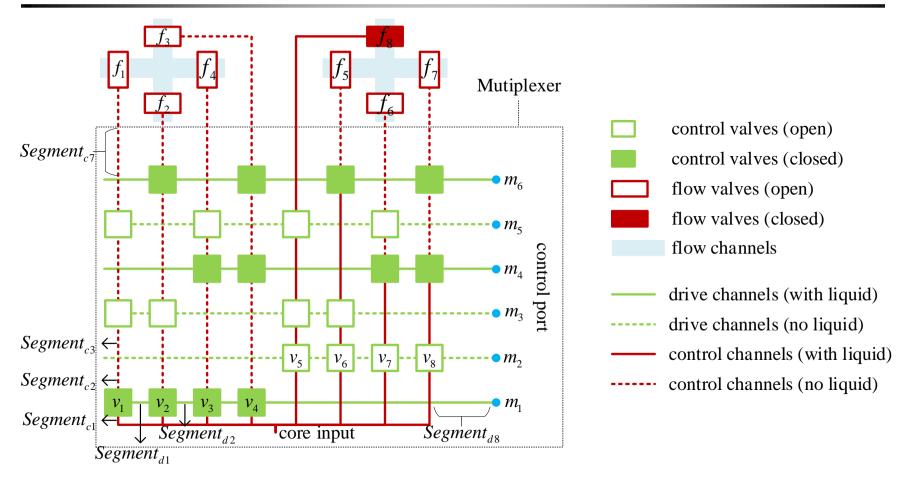

The utilization of multiplexers has bolstered valve integration within FPVA Biochips.

- Background and Motivation

- Preliminary and Problem Formulation

- Structure of Multiplexer

- Manufacturing Defects in FPVA Biochips

- Fault Model

- Single-Fault-Type Assumption

- Problem Model

- Details of the Proposed Automated Fault Test Method

- ILP-based ATPG Algorithm

- Test Strategy

- Simulation Results

- Conclusion

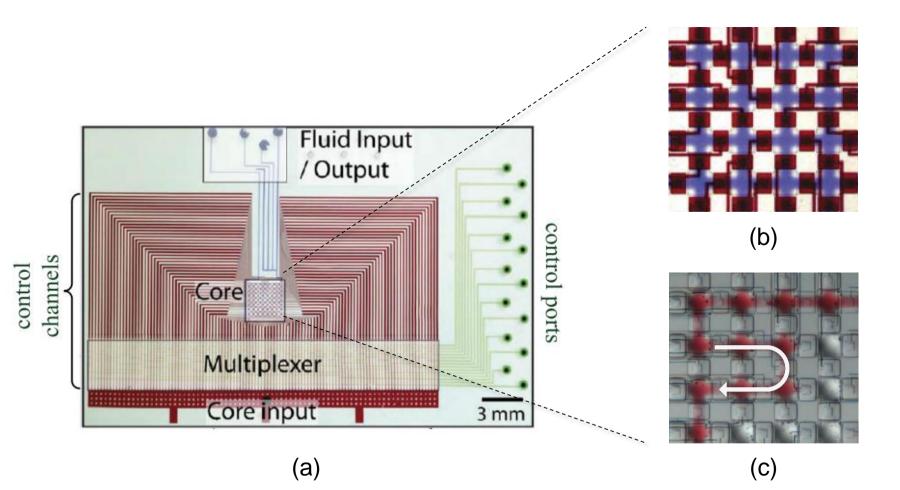

#### **Structure of Multiplexer**

- The Multiplexer's Two-Layer Structure.

- Upper Layer: The Driving Layer (Green).

- Lower Layer: The Control Layer (Red).

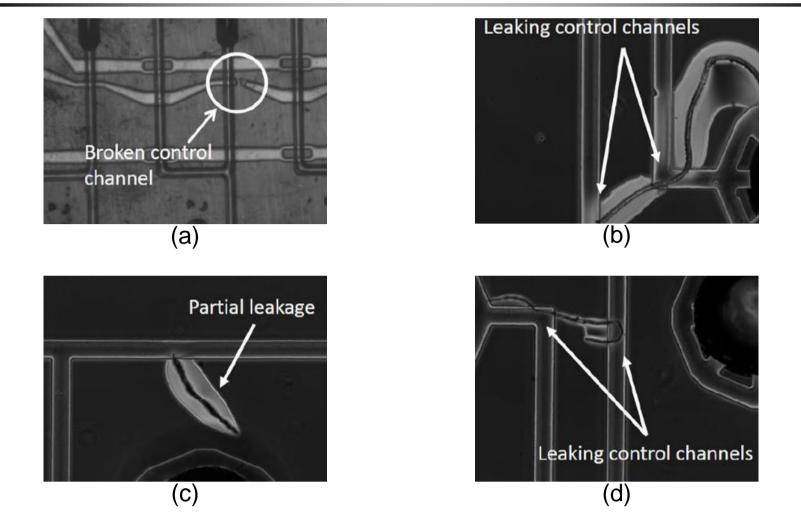

#### **Manufacturing Defects in FPVA Biochips**

Throughout the manufacturing and operational phases, FPVA biochips may experience physical defects. [*K. Hu et al., 2014*]

#### **Fault Model**

Five categories:

- Control channel blockage

- Control channel leakage

- Drive channel blockage

- Drive channel leakage

- Valve elastic degradation

Five categories:

- Control channel blockage

- Control channel leakage

- Drive channel blockage

- Drive channel leakage

- Valve elastic degradation

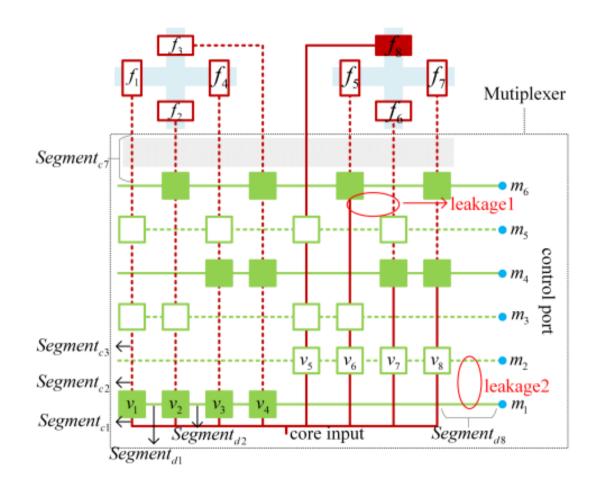

#### • Assumption:

A chip will rarely contain multiple fault types, but the same type of fault may occur multiple times in a layer.

#### • Because:

The root cause of a fault typically leads to the occurrence of the same type of fault.

Since the layers of a multiplexer are manufactured independently,

there will be no interlayer faults.

[K. Hu et al., 2015]

#### **Problem Model**

- Based on the time division concept, we divide the execution process of a test pattern into four parts: "<u>drive delay</u>", "<u>filling delay</u>", "<u>leakage</u> <u>delay</u>" and "<u>refresh delay</u>".

- **Given:** The structure of a multiplexer.

- **Output:** A set of test patterns.

- **Objective:** Minimizing the number of test patterns.

- Subject to: The generated test pattern combinations can cover all the possible positions of the above five types of faults in the multiplexer,

i.e., achieving 100% fault coverage.

- Background and Motivation

- Preliminary and Problem Formulation

- Structure of Multiplexer

- Manufacturing Defects in FPVA Biochips

- Fault Model

- Single-Fault-Type Assumption

- Problem Model

#### Details of the Proposed Automated Fault Test Method

- ILP-based ATPG Algorithm

- Test Strategy

- Simulation Results

- Conclusion

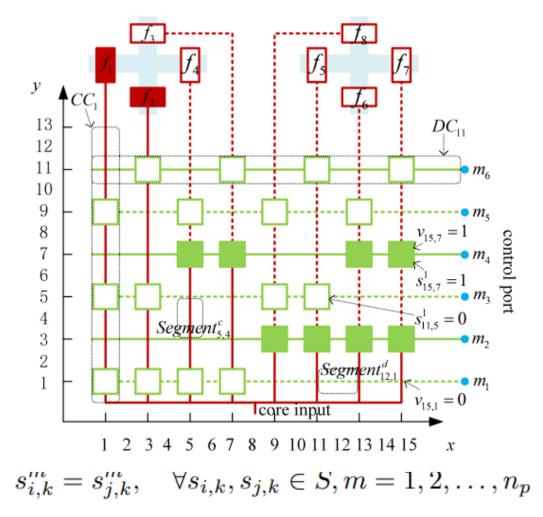

# **ILP-based ATPG Algorithm**

- Formulate Integer Linear Programming(ILP) models for the five types of faults mentioned above.

- To achieve 100% fault coverage, we must ensure that  $n_p$  test patterns can cover each potential fault location at least once.

$$\sum_{m=1}^{n_p} bd_j^m \ge 1, j \in C_d \qquad \qquad \sum_{m=1}^{n_p} lc_{i,j}^m \ge 1, (i,j) \in G_c$$

$$\sum_{m=1}^{n_p} ld_j^m \ge 1, j \in G_d \qquad \qquad \sum_{m=1}^{n_p} ec_{i,j}^m \ge 1, (i,j) \in V$$

$$\sum_{m=1}^{n_p} bc_i^m \ge 1, i \in C_c$$

$n_{-}$

• The proposed ILP model aims to identify a test pattern combination with the minimal quantity.

$$minimize\sum_{m=1}^{n_p} p_m$$

- For example:

- Test patterns generation.

# **Test Strategy**

We divide the execution process of a test pattern into four steps during the test process of the multiplexer.

•Step1: Inject colorless gas and close corresponding control valves.

•Step2: Inject ample colored gas into control channels and close the core input to contain the gas within those channels.

•Step3: Maintain closed control ports and core input to enable complete gas leakage to the external environment over time.

•Step4: Open control ports and core input to release channel gas. Replace colored gas with colorless in control channels to avoid impacting next test execution.

- Background and Motivation

- Preliminary and Problem Formulation

- Structure of Multiplexer

- Manufacturing Defects in FPVA Biochips

- Fault Model

- Single-Fault-Type Assumption

- Problem Model

- Details of the Proposed Automated Fault Test Method

- ILP-based ATPG Algorithm

- Test Strategy

- Simulation Results

- Conclusion

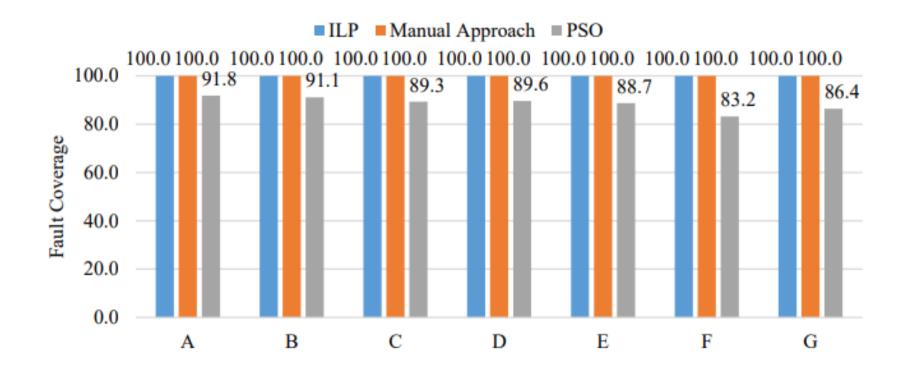

### **Simulation Results**

| Multiplexer |       |       |       |       | ILP   |        |       | Manual Method |       | Imp(%) |       | PSO   |       | Imp(%)  |  |

|-------------|-------|-------|-------|-------|-------|--------|-------|---------------|-------|--------|-------|-------|-------|---------|--|

| Bench       | $n^v$ | $n^d$ | $n^c$ | $n^p$ | $n^t$ | t(s)   | $n^t$ | t(s)          | $n^t$ | t      | $n^t$ | t(s)  | $n^t$ | t       |  |

| Α           | 24    | 6     | 8     | 6     | 5     | 2.1    | 8     | -             | 37.5  | -      | 5     | 19.2  | 0.0   | 89.2    |  |

| в           | 36    | 8     | 9     | 8     | 7     | 7.7    | 9     | -             | 22.2  | -      | 8     | 40.6  | 12.5  | 81.0    |  |

| С           | 64    | 8     | 9     | 8     | 7     | 17.3   | 16    | -             | 56.3  | -      | 10    | 63.8  | 30.0  | 72.9    |  |

| D           | 105   | 10    | 21    | 10    | 8     | 142.6  | 21    | -             | 61.9  | -      | 17    | 93.1  | 52.9  | -53.3   |  |

| E           | 160   | 10    | 32    | 16    | 9     | 1800.0 | 32    | -             | 71.9  | -      | 19    | 128.4 | 52.6  | -1301.5 |  |

| F           | 246   | 12    | 41    | 20    | 12    | 1800.0 | 41    | -             | 70.7  | -      | 21    | 178.7 | 42.9  | -907.0  |  |

| G           | 384   | 12    | 64    | 32    | 20    | 1800.0 | 64    | -             | 68.8  | -      | 41    | 181.6 | 51.2  | -891.2  |  |

#### Comparison results of execution time and number of test patterns.

- *n<sup>v</sup>*: The number of control valves;

- *n<sup>d</sup>*: The number of drive channels;

- *n<sup>c</sup>*: The number of control channels;

- *n<sup>c</sup>*: The number of control channels;

- *n*<sup>*p*</sup>: A constant, used to limit the maximum number of test patterns;

- *n*<sup>t</sup>: The number of test patterns generated by the algorithm;

- *t* : The time used to generate test patterns;

- - : Time is difficult to estimate.

Comparison results of fault coverage.

- Background and Motivation

- Preliminary and Problem Formulation

- Structure of Multiplexer

- Manufacturing Defects in FPVA Biochips

- Fault Model

- Single-Fault-Type Assumption

- Problem Model

- Details of the Proposed Automated Fault Test Method

- ILP-based ATPG Algorithm

- Test Strategy

- Simulation Results

- Conclusion

# Conclusion

- We propose an ILP-based automated test pattern generation(ATPG) algorithm.

- We propose an automatic testing strategy for multiplexers.

- The proposed ILP-based algorithm can generate fewer test patterns in a reasonable time and achieve 100% fault coverage.

#### Thank you for your attention!